Команда векторного типа на поле галуа перемножения, суммирования и накопления

Иллюстрации

Показать всеИзобретение относится к компьютерной технике и, в частности, к векторной обработке в вычислительной среде. Технический результат заключается в повышении эффективности вычислений на поле Галуа. Технический результат достигается за счет получения процессором для исполнения машинной команды, содержащей поле кода операции для предоставления кода операции, идентифицирующего операцию векторного типа на поле Галуа перемножения, суммирования и накопления, поле первого регистра, используемое для обозначения первого регистра, содержащего первый операнд, поле второго регистра, используемое для обозначения второго регистра, содержащего второй операнд, поле третьего регистра, используемое для обозначения третьего регистра, содержащего третий операнд, поле четвертого регистра, используемое для обозначения четвертого регистра, содержащего четвертый операнд. 3 н. и 17 з.п. ф-лы, 32 ил.

Реферат

Предпосылки создания изобретения

[0001] Один или несколько аспектов изобретения относятся в общем к обработке в вычислительной среде, в частности, к векторной обработке в такой среде.

[0002] Обработка в вычислительной среде включает управление работой одного или нескольких центральных процессорных устройств (ЦПУ). Обычно действие ЦПУ управляется командами, хранящимися запоминающем устройстве Команды могут иметь различный формат и часто указывают регистры, используемые при выполнении различных операций.

[0003] В зависимости от архитектуры ЦПУ могут использоваться различные типы регистров, в том числе, например, регистры общего назначения, регистры специального назначения, регистры с плавающей запятой и/или векторные регистры. С различными типами команд могут использоваться различные типы регистров. Например, регистры с плавающей запятой хранят числа с плавающей запятой, используемые командами с плавающей запятой, векторные регистры содержат данные для векторной обработки, выполняемой командами типа "одиночный поток команд, множественный поток данных" (англ.: Single Instruction, Multiple Data, сокращенно SIMD), в том числе командами векторного типа.

Раскрытие изобретения

[0004] Для устранения недостатков уровня техники предложен машиночитаемый носитель данных (машиночитаемая среда хранения данных), в котором хранятся машинные команды, исполняемые схемой обработки для осуществления способа. Указанный способ включает, например: получение процессором для исполнения машинной команды, которая определена для исполнения компьютером в соответствии с архитектурой компьютера и содержит: по меньшей мере одно поле кода операции для предоставления кода операции, идентифицирующего операцию векторного типа на поле Галуа перемножения, суммирования и накопления; поле первого регистра, используемое для обозначения первого регистра, содержащего первый операнд; поле второго регистра, используемое для обозначения векторного регистра, содержащего второй операнд; поле третьего регистра, используемое для обозначения третьего регистра, содержащего третий операнд; поле четвертого регистра, используемое для обозначения четвертого регистра, содержащего четвертый операнд; и исполнение машинной команды, включающее: перемножение одного или нескольких элементов второго операнда с одним или несколькими элементами третьего операнда с использованием умножения без переноса для получения набора произведений; выполнение первой математической операции над указанным набором произведений для получения первого результата; выполнение второй математической операции над первым результатом и одним или несколькими выбранными элементами четвертого операнда для получения второго результата; и помещение второго результата в первый операнд.

[0005] В настоящей заявке также описываются и заявляются способы и системы, относящиеся к одному или нескольким аспектам изобретения. Кроме того, в настоящей заявке также описываются и могут быть заявлены сервисы (т.е. дополнительные функции), относящиеся к одному или нескольким аспектам изобретения.

[0006] С помощью способов одного или нескольких аспектов изобретения реализуются дополнительные особенности и преимущества. В данной заявке подробно описываются прочие варианты осуществления и аспекты изобретения, они рассматриваются как часть формулы изобретения. Достигаемый при осуществлении изобретения технический результат заключается в повышении эффективности вычислений на поле Галуа, а также в расширении арсенала средств и методов проведения таких вычислений.

[0007] В первом аспекте настоящего изобретения предлагается машиночитаемый носитель данных, в котором хранятся машинные команды, исполняемые схемой обработки для осуществления способа, включающего: получение процессором для исполнения машинной команды, которая определена для исполнения компьютером в соответствии с архитектурой компьютера и содержит: по меньшей мере одно поле кода операции для предоставления кода операции, идентифицирующего операцию векторного типа на поле Галуа перемножения, суммирования и накопления; поле первого регистра, используемое для обозначения первого регистра, содержащего первый операнд; поле второго регистра, используемое для обозначения второго регистра, содержащего второй операнд; поле третьего регистра, используемое для обозначения третьего регистра, содержащего третий операнд; поле четвертого регистра, используемое для обозначения четвертого регистра, содержащего четвертый операнд; и исполнение машинной команды, включающее: перемножение одного или нескольких элементов второго операнда с одним или несколькими элементами третьего операнда с использованием умножения без переноса для получения набора произведений; выполнение первой математической операции над указанным набором произведений для получения первого результата; выполнение второй математической операции над первым результатом и одним или несколькими выбранными элементами четвертого операнда для получения второго результата; и помещение второго результата в первый операнд.

[0008] В настоящем изобретении предпочтительно предлагается машиночитаемый носитель данных, в котором указанное перемножение включает умножение каждого элемента второго операнда на соответствующий элемент третьего операнда с использованием умножения без переноса с получением в результате четной-нечетной пар произведений, длина которых равна удвоенной длине элементов.

[0009] В настоящем изобретении предпочтительно предлагается машиночитаемый носитель данных, в котором умножение без переноса имеет порядок два.

[0010] В настоящем изобретении предпочтительно предлагается машиночитаемый носитель данных, в котором указанная первая математическая операция содержит операцию "исключающее ИЛИ", причем для получения указанного первого результата указанные четная-нечетная пары произведений с длиной, равной удвоенной длине элементов, добавляются друг к другу операцией "исключающее ИЛИ".

[0011] В настоящем изобретении предпочтительно предлагается машиночитаемый носитель данных, в котором указанная вторая математическая операция содержит операцию "исключающее ИЛИ", причем для получения второго результата указанный первый результат добавляется операцией "исключающее ИЛИ" к соответствующему элементу двойной длины четвертого операнда.

[0012] В настоящем изобретении предпочтительно предлагается машиночитаемый носитель данных, в котором указанное помещение включает помещение второго результата в элемент двойной длины первого операнда.

[0013] В настоящем изобретении предпочтительно предлагается машиночитаемый носитель данных, в котором машинная команда также содержит поле маски для указания длины элементов одного или нескольких из первого операнда, второго операнда, третьего операнда, четвертого операнда машинной команды.

[0014] В настоящем изобретении предпочтительно предлагается машиночитаемый носитель данных, в котором поле маски определяет длину элементов второго операнда и третьего операнда указанной машинной команды.

[0015] В настоящем изобретении предпочтительно предлагается машиночитаемый носитель данных, в котором длина элементов указанных первого операнда и четвертого операнда равна удвоенной длине элементов указанных второго операнда и третьего операнда.

[0016] В настоящем изобретении предпочтительно предлагается машиночитаемый носитель данных, в котором машинная команда также содержит поле расширения, используемое для указания одного или нескольких регистров, причем поле первого регистра объединено с первой частью поля расширения для указания первого регистра, поле второго регистра объединено со второй частью поля расширения для указания второго регистра, поле третьего регистра объединено с третьей частью поля расширения для указания третьего регистра, и поле четвертого регистра объединено с четвертой частью поля расширения для указания четвертого регистра.

[0017] В другом аспекте настоящего изобретения предлагается компьютерная система для исполнения машинной команды в центральном процессорном устройстве, содержащая запоминающее устройство и процессор, связанный с запоминающим устройством, причем компьютерная система сконфигурирована для осуществления способа, включающего: получение процессором для исполнения машинной команды, которая определена для исполнения компьютером в соответствии с архитектурой компьютера и содержит: по меньшей мере одно поле кода операции для предоставления кода операции, идентифицирующего операцию векторного типа на поле Галуа перемножения, суммирования и накопления; поле первого регистра, используемое для обозначения первого регистра, содержащего первый операнд; поле второго регистра, используемое для обозначения второго регистра, содержащего второй операнд; поле третьего регистра, используемое для обозначения третьего регистра, содержащего третий операнд; поле четвертого регистра, используемое для обозначения четвертого регистра, содержащего четвертый операнд; и исполнение машинной команды, включающее: перемножение одного или нескольких элементов второго операнда с одним или несколькими элементами третьего операнда с использованием умножения без переноса для получения набора произведений; выполнение первой математической операции над указанным набором произведений для получения первого результата; выполнение второй математической операции над первым результатом и одним или несколькими выбранными элементами четвертого операнда для получения второго результата; и помещение второго результата в первый операнд.

[0018] В настоящем изобретении предпочтительно предлагается компьютерная система, в которой указанное перемножение включает умножение каждого элемента второго операнда на соответствующий элемент третьего операнда с использованием умножения без переноса с получением в результате четной-нечетной пар произведений, длина которых равна удвоенной длине элементов.

[0019] В настоящем изобретении предпочтительно предлагается компьютерная система, в которой указанная первая математическая операция содержит операцию "исключающее ИЛИ", причем для получения указанного первого результата указанные четная-нечетная пары произведений с длиной, равной удвоенной длине элементов, добавляются друг к другу операцией "исключающее ИЛИ".

[0020] В настоящем изобретении предпочтительно предлагается компьютерная система, в которой указанная вторая математическая операция содержит операцию "исключающее ИЛИ" и в котором указанный первый результат добавляется операцией "исключающее ИЛИ" к соответствующему элементу двойной длины четвертого операнда для получения указанного второго результата.

[0021] В настоящем изобретении предпочтительно предлагается компьютерная система, в которой машинная команда также содержит поле маски для указания длины элементов одного или нескольких из первого операнда, второго операнда, третьего операнда, четвертого операнда машинной команды.

[0022] В настоящем изобретении предпочтительно предлагается компьютерная система, в которой поле маски определяет длину элементов второго операнда и третьего операнда указанной машинной команды и в которой длина элементов указанных первого операнда и четвертого операнда равна удвоенной длине элементов указанных второго операнда и третьего операнда.

[0023] В настоящем изобретении предпочтительно предлагается компьютерная система, в которой машинная команда также содержит поле расширения, используемое для указания одного или нескольких регистров, причем поле первого регистра объединено с первой частью поля расширения для указания первого регистра, поле второго регистра объединено со второй частью поля расширения для указания второго регистра, поле третьего регистра объединено с третьей частью поля расширения для указания третьего регистра, и поле четвертого регистра объединено с четвертой частью поля расширения для указания четвертого регистра.

[0024] В другом аспекте настоящего изобретения предлагается способ исполнения машинной команды в центральном процессорном устройстве, включающий: получение процессором для исполнения машинной команды, которая определена для исполнения компьютером в соответствии с архитектурой компьютера и содержит: по меньшей мере одно поле кода операции для предоставления кода операции, идентифицирующего операцию векторного типа на поле Галуа перемножения, суммирования и накопления; поле первого регистра, используемое для обозначения первого регистра, содержащего первый операнд; поле второго регистра, используемое для обозначения второго регистра, содержащего второй операнд; поле третьего регистра, используемое для обозначения третьего регистра, содержащего третий операнд; поле четвертого регистра, используемое для обозначения четвертого регистра, содержащего четвертый операнд; и исполнение машинной команды, включающее: перемножение одного или нескольких элементов второго операнда с одним или несколькими элементами третьего операнда с использованием умножения без переноса для получения набора произведений; выполнение первой математической операции над указанным набором произведений для получения первого результата; выполнение второй математической операции над первым результатом и одним или несколькими выбранными элементами четвертого операнда для получения второго результата; и помещение второго результата в первый операнд.

[0025] В настоящем изобретении предпочтительно предлагается способ, согласно которому машинная команда также содержит поле маски для указания длины элементов одного или нескольких из первого операнда, второго операнда, третьего операнда, четвертого операнда машинной команды.

[0026] В настоящем изобретении предпочтительно предлагается способ, согласно которому машинная команда также содержит поле расширения, используемое для указания одного или нескольких регистров, причем поле первого регистра объединено с первой частью поля расширения для указания первого регистра, поле второго регистра объединено со второй частью поля расширения для указания второго регистра, поле третьего регистра объединено с третьей частью поля расширения для указания третьего регистра, и поле четвертого регистра объединено с четвертой частью поля расширения для указания четвертого регистра.

Краткое описание чертежей

[0027] Настоящее изобретение может быть осуществлено множеством способов, и далее исключительно в качестве примера будут описаны варианты осуществления с использованием прилагающихся чертежей. На чертежах показано:

на фиг. 1 - схема примера вычислительной среды, в состав которой могут входить и в которой могут использоваться один или несколько аспектов изобретения,

на фиг. 2А - схема другого примера вычислительной среды, в состав которой могут входить и в которой могут использоваться один или несколько аспектов изобретения,

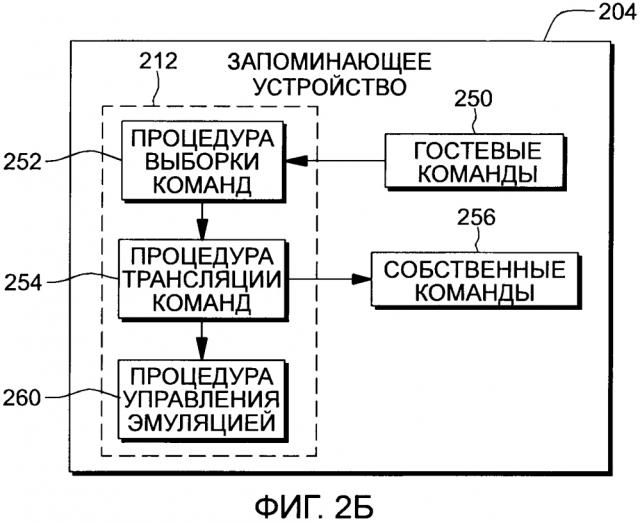

на фиг. 2Б - более детальная схема запоминающего устройства по схеме фиг. 2А,

на фиг. 3 - схема примера файла регистров,

на фиг. 4А - схема примера формата команды векторного типа

непосредственной проверки класса данных с плавающей запятой (англ.: Vector Floating Point Test Data Class Immediate),

на фиг. 4Б - пример значений двоичных разрядов третьего операнда команды векторного типа непосредственной проверки класса данных с плавающей запятой согласно фиг. 4А,

на фиг. 4В - схема варианта осуществления процедуры, связанной с командой векторного типа непосредственной проверки класса данных с плавающей запятой согласно фиг. 4А,

на фиг. 4Г - схема примера алгоритма исполнения команды векторного типа непосредственной проверки класса данных с плавающей запятой согласно фиг. 4А,

на фиг. 4Д - пример определения различных классов данных с плавающей запятой в двоичной форме представления,

на фиг. 5А - схема примера формата команды векторного типа контрольной суммы (англ.: Vector Checksum),

на фиг. 5Б - схема варианта осуществления процедуры, связанной с командой векторного типа контрольной суммы согласно фиг. 5А,

на фиг. 5В - схема примера алгоритма исполнения команды векторного типа контрольной суммы согласно фиг. 5А,

на фиг. 6А - схема примера формата команды векторного типа на поле Галуа перемножения, суммирования и накопления (англ.: Vector Galois Field Multiply Sum and Accumulate),

на фиг. 6Б - схема варианта осуществления процедуры, связанной с командой векторного типа на поле Галуа перемножения, суммирования и накопления согласно фиг. 6А,

на фиг. 6В - схема примера алгоритма исполнения команды векторного типа на поле Галуа перемножения, суммирования и накопления согласно фиг. 6А,

на фиг. 7А - схема примера формата команды векторного типа формирования маски (англ.: Vector Generate Mask),

на фиг. 7Б - схема варианта осуществления процедуры, связанной с командой векторного типа формирования маски согласно фиг. 7А,

на фиг. 7В - схема примера алгоритма исполнения команды векторного типа формирования маски согласно фиг. 7А,

на фиг. 8А - схема примера формата команды векторного типа циклического сдвига элемента и вставки по маске (англ.: Vector Element Rotate and Insert Under Mask),

на фиг. 8Б - схема варианта осуществления процедуры, связанной с командой векторного типа циклического сдвига элемента и вставки по маске согласно фиг. 8А,

на фиг. 8В - схема примера алгоритма исполнения команды векторного типа циклического сдвига элемента и вставки по маске согласно фиг. 8А,

на фиг. 9А - схема примера кода векторного исключения,

на фиг. 9Б - схема варианта осуществления процедуры, связанной с установкой кода векторного исключения согласно фиг. 9А,

на фиг. 10 - графическое представление варианта осуществления компьютерного программного продукта, содержащего один или несколько аспектов изобретения,

на фиг. 11 - схема варианта выполнения хост-компьютерной системы,

на фиг. 12 - схема еще одного примера компьютерной системы,

на фиг. 13 - схема другого примера компьютерной системы, содержащей вычислительную сеть,

на фиг. 14 - схема варианта выполнения различных узлов компьютерной системы,

на фиг. 15А - схема варианта выполнения исполнительного устройства из состава компьютерной системы, показанной на фиг. 14,

на фиг. 15Б - схема варианта выполнения устройства ветвления из состава компьютерной системы, показанной на фиг. 14,

на фиг. 15В - схема варианта выполнения устройства загрузки-хранения из состава компьютерной системы, показанной на фиг. 14,

на фиг. 16 - схема варианта выполнения эмулируемой (виртуальной) хост-компьютерной системы.

Осуществление изобретения

[0028] Согласно одному или нескольким аспектам изобретения предлагается векторное средство, которое содержит различные команды векторного типа, а также обработку векторных исключений. Каждая из указанных команд, описанных в настоящей заявке, является командой типа "одиночный поток команд, множественный поток данных", использующей один или несколько векторных регистров (в настоящей заявке векторные регистры также называются векторами). Векторным регистром является, например, регистр процессора (называемый также аппаратным регистром), который представляет собой небольшое по объему пространство памяти (например, не являющееся пространством памяти главного запоминающего устройства), доступное как часть ЦПУ или другого процессора. Каждый векторный регистр содержит векторный операнд, содержащий один или несколько элементов, и длина элемента составляет, например, один, два, четыре или восемь байтов. В других вариантах осуществления изобретения элементы могут иметь другие длины, а команда векторного типа не обязательно должна быть командой типа "одиночный поток команд, множественный поток данных".

[0029] Схема одного варианта осуществления вычислительной среды для внедрения и использования одного или нескольких аспектов изобретения показана на фиг. 1. Вычислительная среда 100 содержит, например, процессор 102 (например, ЦПУ), запоминающее устройство 104 (например, главное запоминающее устройство) и одно или несколько устройств ввода-вывода и/или интерфейсов 106, соединенных с другой вычислительной средой, например, через одну или несколько шин 108 и/или иных соединений.

[0030] В одном примере процессор 102 основан на архитектуре z/Architecture (торговая марка, обозначающая архитектуру линейки мейнфреймов), предложенной корпорацией International Business Machines Corporation (корпорацией IBM) и являющейся частью сервера, такого как сервер System z (торговая марка, обозначающая линейку мейнфреймов), который также предлагается корпорацией International Business Machines Corporation и в котором реализована архитектура zl Architecture. Один из вариантов осуществления архитектуры z/Architecture описан в публикации IBM® "z/Architecture Principles of Operation" ("Принцип действия архитектуры z/Architecture", публикация IBM № SA22-7832-08, 10-е издание, сентябрь 2012 г.), которая включена в настоящую заявку путем ссылки во всей своей полноте. В одном примере указанный процессор исполняет команды операционной системы, такой как z/OS, также предлагаемой корпорацией IBM. IBM®, Z/ARCHITECTURE® и Z/OS® являются зарегистрированными торговыми марками корпорации International Business Machines Corporation, Армонк, штат Нью-Йорк, США. Прочие наименования, используемые в настоящей заявке, могут также быть зарегистрированными торговыми марками, торговыми марками или наименованиями продуктов корпорации International Business Machines Corporation или других компаний.

[0031] Согласно другому варианту осуществления изобретения процессор 102 основан на архитектуре POWER Architecture (от англ. Performance Optimization With Enhanced RISC - оптимизация производительности с применением улучшенной архитектуры RISC), предложенной корпорацией IBM. Один вариант осуществления архитектуры POWER Architecture описан в публикации корпорации IBM "Power ISA™ Version 2.06 Revision В" от 23 июля 2010 г.), которая включена в настоящую заявку путем ссылки во всей своей полноте. POWER ARCHITECTURE® является зарегистрированной торговой маркой корпорации International Business Machines Corporation.

[0032] Согласно еще одному варианту осуществления, процессор 102 основан на архитектуре Intel, предложенной корпорацией Intel. Один вариант осуществления архитектуры Intel описан в публикациях "Intel® 64 and IA-32 Architectures Developer's Manual: Vol. 2B, Instructions Set Reference, A-L", номер заказа 253666-045US, январь 2013 г., и "Intel® 64 and IA-32 Architectures Developer's Manual: Vol. 2B, Instructions Set Reference, M-Z", номер заказа 253667-045US, январь 2013 г., которые включены в настоящую заявку путем ссылки во всей своей полноте. Intel® является зарегистрированной торговой маркой корпорации Intel Corporation, г. Санта-Клара, штат Калифорния, США.

[0033] Схема другого варианта осуществления вычислительной среды для внедрения и использования одного или нескольких аспектов изобретения показана на фиг. 2А. В данном примере вычислительная среда 200 содержит, например, собственное ЦПУ 202, запоминающее устройство 204 и одно или несколько устройств ввода-вывода и/или интерфейсов 206, соединенных между собой, например, через одну или несколько шин 208 и/или других соединений. Например, вычислительная среда 200 может содержать: процессор PowerPC, сервер pSeries или сервер xSeries, предложенные корпорацией International Business Machines Corporation, Армонк, штат Нью-Йорк, США; сервер HP Superdome с процессорами Intel Itanium II, предложенный корпорацией Hewlett Packard Corporation, г. Пало-Альто, штат Калифорния, США; и/или другие электронно-вычислительные машины, основанные на архитектурах, предложенных корпорациями International Business Machines Corporation, Hewlett Packard, Intel, Oracle или другими компаниями и корпорациями.

[0034] Собственное ЦПУ 202 содержит один или несколько собственных регистров 210, таких как один или несколько регистров общего назначения и/или один или несколько регистров специального назначения, используемых при обработке в вычислительной среде. Эти регистры содержат информацию, которая представляет состояние вычислительной среды в каждый отдельно взятый момент времени.

[0035] Кроме того, собственное ЦПУ 202 исполняет команды и программный код, которые хранятся в запоминающем устройстве 204. Согласно одному конкретному примеру, ЦПУ выполняет код 212 эмулятора, хранящийся в запоминающем устройстве 204. Этот код позволяет среде обработки, сконфигурированной по одной архитектуре, эмулировать (т.е. имитировать) другую архитектуру. Например, код 212 эмулятора позволяет электронным вычислительным машинам, основанным на архитектурах, отличных от z/Architecture, таким как процессоры PowerPC, серверы pSeries, серверы xSeries, серверы HP Superdome или другим, имитировать архитектуру z/Architecture и выполнять программное обеспечение и команды, разработанные для архитектуры z/Architecture.

[0036] Дальнейшие сведения о коде 212 эмулятора приводятся с использованием фиг. 2Б. Гостевые команды 250, хранящиеся в запоминающем устройстве 204, содержат команды программного обеспечения (например, взаимосвязанные с машинными командами), которые были разработаны для исполнения на архитектуре, отличной от архитектуры собственного ЦПУ 202. Например, гостевые команды 250 могли были быть разработаны для исполнения на процессоре 102, построенном по архитектуре z/Architecture, однако вместо этого эмулируются на собственном ЦПУ 202, которое может быть, например, процессором типа Intel Itanium II. В одном из примеров код 212 эмулятора содержит процедуру 252 выборки команд, предназначенную для получения одной или нескольких гостевых команд 250 из запоминающего устройства 204 и, возможно, для выполнения локальной буферизации (временного хранения) полученных команд. Этот код 212 эмулятора также содержит процедуру 254 трансляции команд, предназначенную для определения типа поступившей гостевой команды и трансляции указанной гостевой команды в одну или несколько соответствующих собственных команд 256 (т.е. команд, предназначенных для исполнения собственным ЦПУ, построенным по собственной архитектуре). В состав процедуры трансляции входят, например, идентификация функции, которая должна выполняться гостевой командой, и выбор собственной команды или набора команд для выполнения этой функции.

[0037] Далее, эмулятор 212 содержит процедуру 260 управления эмуляцией, обеспечивающую исполнение собственных команд. Процедура 260 управления эмуляцией может заставить собственное ЦПУ 202 выполнять программу из собственных команд, которая имитирует одну или несколько раннее поступивших гостевых команд, и по окончании этого вычислительного процесса возвращать управление упомянутой процедуре выборки команд для имитации получения следующей гостевой команды или группы гостевых команд. Процесс исполнения собственных команд 256 может содержать загрузку данных в регистр из запоминающего устройства 204, передачу данных из регистра обратно в запоминающее устройство для хранения или выполнение некоторой арифметической или логической операции в соответствии с определенной процедурой трансляции.

[0038] Каждая процедура реализована, например, в программном обеспечении, которое хранится в запоминающем устройстве и выполняется собственным ЦПУ 202. В других примерах одна или несколько процедур или операций реализованы в постоянном запоминающем устройстве (ПЗУ), в аппаратном или программном обеспечении или в их комбинации. Упомянутые регистры эмулируемого процессора могут имитироваться с использованием регистров 210 собственного ЦПУ или с использованием ячеек памяти запоминающего устройства 204. В вариантах осуществления гостевые команды 250, собственные команды 256 и код 212 эмулятора могут располагаться в одном и том же запоминающем устройстве или могут храниться распределенно в различных запоминающих устройствах.

[0039] В рассматриваемом примере ПЗУ хранит, например, микрокод, милликод и/или макрокод процессора. Код содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации машинных кодов более высокого уровня. В одном варианте осуществления код содержит, например, проприетарный код, который обычно поставляется как микрокод, содержащий выверенное программное обеспечение, или микрокод, специфический для окружающего аппаратного обеспечения и контролирующий доступ операционной системы к аппаратному обеспечению вычислительной системы.

[0040] В одном примере загружаемая, транслируемая и исполняемая гостевая команда 250 является одной из команд, описанных в настоящей заявке. Эта команда, предназначенная для одной архитектуры (например, для архитектуры z/Architecture), извлекается из запоминающего устройства, транслируется и представляется последовательным набором собственных команд 256 другой архитектуры (например, архитектуры PowerPC, pSeries, xSeries, Intel и т.д.). Затем указанные собственные команды исполняются.

[0041] В одном варианте осуществления изобретения описанные в настоящей заявке команды являются командами векторного типа и являются частью векторного функционала (т.е. векторной среды, набора команд векторного типа и средств их обработки). Векторный функционал позволяет работать, например, с векторами фиксированной длины в пределах от одного до шестнадцати элементов. Каждый вектор содержит данные, которые обрабатываются командами векторного типа, определенными в векторном функционале. Согласно варианту осуществления, если вектор образован из набора элементов, то каждый элемент обрабатывается параллельно с другими элементами. Исполнение команды не завершено, пока не завершена обработка всех элементов вектора. В других вариантах осуществления изобретения элементы обрабатываются частично параллельно и/или последовательно.

[0042] Команды векторного типа могут использоваться как часть различных архитектур, включая (но не ограничиваясь) архитектуры z/Architecture, Power, х86, IA-32, IA-64 и т.д. Хотя варианты осуществления изобретения, описанные в настоящей заявке, описываются применительно к архитектуре z/Architecture, однако команды векторного типа, описанные в настоящей заявке, а также один или несколько других аспектов изобретения могут основываться на многих других архитектурах. Архитектура z/Architecture используется исключительно в качестве одного из примеров.

[0043] Согласно варианту осуществления изобретения, в котором векторный функционал применяется как часть архитектуры z/Architecture, для того, чтобы использовать указанные векторные регистры и команды векторного типа, в специализированном управляющем регистре (например, в управляющем регистре 0) флаги разрешения векторного функционала и векторных регистров должны быть установлены в состояние, например, логической единицы. Если векторный функционал инсталлирован и команда векторного типа исполняется без разрешающих флагов, то возбуждается исключение данных. Если векторный функционал не инсталлирован и делается попытка исполнить команду векторного типа, то возбуждается исключение исполнения.

[0044] В одном варианте осуществления имеется 32 векторных регистра, причем регистры других типов могут отображаться на область-квадрант векторных регистров. Например, как показано на фиг. 3, файл 300 регистров содержит 32 векторных регистра 302, и длина каждого регистра составляет 128 двоичных разрядов. Шестнадцать регистров 304 с плавающей запятой длиной 64 двоичных разряда каждый могут перекрываться с векторными регистрами. Таким образом, например, если изменится содержимое регистра 2 с плавающей запятой, то содержимое векторного регистра 2 также изменится. Для регистров других типов также возможны и другие отображения.

[0045] Векторные данные располагаются в запоминающем устройстве, например, в той же самой последовательности, слева направо, как и прочие форматы данных. Двоичные разряды 0-7 формата данных образуют байт в крайней левой (с наименьшим номером) ячейке хранения байтов запоминающего устройства; двоичные разряды 8-15 образуют байт в следующей за предыдущей ячейке запоминающего устройства и т.д. В другом примере векторные данные могут располагаться в запоминающем устройстве в иной последовательности, например, справа налево.

[0046] Каждая команда векторного типа, описанная в настоящей заявке, содержит набор полей, и одно или несколько указанных полей снабжены нижним числовым индексом, связанным с данным полем. Нижний индекс, связанный с полем команды, обозначает операнд, к которому это поле применяется. Например, нижний индекс "1" в обозначении "V1" векторного регистра указывает на то, что регистр V1 содержит первый операнд и т.д. Операнд регистра имеет ту же длину, что и сам регистр, например, 128 двоичных разрядов.

[0047] Далее, многие команды векторного типа, поддерживаемые векторным функционалом, снабжены полем, состоящим из специальных двоичных разрядов. Такое поле, называемое полем RXB (от англ. register extension bit - бит расширения регистра), содержит наиболее значимый двоичный разряд для каждого из операндов, указываемых векторным регистром. Двоичные разряды для обозначений регистров, не указанные командой, должны быть зарезервированы и должны быть установлены в состояние логического нуля. Наиболее значимый двоичный разряд объединяется операцией конкатенации, например, слева с четырехразрядным обозначением регистра для формирования пятиразрядного обозначения векторного регистра.

[0048] В одном примере указанное поле RXB содержит четыре двоичных разряда (например, 0-3), и эти разряды имеют следующее назначение:

разряд 0 - наиболее значимый разряд обозначения первого векторного регистра указанной команды (например, в разрядах 8-11);

разряд 1 - наиболее значимый разряд обозначения второго векторного регистра (например, в разрядах 12-15) указанной команды, если таковой предусмотрен;

разряд 2 - наиболее значимый разряд обозначения третьего векторного регистра (например, в разрядах 16-19) указанной команды, если таковой предусмотрен;

разряд 3 - наиболее значимый разряд обозначения четвертого векторного регистра (например, в разрядах 32-35) указанной команды, если таковой предусмотрен.

[0049] Каждый двоичный разряд устанавливается в состояние логического нуля или логической единицы, например, ассемблером, в зависимости от номера регистра. Например, для регистров 0-15 этот разряд устанавливается в состояние логического нуля, для регистров 16-31 этот разряд устанавливается в состояние логической единицы и т.д.

[0050] В одном варианте осуществления каждый двоичный разряд поля RXB является разрядом расширения определенного поля команды, которое содержит один или несколько векторных регистров. Например, в одной или нескольких командах векторного типа разряд 0 поля RXB является разрядом-расширением поля команды с позициями 8-11, это поле обозначается, например, как V1; разряд 1 поля RXB является разрядом-расширением поля команды с позициями 12-15, это поле команды обозначается, например, как V2, и т.д. В другом варианте осуществления поле RXB содержит дополнительные двоичные разряды, и для каждого вектора или поля в качестве разрядов-расширений используются по два и более разрядов.

[0051] Согласно аспекту изобретения, одной из предоставляемых команд, содержащих поле RXB, является команда векторного типа непосредственной проверки класса данных с плавающей запятой, пример формата которой показан на фиг. 4А (мнемонический код команды - VFTCI). В одном примере команда 400 векторного типа непосредственной проверки класса данных с плавающей запятой содержит: поля 402а (например, двоичные разряды 0-7) и 402b (например, разряды 40-47) кода операции, идентифицирующие операцию векторного типа непосредственной проверки класса данных с плавающей запятой; поле 404 первого векторного регистра (например, разряды 8-11), используемое для обозначения первого векторного регистра (V1); поле 406 второго векторного регистра (например, разряды 12-15), используемое для обозначения второго векторного регистра (V2); примыкающее поле I3 408 (например, разряды 16-27) для размещения двоичной маски; поле 410 первой маски (М5) (например, разряды 28-31); поле 412 второй маски (М4) (например, разряды 32-35); поле 414 RXB (например, разряды 36-39). В одном примере каждое из полей 404-414 является отдельным и независимым от поля (полей) кода операции. Далее, в одном варианте осуществления указанные поля являются отдельными и независимыми друг от друга; однако в других вариантах осуществления два и более полей могут быть объединенными. Ниже приводятся дальнейшие сведения об использовании перечисленных полей.

[0052] В одном примере выбранные двоичные разряды (например, первые два