Многовходовый логический элемент и

Иллюстрации

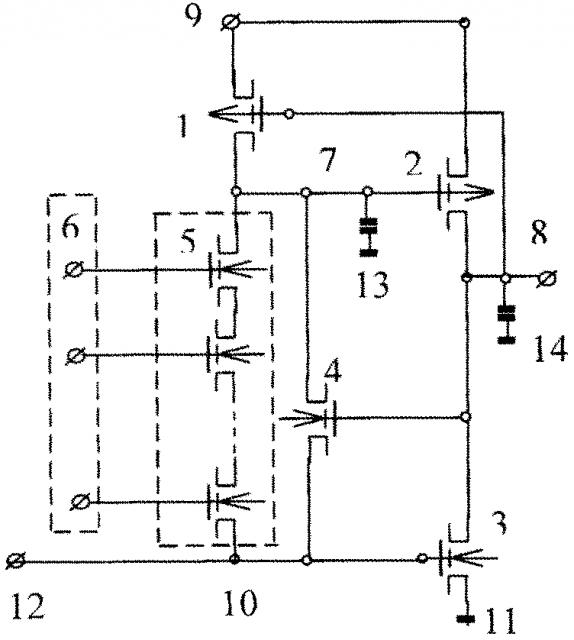

Показать всеИзобретение относится к области вычислительной техники и может быть использовано для реализации логических устройств на КМДП транзисторах. Технический результат заключается в упрощении устройства. Многовходовой логический элемент И содержит предзарядовый 1 и логический 2 транзисторы p-типа, тактовый 3 и дополнительный 4 транзисторы n-типа и ключевую цепь 5, состоящую из последовательно соединенных логических транзисторов n-типа, затворы которых подключены к логическим входам 6 устройства, первый вывод 7 ключевой цепи 5 соединен с затвором логического транзистора 2 p-типа, который включен между выходом 8 устройства и шиной питания 9, второй вывод 10 ключевой цепи 5 соединен с затвором тактового транзистора 3 n-типа, который включен между выходом устройства и шиной земли 11, дополнительный транзистор 4 n-типа, затвор которого соединен с выходом 8 устройства, включен между первым 7 и вторым выводами 10 ключевой цепи, предзарядовый транзистор 1, затвор которого соединен с выходом 8 устройства, включен между первым выводом 7 ключевой цепи 5 и шиной питания 9, а второй 10 вывод ключевой цепи 5 подключен к тактовой шине 12. 1 ил.

Реферат

Изобретение относится к области вычислительной техники и может быть использовано для реализации КМДП логических устройств.

Известен тактируемый логический элемент с функцией И на КМДП транзисторах (Патент №2412542, МКИ Н03К 19/20, 19/017, от 20.02.2011). Устройство содержит элемент И-НЕ из двух ключевых цепей на транзисторах n-типа и предзарядовых транзисторов p-типа в виде нагрузки, инвертирующий элемент, содержащий логический транзистор p-типа и тактовый транзистор n-типа, а также транзисторы обратной связи. Недостаток этого устройства - его избыточная сложность. Наиболее близким техническим решением к предлагаемому является многовходовый логический элемент И на КМДП транзисторах (Патент РФ №2319299, МКИ Н03К 19/20,19/017, 19/094, от 10.3.2008). Это устройство, принятое за прототип, содержит элемент И-НЕ, выполненный в виде ключевой цепи на логических транзисторах n-типа и предзарядового транзистора p-типа, а также инвертирующий элемент и транзистор обратной связи. Недостаток этого устройства - избыточная сложность как следствие наличия шести транзисторов (помимо логических) с соответствующими связями.

Техническим результатом изобретения является упрощение устройства. Технический результат достигается тем, что многовходовый логический элемент И содержит предзарядовый и логический транзисторы p-типа, тактовый и дополнительный транзисторы n-типа и ключевую цепь, состоящую из последовательно соединенных логических транзисторов n-типа, затворы которых подключены к логическим входам устройства, первый вывод ключевой цепи соединен с затвором логического транзистора p-типа, который включен между выходом устройства и шиной питания, второй вывод ключевой цепи соединен с затвором тактового транзистора п-типа, который включен между выходом устройства и шиной земли, дополнительный транзистор n-типа, затвор которого соединен с выходом устройства, включен между первым и вторым выводами ключевой цепи, предзарядовый транзистор p-типа включен между первым выводом ключевой цепи и шиной питания, затвор предзарядового транзистора p-типа соединен с выходом устройства, а второй вывод ключевой цепи подключен к тактовой шине.

Существенными отличительными признаками в указанной совокупности признаков является подключение затвора предзарядового транзистора p-типа с выходом устройства и подключение второго вывода ключевой цепи к тактовой шине.

Наличие в предлагаемом устройстве перечисленных выше существенных признаков обеспечивает решение поставленной технической задачи - упрощения устройства. В устройстве-прототипе используются помимо логических шесть транзисторов, а в заявленном устройстве - на два транзистора меньше. При этом предзарядовый транзистор включен в цепь отрицательной обратной связи, а дополнительный транзистор n-типа в цепи положительной обратной связи управляется непосредственно от тактовой шины.

На чертеже приведена принципиальная схема заявленного устройства.

Многовходовой логический элемент И содержит предзарядовый 1 и логический 2 транзисторы p-типа, тактовый 3 и дополнительный 4 транзисторы n-типа и ключевую цепь 5, состоящую из последовательно соединенных логических транзисторов n-типа, затворы которых подключены к логическим входам 6 устройства, первый вывод 7 ключевой цепи 5 соединен с затвором логического транзистора 2 p-типа, который включен между выходом 8 устройства и шиной питания 9, второй вывод 10 ключевой цепи 5 соединен с затвором тактового транзистора 3 n-типа, который включен между выходом устройства и шиной земли 11, дополнительный транзистор 4 n-типа, затвор которого соединен с выходом 8 устройства, включен между первым 7 и вторым выводами 10 ключевой цепи, предзарядовый транзистор 1, затвор которого соединен с выходом 8 устройства, включен между первым выводом 7 ключевой цепи 5 и шиной питания 9, а второй 10 вывод ключевой цепи 5 подключен к тактовой шине 12.

Устройство работает следующим образом. В исходном состоянии - на первом полутакте, при положительном сигнале на тактовой шине тактовый транзистор 3 n-типа открыт, конденсатор 14, представляющий собой узловую нагрузку, разряжается до 0. Ключевая цепь 5 либо закрыта, либо работает в инверсионном режиме. Предзарядовый транзистор 1 p-типа открывается и конденсатор 13, являющийся узловой емкостью, от шины питания 9 заряжается до напряжения питания. Логический транзистор 2 p-типа при этом закрывается. На первом полутакте на логических входах 6 устанавливаются сигналы, соответствующие выполняемой функции. Когда хотя бы на одном логическом входе 6 присутствует сигнал логического 0, ключевая цепь 5 не проводит, дополнительный транзистор также закрыт и устройство сохраняет исходное состояние, соответствующее функции, равной 0.

На втором полутакте на тактовую шину 12 поступает нулевой сигнал. Тактовые транзисторы 3 при этом закрываются и подготавливают выход 8 устройства к формированию логического сигнала. Когда на затворы логических транзисторов n-типа ключевой цепи 5 поданы сигналы логической 1, что соответствует функции И, равной 1, ключевая цепь оказывается в проводящем состоянии и узловая емкость (конденсатор 13) разряжается. Логический транзистор 2 p-типа при этом открывается, предзарядовый транзистор 1 p-типа в цепи обратной связи закрывается, а дополнительный транзистор 4 n-типа в цепи положительной обратной связи также открывается, ускоряя процесс разядки конденсатора 13, поскольку на тактовой шине 12 предварительно сформирован нулевой сигнал. На выходе 8 устройства формируется сигнал логической 1. При восстановлении исходного состояния ключевая цепь 5 закрывается непосредственно от сигнала на тактовой шине 12, а дополнительный транзистор 4 n-типа работает в инверсионном режиме, что служит ускорению заряда конденсатора 13 и переходу логического транзистора 2 в закрытое состояние.

Многовходовый логический элемент И-ИЛИ, содержащий предзарядовый и логический транзисторы p-типа, тактовый и дополнительный транзисторы n-типа и ключевую цепь, состоящую из последовательно соединенных логических транзисторов n-типа, затворы которых подключены к логическим входам устройства, первый вывод ключевой цепи соединен с затвором логического транзистора p-типа, который включен между выходом устройства и шиной питания, второй вывод ключевой цепи соединен с затвором тактового транзистора n-типа, который включен между выходом устройства и шиной земли, дополнительный транзистор n-типа, затвор которого соединен с выходом устройства, включен между первым и вторым выводами ключевой цепи, предзарядовый транзистор p-типа включен между первым выводом ключевой цепи и шиной питания, отличающийся тем, что затвор предзарядового транзистора p-типа соединен с выходом устройства, а второй вывод ключевой цепи подключен к тактовой шине.