Измеритель скорости счета статистически распределенных во времени импульсов

Иллюстрации

Показать всеИзобретение относится к ядерной технике и может быть применено для обработки сигнала ионизационных камер, регистрирующих уровень ионизирующего излучения. Измеритель скорости счета статистически распределенных во времени импульсов содержит разравниватель импульсов, первый элемент И, двоичный счетчик, регистр, делитель, генератор тактовых импульсов, управляющий блок, блок памяти, сумматор-вычитатель и счетчик адреса памяти. Разравниватель импульсов включает в себя первый и второй счетчики, компаратор, второй элемент И и генератор опорной частоты. Вход первого счетчика является входом разравнивателя импульсов, выход первого счетчика соединен со входом компаратора, выход которого подключен к одному входу второго элемента И, второй вход второго элемента И подключен к генератору опорной частоты, выход второго элемента И соединен со входом второго счетчика, первый выход которого подключен ко второму входу компаратора, а второй его выход является выходом разравнивателя импульсов и подключен ко входу управляющего блока. Выходы управляющего блока подключены к первому входу первого элемента И, первому входу двоичного счетчика, первому входу регистра, входу блока памяти, входу сумматора-вычитателя, входу делителя и входу счетчика адреса памяти. Второй вход первого элемента И соединен с выходом генератора тактовых импульсов, а выход первого элемента И соединен со вторым входом двоичного счетчика, выход которого подключен ко второму входу регистра, ко входу блока памяти подключены выходы регистра и счетчика адреса памяти, выход блока памяти соединен со входом сумматора-вычитателя, выход которого подключен к его же входу, а также ко входу делителя, выход делителя является выходом устройства. Технический результат - повышение помехоподавления, расширение динамического диапазона и автоматическое увеличение быстродействия при увеличении частоты входных импульсов. 3 ил.

Реферат

Настоящее изобретение относится к ядерной технике и может быть применено для обработки сигнала ионизационных камер, регистрирующих уровень ионизирующего излучения (потока нейтронов, гамма-квантов и др.).

Наиболее близким по совокупности существенных признаков к изобретению является измеритель скорости счета статистически распределенных импульсов, содержащий разравниватель импульсов, элемент И, двоичный счетчик, регистр, делитель и генератор тактовых импульсов (авт.св. SU 864165, G01R 23/00, опубл. 15.09.1981).

В известном устройстве используется две цепи с обратными связями. Это не позволит в динамических режимах при быстром росте скорости счета точно измерить среднюю скорость статистически распределенных импульсов. При использовании устройства для контроля периода роста мощности ядерного реактора сигнал периода может иметь ложные выбросы. Кроме того, описанное устройство при использовании для контроля очень низких скоростей счета (менее 0,1 1/с) будет иметь значительную погрешность.

Задачей настоящего изобретения является создание измерителя скорости счета статистически распределенных во времени импульсов, который характеризуется надежностью измерения скорости счета импульсов, большим динамическим диапазоном и высокой достоверностью.

Техническим результатом настоящего изобретения является повышение помехоподавления, расширение динамического диапазона и автоматическое увеличение быстродействия при увеличении частоты входных импульсов.

Указанный технический результат достигается тем, что известный измеритель скорости счета статистически распределенных во времени импульсов, содержащий разравниватель импульсов, первый элемент И, двоичный счетчик, регистр, делитель и генератор тактовых импульсов дополнительно содержит управляющий блок, блок памяти, сумматор-вычитатель и счетчик адреса памяти, при этом разравниватель импульсов включает в себя первый и второй счетчики, компаратор, второй элемент И и генератор опорной частоты, причем вход первого счетчика является входом разравнивателя импульсов, выход первого счетчика соединен со входом компаратора, выход которого подключен к одному входу второго элемента И, второй вход второго элемента И подключен к генератору опорной частоты, выход второго элемента И соединен со входом второго счетчика, первый выход которого подключен ко второму входу компаратора, а второй его выход является выходом разравнивателя импульсов и подключен ко входу управляющего блока, выходы которого подключены к первому входу первого элемента И, первому входу двоичного счетчика, первому входу регистра, входу блока памяти, входу сумматора-вычитателя, входу делителя и входу счетчика адреса памяти, при этом второй вход первого элемента И соединен с выходом генератора тактовых импульсов, а выход первого элемента И соединен со вторым входом двоичного счетчика, выход которого подключен ко второму входу регистра, ко входу блока памяти подключены выходы регистра и счетчика адреса памяти, выход блока памяти соединен со входом сумматора-вычитателя, выход которого подключен к его же входу, а также ко входу делителя, выход делителя является выходом устройства.

Повышение помехоподавления обеспечивается ограничением емкости первого счетчика разравнивателя вышеописанной конструкции, т.к. при увеличении частоты выше (где К - разрядность счетчика) наступает его переполнение, и, следовательно, после воздействия помехи максимальное число обрабатываемых импульсов помехи будет равно остатку количества импульсов на первом счетчике, который зависит от разрядности счетчика. Увеличение динамического диапазона работы и уменьшение погрешности обеспечивается за счет применения автоматически изменяемой в зависимости от частоты входных импульсов экспозицией, что также позволяет при малых скоростях счета существенно снизить флуктуации сигнала периода, и тем самым обеспечивается расширение динамического диапазона.

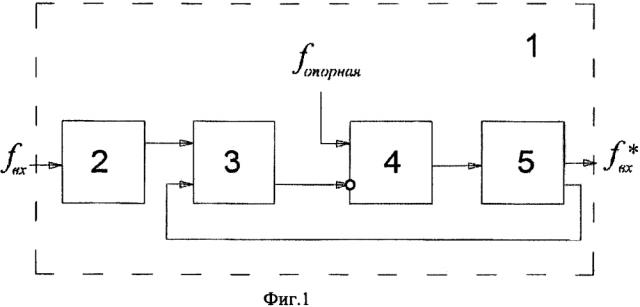

Сущность изобретения поясняется чертежами. На фиг. 1 представлена блок-схема разравнивателя импульсов. На фиг. 2 представлена блок-схема измерителя скорости счета. На фиг. 3 изображен порядок формирования сигналов управляющим блоком.

Измеритель скорости счета статистически распределенных во времени импульсов содержит разравниватель импульсов 1, вход которого является входом устройства. Разравниватель импульсов 1 включает в себя первый счетчик 2, компаратор 3, второй элемент И 4, второй счетчик 5 и генератор опорной частоты. Вход разравнивателя импульсов 1 также является входом первого счетчика 2, выход которого соединен со входом компаратора 3, выход которого в свою очередь подключен к одному входу второго элемента И 4. Второй вход второго элемента И 4 подключен к генератору опорной частоты, а его выход соединен со входом второго счетчика 5. Первый выход последнего подключен ко второму входу компаратора 3, а второй выход является выходом разравнивателя импульсов 1 и подключен ко входу управляющего блока 6. Выходы управляющего блока 6 подключены к первому входу первого элемента И 7, первому входу двоичного счетчика 8, первому входу регистра 9, входу блока памяти 10, входу сумматора-вычитателя 11, входу делителя 12 и входу счетчика адреса памяти 13. Второй вход первого элемента И 7 соединен с выходом генератора тактовых импульсов, а выход его соединен со вторым входом двоичного счетчика 8. Выход двоичного счетчика подключен ко второму входу регистра 9. Вход блока памяти 10 подключен к выходам регистра 9 и счетчика адреса памяти 13. Выход блока памяти 10 в свою очередь соединен со входом сумматора-вычитателя 11. Выход сумматора-вычитателя 11 подключен к его же входу, a также ко входу делителя 12. Выход последнего является выходом устройства.

Измеритель скорости счета статистически распределенных во времени импульсов работает следующим образом.

На вход измерителя скорости счета поступают импульсы с переменной частотой . С каждым приходящим импульсом в устройстве корректируется выходное значение скорости счета. На обработку каждого приходящего импульса требуется некоторое время. Для предоставления измерителю скорости счета такого временного промежутка после каждого импульса используется разравниватель импульсов 1. Если пауза между несколькими импульсами во входящем сигнале недостаточная для обработки каждого из них устройством, разравниватель 1 увеличивает эту паузу.

Разравниватель импульсов 1 работает следующим образом (см. фиг. 1). Импульс входящего сигнала увеличивает значение, хранящееся в первом счетчике 2, на единицу, компаратор 3 сравнивает показания первого 2 и второго 5 счетчиков и в случае их равенства подает логическую единицу на инвертированный вход второго элемента И 4. В случае, если показания на первом 2 и втором 5 счетчиках различны, второй элемент И 4 пропускает один импульс сигнала опорной частоты на второй счетчик 5. Таким образом, на выходе разравнивателя импульсов 1 оказывается то же количество импульсов, что и на входе. При этом, если временной интервал между импульсами на входе разравнивателя импульсов может быть меньше, чем период сигнала , то на выходе разравнивателя импульсов временной интервал между импульсами будет больше или равен . Подобное разравнивание необходимо, когда для обработки каждого импульса измерителем скорости счета необходимо время не менее . Минимальное время определяется исходя из времени, необходимого для работы оставшейся части измерителя скорости счета.

После прохождения сигнала через разравниватель импульсов 1 оставшаяся часть измерителя скорости счета работает следующим образом. Импульс, прошедший через разравниватель импульсов 1, запускает цикл работы управляющего устройства 6, которое по очереди подает управляющие сигналы на остальные элементы измерителя скорости счета (см. фиг. 2 и 3). Первый элемент И 7 размыкается, и тактовые импульсы перестают поступать на двоичный счетчик 8, показания двоичного счетчика сохраняются в регистре 9 и затем значения количества импульсов, поступивших на двоичный счетчик 8, сбрасываются. Элемент И 7 замыкается и на двоичный счетчик 8 начинают поступать тактовые импульсы. Счетчик адреса памяти 13 переключается на адрес самого «старого» значения временного интервала, хранящегося в блоке памяти 10 (значения временных интервалов представляют собой количество импульсов тактовой частоты). В сумматоре-вычитателе 11 производится вычитание наиболее «старого» значения временного (интервала, хранящегося в блоке памяти 10, из хранящейся в сумматоре-вычитателе 11 суммы интервалов. Счетчик адреса памяти 13 переключается на адрес блока памяти 10, куда будет записано значение временного интервала, полученного в текущем цикле. Значение последнего временного интервала записывается в блок памяти 10. В сумматоре-вычитателе 11 производится суммирование временного интервала, полученного в текущем цикле, и суммы интервалов, хранящейся в сумматоре-вычитателе. В делителе 12 происходит вычисление скорости счета импульсов как частного константы, рассчитанной с учетом значения тактовой частоты, и количества тактовых импульсов на выходе сумматора-вычитателя 11.

Таким образом, значение скорости счета на выходе измерителя скорости счета обладает следующими преимуществами: 1) динамически меняется постоянная времени - чем быстрее меняется скорость импульсов, тем меньше постоянная времени и быстрее корректируется выдаваемое значение скорости счета импульсов и периода роста мощности реактора; 2) постоянное известное значение статистической погрешности , где N - число импульсов, по временным интервалам между которыми вычисляется период (заранее выбранная константа); 3) разравниватель импульсов снижает влияние высокочастотных помех, ограничивая их разрядностью первого счетчика 2.

Измеритель скорости счета статистически распределенных во времени импульсов, содержащий разравниватель импульсов, первый элемент И, двоичный счетчик, регистр, делитель и генератор тактовых импульсов, отличающийся тем, что дополнительно содержит управляющий блок, блок памяти, сумматор-вычитатель и счетчик адреса памяти, а разравниватель импульсов включает в себя первый и второй счетчики, компаратор, второй элемент И и генератор опорной частоты, причем вход первого счетчика является входом разравнивателя импульсов, выход первого счетчика соединен со входом компаратора, выход которого подключен к одному входу второго элемента И, второй вход второго элемента И подключен к генератору опорной частоты, выход второго элемента И соединен со входом второго счетчика, первый выход которого подключен ко второму входу компаратора, а второй его выход является выходом разравнивателя импульсов и подключен ко входу управляющего блока, выходы которого подключены к первому входу первого элемента И, первому входу двоичного счетчика, первому входу регистра, входу блока памяти, входу сумматора-вычитателя, входу делителя и входу счетчика адреса памяти, при этом второй вход первого элемента И соединен с выходом генератора тактовых импульсов, а выход первого элемента И соединен со вторым входом двоичного счетчика, выход которого подключен ко второму входу регистра, ко входу блока памяти подключены выходы регистра и счетчика адреса памяти, выход блока памяти соединен со входом сумматора-вычитателя, выход которого подключен к его же входу, а также ко входу делителя, выход делителя является выходом устройства.