Определение профиля пути, используя комбинацию аппаратных и программных средств

Иллюстрации

Показать всеИзобретение относится к средствам определения профиля пути. Технический результат заключается в повышение оптимизации работы программы. Определяют, посредством процессора, соответствует ли первый идентификатор пути имеющемуся идентификатору пути из множества идентификаторов пути, при этом каждый идентификатор пути из множества идентификаторов пути содержит данные, указывающие путь выполнения, сигнатуру пути, идентифицирующую один или более блоков инструкций, и идентификатор инструкции, идентифицирующий первую инструкцию в первом блоке инструкции из одного или более блоков инструкций. Выполняют последовательное приращение счетчика, связанного с имеющимся идентификатором пути, когда первый идентификатор пути соответствует имеющемуся идентификатору пути. Добавляют, посредством процессора, первый идентификатор пути к множеству идентификаторов пути, когда первый идентификатор пути не соответствует имеющемуся идентификатору пути из множества идентификаторов пути. Удаляют по меньшей мере один идентификатор пути из множества идентификаторов пути на основе того, сколько раз путь выполнения, связанный с указанным по меньшей мере одним идентификатором, выполнен процессором. 6 н. и 19 з.п. ф-лы, 14 ил., 47 пр.

Реферат

Варианты осуществления, описанные здесь, в общем, относятся к устройствам обработки и, более конкретно, относятся к определению профиля пути.

Системы могут использовать информацию определения профиля, такую как профиль пути, для генерирования лучшего исполнительного кода и/или инструкций. Например, компьютеры, единовременные компиляторы (JIT), динамические бинарные трансляторы и т.д., могут использовать профиль пути для более эффективного и/или быстрого генерирования кода и/или инструкции. Информация об определении профиля пути может быть очень полезной в нескольких сценариях. Например, совместно разработанные устройства, содержащие программные/аппаратные средства, могут включать в себя уровень программных средств, который эмулирует, транслирует и оптимизирует инструкции поверх простой аппаратной конструкции. В совместно разработанном устройстве точная информация определения профиля пути может быть полезной для агрессивной оптимизации, такой как спекулятивное установление версии управления, и/или может обеспечивать лучшее понимание того, какие области инструкций выбрать для оптимизации. Определение профиля пути также может быть полезным для компиляторов JIT, таких как виртуальная машина Java® Virtual Machine или Microsoft® Common Language Runtime (CLR). Компилятор JIT может представлять собой программный уровень, который эмулирует и оптимизирует инструкции из портативного ISA (байтового кода) в собственный ISA, на котором работает виртуальная машина. Компиляторы JIT могут выполнять оптимизацию на основе пути и планирования трассы, для которой можно использовать преимущество применения точной информации об определении профиля пути (например, благодаря наличию точных профилей пути). Обычные компиляторы также могут использовать профили пути для выполнения оптимизации, которые генерируют более компактные и эффективные бинарные коды. Например, компилятор может использовать определение профиля пути для удаления невыполняемого кода и удаления общего подвыражения. Другое использование информации определения профиля состоит в идентификации сложного для выполнения пути (например, блоков инструкций, которые постоянно выполняются процессором или "горячих путей") для настройки рабочей характеристики и оптимизации программы. Определение профиля пути может использоваться для получения точной информации о выполненных путях.

Краткое описание чертежей

Раскрытие будет более понятным из подробного описания изобретения, представленного ниже, и из приложенных чертежей для различных вариантов осуществления раскрытия. Чертежи, однако, не следует рассматривать, как ограничение раскрытия конкретными вариантами осуществления, но они предназначены только для пояснения и лучшего понимания.

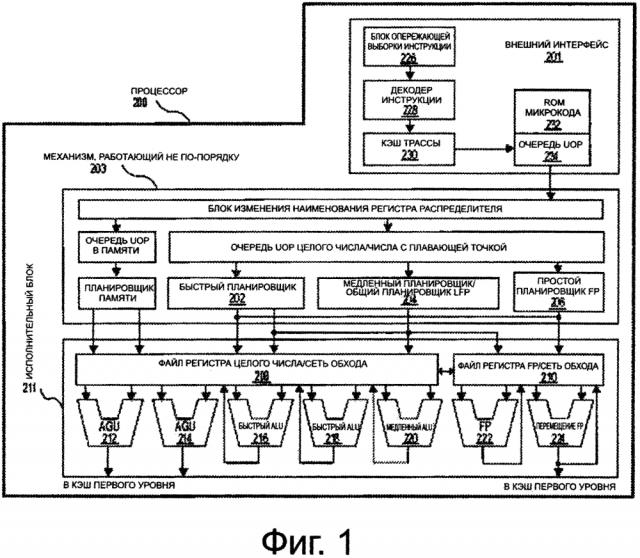

На фиг. 1 показана блок-схема микроархитектуры процессора 200, которая включает в себя логические схемы для выполнения инструкций, в соответствии с одним вариантом осуществления настоящего изобретения.

На фиг. 2 показана блок-схема, поясняющая конвейер, работающий по порядку, и этап переименования регистра, конвейер проблемы/выполнения команд не по порядку.

На фиг. 3 показана блок-схема, поясняющая архитектуру ядра и логику переименования регистра, выполняемую не по порядку проблему/логику выполнения, которая должна быть включена в процессор в соответствии с, по меньшей мере, одним вариантом осуществления раскрытия.

На фиг. 4 показана блок-схема вычислительной системы в соответствии с одним вариантом выполнения.

На фиг. 5 показана блок-схема приложения, включающая в себя блоки многоадресной команды, в соответствии с одним вариантом осуществления раскрытия.

На фиг. 6 представлена таблица, поясняющая пример данных идентификатора пути, в соответствии с одним вариантом выполнения раскрытия.

На фиг. 7 показана блок-схема архитектуры системы для генерирования профиля пути, в соответствии с одним вариантом выполнения раскрытия.

На фиг. 8 показана блок-схема, поясняющая модуль определения профиля для генерирования профиля пути, в соответствии с вариантом осуществления раскрытия.

На фиг. 9 показана блок-схема, поясняющая модуль идентификатора пути для отслеживания пути выполнения, в соответствии с вариантом осуществления раскрытия.

На фиг. 10 показана блок-схема последовательности операций, поясняющая способ генерирования профиля пути, в соответствии с одним вариантом выполнения раскрытия.

На фиг. 11 показана блок-схема последовательности операций, поясняющая способ отслеживания путей выполнения, в соответствии с одним вариантом выполнения раскрытия.

На фиг. 12 показана блок-схема системы на кристалле (SoC), в соответствии с вариантом осуществления настоящего раскрытия.

На фиг. 13 показана блок-схема варианта осуществления системы на кристалле (SOC), в соответствии с вариантом осуществления настоящего раскрытия.

На фиг. 14 показано схематическое изображение устройства в форме примера вычислительной системы, в которой может быть выполнен ряд инструкций для обеспечения выполнения устройством любой одной или больше методологий, описанных здесь.

При работе современных платформ или систем для определения профиля пути могут возникать значительные потоки служебной информации, что делает их непригодными для использования во время работы систем, таких как динамические двоичные трансляторы и компиляторы JIT, и делает их непривлекательными для статических или регулярных компиляторов. При работе современных платформ могут возникать потоки вспомогательной информации, поскольку информация определения профиля может быть собрана, в основном, программным компонентом (например, приложением), в результате выполнения дополнительных инструкций. Такие дополнительные потоки данных могут оказывать отрицательное влияние, такое как: (i) использование простой модели определения профиля, или (ii) определение профиля в течение малого временного окна. Эти два решения могут привести к ухудшению точности определения профиля для уменьшения потока вспомогательных данных, для получения информации профиля. Многие из современных платформ могут определять профиль частоты выполнения блоков инструкций (например, группы инструкций) и мест назначения ответвления (определение профиля на границе).

Как описано выше, каждое определение профиля пути может быть полезным в различных ситуациях. Варианты осуществления раскрытия приводят к генерированию профиля пути. В одном варианте осуществления модуль определения профиля может вставлять инструкции определения профиля в блоки инструкции. Инструкции определения профиля могут генерировать идентификатор пути, по мере того, как процессор выполняет путь выполнения (например, выполняет последовательность или путь блоков инструкции). Модуль идентификатора пути может добавлять идентификаторы пути к данным идентификатора пути, таким как таблица, и может отслеживать количество раз выполнения пути выполнения, ассоциированного с идентификатором пути. Модуль определения профиля может периодически копировать и/или модифицировать данные идентификатора пути и может генерировать профиль пути на основе данных идентификатора пути.

В одном варианте осуществления, как аппаратные, так и программные средства используются для генерирования профиля пути. Модуль идентификатора пути может представлять собой более простой аппаратный компонент, который содержит идентификаторы пути и счетчики для каждого из идентификаторов пути. Модуль определения профиля может представлять собой программный компонент, который идентифицирует области кода для профиля, вставляет легковесные инструкции определения профиля, определяет, как идентификаторы пути и счетчики в модуле идентификатора пути следует обновлять, удалять и/или перезаписывать, и генерирует профиль пути. Это может оставить определение, для каких областей кода следует определять профиль и как определять профиль, для модуля определения профиля, и может привести к возникновению меньших потоков служебных данных, из-за легковесных инструкций определения профиля и простой аппаратной поддержки.

Хотя следующие варианты осуществления могут быть описаны со ссылкой на конкретные интегральные схемы, такие как вычислительные платформы или микропроцессоры, другие варианты осуществления применимы для других типов интегральных схем и логических устройств. Аналогичные технологии и описания вариантов осуществления, описанных здесь, могут применяться для других типов цепей или полупроводниковых устройств. Например, раскрытые варианты осуществления не ограничены настольными компьютерными системами или Ultrabooks™. И также могут использоваться в других устройствах, таких как портативные устройства, планшетные компьютеры, другие тонкие переносные компьютеры, устройства типа системы на микросхеме (SOC), и встраиваемые приложения. Некоторые примеры портативных устройств включают в себя сотовые телефоны, устройства с протоколом Интернет, цифровые камеры, персональные карманные компьютеры (PDA) и портативные ПК. Внедренные приложения обычно включают в себя микроконтроллер, цифровой сигнальный процессор (DSP), систему на микросхеме, сетевые компьютеры (NetPC), телевизионные приставки, сетевые концентраторы, переключатели глобальной сети (WAN) или любую другую систему, которая может выполнять функции и операции, описанные ниже.

Хотя следующие варианты осуществления описаны со ссылкой на процессор, другие варианты осуществления применимы для других типов интегральных цепей и логических устройств. Аналогичные технологии и описания вариантов осуществления настоящего изобретения могут применяться в других типах цепей или в полупроводниковых устройствах, которые могут с пользой применять более высокую пропускную способность конвейера и улучшенные рабочие характеристики. Описания вариантов осуществления настоящего изобретения применимы для любого процессора или устройства, которое выполняет манипулирование с данными. Однако настоящее изобретение не ограничено процессорами или устройствами, которые выполняют операции с данными длиной 512 битов, 256 битов, 128 битов, 64 бита, 32 бита или 16 битов, и могут применяться для любого процессора и устройства, в котором выполняется манипулирование с данными или администрирование данных. Кроме того, в следующем описании представлены примеры, и на приложенных чертежах показаны различные примеры с целью иллюстрации. Однако эти примеры не следует рассматривать в ограничительном смысле, поскольку они просто предназначены для представления примеров вариантов осуществления настоящего изобретения, а не для представления исчерпывающего списка всех возможных воплощений вариантов осуществления настоящего изобретения.

На фиг. 1 показана блок-схема микроархитектуры процессора 200, которая включает в себя логические схемы для выполнения инструкций в соответствии с одним вариантом осуществления настоящего изобретения. В некоторых вариантах осуществления инструкции, в соответствии с одним вариантом осуществления могут быть воплощены для выполнения операций с элементами данных, имеющими размеры байт, слово, двойное слово, учетверенное слово и т.д., а также к типам данных, таким как целые числа одиночной и двойной точности и типы данных с плавающей точкой. В одном варианте осуществления процессор 200 может выполнять модуль определения профиля (например, определения 330 профиля, представленного на фиг. 7). В одном варианте осуществления процессор 200 также может включать в себя модуль идентификатора пути (например, модуль 340 идентификатора пути, показанный на фиг. 7). Например, модуль идентификатора пути может представлять собой часть внешнего интерфейса 201 и/или механизм 203 выполнения команд с изменением порядка их очередности. В одном варианте осуществления внешний интерфейс 201, работающий по порядку, представляет собой часть процессора 200, который производит выборку инструкций для исполнения, и подготавливает их для последующего использования в конвейере процессора. Внешний интерфейс 201 может включать в себя несколько модулей. В одном варианте осуществления блок 226 опережающей выборки инструкции осуществляет выборку инструкций из памяти и подает их в декодер 228 инструкций, который, в свою очередь, декодирует или интерпретирует их. Например, в одном варианте осуществления, декодер декодирует принятую инструкцию в одну или больше операций, называемых "микроинструкциями" или "микрооперациями" (также называются micro op или uop), которые может выполнять устройство. В других вариантах осуществления декодер анализирует инструкцию, разделяя ее на ор код и соответствующие данные, и поля управления, которые используются микроархитектурой для выполнения операций в соответствии с одним вариантом осуществления. В одном варианте осуществления кэш 230 трассы принимает декодированные uop и собирает их в упорядоченные последовательности программы или трассы в очереди 234 uop для выполнения. Когда кэш 230 трассы сталкивается со сложной инструкцией, ROM 232 микрокода предоставляет uop, необходимые для завершения операции.

Некоторые инструкции преобразуют в одиночные micro-op, тогда как для других требуется несколько micro-op для завершения всей операции. В одном варианте осуществления, если больше чем четыре micro-op необходимы для завершения инструкции, декодер 228 обращается к ROM 232 микрокода для выполнения инструкции. В одном варианте осуществления инструкция может быть декодирована на малое количество микроопераций для обработки в декодере 228 инструкции. В другом варианте осуществления инструкция может быть сохранена в ROM 232 микрокода, в случае, когда множество micro-op потребуется для выполнения операции. Кэш 230 трассы обращается к входу в матрицу программируемой логики (PLA) для определения правильного указателя микроинструкции, для считывания последовательности микрокода, для выполнения одной или больше инструкций, в соответствии с одним вариантом осуществления, из ROM 232 микрокода. После того, как ROM 232 микрокода закончит установление последовательности микроопераций для инструкций, внешний интерфейс 201 устройства возобновляет выборку micro-op из кэш 230 трассы.

Механизм 203 выполнения не по порядку используется, когда инструкции подготавливают для выполнения. Логика выполнения не порядку имеет множество буферов для сглаживания и изменения порядка потока инструкций, для оптимизации рабочих характеристик, по мере того, как они выходят из конвейера, и их планируют для выполнения. Логика распределителя распределяет машинные буферы и ресурсы, которые требуются для выполнения каждой из uop. Логика изменения наименования регистра изменяет наименование логических регистров на запись в файле регистра. Распределитель также распределяет запись для каждой uop на одну из двух очередей uop, одна для операций с памятью и одна для операций без привлечения памяти, перед планировщиками инструкции: планировщик памяти, быстрый планировщик 202, медленный/общий планировщик 204 с плавающей точкой и простой планировщик 206 с плавающей точкой. Планировщики 202, 204, 206 uop определяют, когда uop готова для исполнения на основе готовности зависимых от нее источников операнда входного регистра и в зависимости от доступности исполнительных ресурсов, которые требуются uop для выполнения их операций. Быстрый планировщик 202 в одном варианте осуществления может выполнять планирование в течение каждой половины основного цикла тактовой частоты, в то время как другие планировщики выполняют планирования только один раз за цикл тактовой частоты основного процессора. Планировщики определяют порты отправления для планирования uop для выполнения.

Файлы 208, 210 регистра находятся между планировщиками 202, 204, 206, и исполнительными модулями 212, 214, 216, 218, 220, 222, 224 в исполнительном блоке 211. Существует отдельный файл 208, 210 регистра для операций с целыми числами и плавающей точкой, соответственно. Каждый файл 208, 210 регистра, в соответствии с одним вариантом осуществления, также включает в себя обходную сеть, которая позволяет обходить или направлять только что полученные результаты, которые еще не были записаны в файл регистра для новых зависимых uop. Файл 208 регистра для целого числа и файл 210 регистра для плавающей точки также позволяют выполнять обмен данными друг с другом. В одном варианте осуществления файл 208 регистра для целого числа разделяется на два отдельных файла регистра, один файл регистра для 32 битов младшего порядка данных и второй файл регистра для 32 битов старшего порядка данных. Файл 210 регистра с плавающей запятой в одном варианте осуществления имеет входы шириной 128 битов, поскольку инструкции с плавающей точкой обычно имеют операнды шириной от 64 до 128 битов.

Исполнительный блок 211 содержит исполнительные модули 212, 214, 216, 218, 220, 222, 224, где фактически выполняются инструкции. Этот блок включает в себя файлы 208, 210 регистра, которые содержат значения операндов в виде данных целых чисел и с плавающей точкой, которые требуются для выполнения микроинструкций. Процессор 200 в одном варианте осуществления состоит из множества исполнительных модулей: модуль 212 генерирования адресов (AGU), AGU 214, быстрый ALU 216, быстрый ALU 218, медленный ALU 220, ALU 222 с плавающей точкой, модуль 224 перемещения плавающей точки. В одном варианте осуществления исполнительные блоки 222, 224 с плавающей точкой выполняют операции с плавающей точкой, MMX, SIMD и SSE, или другие операции. ALU 222 с плавающей точкой в одном варианте осуществления включают в себя разделитель плавающей точки 64 бита на 64 бита, для выполнения деления, определения квадратного корня и остальных микроопераций. Для вариантов осуществления настоящего изобретения инструкции, обрабатывающие значение с плавающей точкой, могут обрабатываться с использованием аппаратных средств с плавающей точкой. В одном варианте осуществления операции ALU переходят к исполнительным модулям 216, 218 высокоскоростного ALU. Быстрые ALU 216, 218, в одном варианте осуществления, могут выполнять быстрые операции с эффективной задержкой половины цикла тактовой частоты. В одном варианте осуществления наиболее сложные операции со сложными числами выполняются в медленном ALU 220, поскольку медленный ALU 220 включает в себя аппаратные средства для обработки целых чисел в операциях с длительной задержкой, таких как умножитель, сдвиги, логика флагов и обработка разветвлений. Операции загрузки/сохранения в памяти выполняются AGU 212, 214. В одном варианте осуществления ALU 216, 218, 220 для обработки целых чисел описаны в контексте выполнения операций с целыми числами для операндов данных 64 бита. В альтернативных вариантах осуществления ALU 216, 218, 220 могут быть воплощены для поддержки различного количества битов данных, включающих в себя 16, 32, 128, 256 и т.д. битов. Аналогично, модули 222, 224 с плавающей точкой, могут быть воплощены для поддержки определенного диапазона операндов, имеющих различную ширину в битах. В одном варианте осуществления модули 222, 224 с плавающей точкой могут работать с операндам для пакетных данных шириной 128 битов совместно с SIMD и мультимедийными инструкциями.

В одном варианте осуществления планировщики 202, 204, 206 uop вырабатывают зависимые операции перед окончанием обработки из родительской загрузки. Поскольку uop планируют спекулятивно и выполняют в процессоре 200, процессор 200 также включает в себя логику для обработки потерь в памяти. Если загрузка данных теряется в кэш данных, могут существовать зависимые операции, выполняемые в данный момент времени в конвейере, которые оставили в планировщике неправильные по времени данные. Механизм повторной обработки отслеживает и повторно выполняет инструкции, которые используют неправильные данные. Только зависимые операции требуют повторной обработки, и независимые операции могут быть закончены. Планировщики и механизм повторной обработки в одном варианте осуществления процессора также разработаны для захвата последовательности инструкций для операций сравнения текстовой строки.

Термин "регистры" может относиться к местам сохранения для процессора, установленного на борту, которые используются как часть инструкций, для идентификации операндом. Другими словами, регистры могут представлять собой те, которые используются за пределами процессора (с точки зрения программиста). Однако регистры, в соответствии с вариантом осуществления, не должны быть ограничены значением определенного типа цепи. Скорее, регистр, в соответствии с вариантом осуществления, позволяет сохранять и предоставлять данные, и выполнять функции, описанные здесь. Регистры, описанные здесь, могут быть воплощены с использованием схемы в процессоре, используя любое количество разных технологий, таких как специализированные физические регистры, динамически выделенные физические регистры, используя изменение наименования регистра, комбинации выделенных и динамически распределенных физических регистров, и т.д. В одном варианте осуществления регистры для целого числа содержат данные в виде целых чисел длиной тридцать два бита. Файл регистра, в соответствии с одним вариантом осуществления, также содержит восемь мультимедийных регистров SIMD для пакетных данных. Что касается представленного ниже описания, под регистрами также понимают регистры данных, предназначенные для содержания пакетных данных, такие как регистры MMXTM шириной 64 бита (также называются регистрами 'mm' в некоторых случаях) в микропроцессорах, в которых используется технология MMX Intel Corporation Санта-Клара, Калифорния. Эти регистры MMX, доступные как в форме регистров для целого числа, так и для плавающей точки, могут работать с элементами пакетных данных, которые сопровождают инструкции SIMD и SSE. Аналогично регистры XMM шириной 128 битов, относящиеся к технологии SSE2, SSE3, SSE4 или дальше (называется, в общем, "SSEx"), также могут использоваться для содержания таких операндов пакетных данных. В одном варианте осуществления, при сохранении пакетных данных и данных целого числа, регистрам не требуется различать эти два типа данных. В одном варианте осуществления целые числа и числа с плавающей запятой, либо содержатся в одном и том же файле регистра или в разных файлах регистра. Кроме того, в одном варианте осуществления, данные с плавающей запятой и целочисленные данные могут быть сохранены в разных регистрах или в одних и тех же регистрах.

На фиг. 2 показана блок-схема, иллюстрирующая конвейер, работающий по порядку, и этап переименования регистра, конвейер проблемы/выполнения не по порядку, воплощенный устройством 1500 обработки по фиг. 3. На фиг. 2 показана блок-схема, иллюстрирующая ядро архитектуры, работающей по порядку, и логику переименования регистра, логику проблемы/выполнения не по порядку, которая должна быть включена в процессор, в соответствии с, по меньшей мере, одним вариантом осуществления изобретения. Прямоугольники, представленные сплошными линиями на фиг. 2, иллюстрируют конвейер, работающий по порядку, в то время как прямоугольники, показанные пунктирными линиями, иллюстрируют переименование регистров, конвейер проблемы/выполнения не по порядку. Аналогично, прямоугольники, представленные сплошными линиями на фиг. 2, иллюстрируют логику архитектуры, работающей по порядку, в то время, как прямоугольники, представленные пунктирными линиями, иллюстрируют логику переименования регистра и логику проблемы/выполнения не по порядку. На фиг. 2, конвейер 1400 процессора включает в себя этап 1402 выборки, этап 1404 декодирования длины, этап 1406 декодирования, этап 1408 выделения, этап 1410 переименования, этап 1412 планирования (также известный как этап отправки или проблемы), этап 1414 считывания регистра/считывания памяти, исполнительный этап 1416, этап 1418 обратной записи стороны/записи в память, этап 1422 обработки исключения и этап 1424 завершения.

На фиг. 3 показана блок-схема, иллюстрирующая ядро архитектуры, работающей по порядку, и логику переименования регистра, логику проблемы/выполнения не по порядку, которая должна быть включена в процессор, в соответствии с, по меньшей мере, одним вариантом осуществления раскрытия. На фиг. 3 стрелки обозначают соединение между двумя или больше модулями, и направление стрелки обозначает направление потока данных между этими модулями. На фиг. 3 показано ядро 1590 процессора, включающее в себя модуль 1530 внешнего интерфейса, соединенный с модулем 1550 исполнительного механизма, и оба они соединены с модулем 1570 памяти. В одном варианте осуществления данные идентификатора пути (например, в таблице 290, показанной на фиг. 6) могут быть сохранены в модуле 1570 памяти.

Ядро 1590 может представлять собой вычислительное ядро с сокращенным набором команд (RISC), вычислительное ядро со сложным набором команд (CISC), вычислительное ядро со словом инструкции очень большой длины (VLIW), или ядро гибридного или альтернативного типа. В качестве еще другого варианта, ядро 1590 может представляет собой ядро специального назначения, такое как, например, сеть или ядро передачи данных, механизм сжатия, графическое ядро и т.п. В одном варианте осуществления ядро 1590 может выполнять модуль определения профиля (например, модуль 330 определения профиля, представленный на фиг. 7). В другом варианте осуществления модуль идентификатора пути (например, идентификатор 340 пути, показанный на фиг. 7), может быть включен в или может составлять часть ядра 1590. Например, модуль идентификатора пути может представлять собой часть модуль 1530 внешнего интерфейса и/или модуль 1550 исполнительного механизма.

Модуль 1530 внешнего интерфейса включает в себя модуль 1532 прогнозирования ответвления, соединенный с модулем 1534 кэш- инструкции, который соединен с буфером 1536 сохранения трансляции инструкции (TLB), который соединен с модулем 1538 выборки инструкции, который соединен с модулем 1540 декодирования. Модуль декодирования или декодер могут декодировать инструкции и генерировать, в качестве выхода, одну или больше микроопераций, точек входа микрокода, микроинструкций, других инструкций или других сигналов управления, которые декодируют из или которые по-другому отражают, или которые выводят из оригинальных инструкций. Декодер может быть воплощен, используя всевозможные механизмы. Примеры соответствующих механизмов включают в себя, но не ограничены этим, справочные таблицы, аппаратное воплощение, матрицы программируемой логики (PLA), постоянное запоминающее устройство (ROM) микрокода и т.д. Модуль 1534 кэш инструкции дополнительно соединен с модулем 1576 кэш уровня 2 (L2) в модуле 1570 памяти. Модуль 1540 декодирования соединен с модулем 1552 переименования/распределителя в модуле 1550 исполнительного механизма.

Модуль 1550 исполнительного механизма включает в себя модуль 1552 переименования/распределителя, соединенный с модулем 1554 прекращения выполнения инструкции и набор из одного или больше модуля (модулей) 1556 планировщика. Модуль (модули) 1556 планировщика представляет собой любое количество разных планировщиков, включая в себя станции резервирования, окно центральной инструкции и т.д. Модуль (модули) 1556 планировщика соединен с модулем (модулями) файла (файлов) 1558 физического регистра. Каждый из модулей 1558 файла (файлов) физического регистра представляет собой один или больше файлов физического регистра, разные файлы из которых содержат один или больше разных типов данных, таких как скалярное целое число, скалярное число с плавающей точкой, пакетное целое число, пакетное число с плавающей точкой, векторное целое число, векторное число с плавающей точкой и т.д., статус (например, указатель инструкции, который представляет собой адрес следующей инструкции, предназначенной для выполнения), и т.д. Модуль (модули) 1558 файла (файлов) физического регистра частично перекрывается модулем 1554 прекращения инструкции, для иллюстрации различных способов, с помощью которых может быть воплощено переименование регистра и выполнение не по порядку (например, используя буфер (буферы) изменения порядка и файл (файлы) регистра прекращения инструкции, используя будущий файл (файлы), буфер (буферы) предистории, и файл (файлы) регистра прекращения инструкции; использование карты регистров и области регистров; и т.д.). В общем, архитектурные регистры являются видимыми снаружи от процессора или из перспективы программиста. Регистры не ограничены каким-либо известным конкретным типом цепи. Пригодны всевозможные типы регистров, если только они позволяют сохранять и предоставлять данные, как описано здесь. Примеры соответствующих регистров включают в себя, но без ограничений, специализированные физические регистры, динамически выделенные физические регистры с использованием переименования регистра, комбинации специализированных и динамически выделенных физических регистров и т.д. Модуль 1554 прекращения операции инструкции и модуль (модули) 1558 файла (файлов) физического регистра соединены с исполнительным кластером (кластерами) 1560. Исполнительный кластер (кластеры) 1560 включает в себя набор из одного или больше исполнительных модулей 162 и набор из одного или больше модулей 1564 доступа к памяти. Исполнительные модули 1562 могут выполнять различные операции (например, сдвиг, суммирование, вычитание, умножение) и для различных типов данных (например, скалярное число с плавающей точкой, пакетное целое число, пакетное число с плавающей точкой, векторное целое число, векторное число с плавающей точкой). В то время как некоторые варианты осуществления могут включать в себя множество исполнительных модулей, специально выделенных для конкретных функций или наборов функций, другие варианты осуществления могут включать в себя только один исполнительный модуль или множество исполнительных модулей, все из которых выполняют свои функции. Модуль (модули) 1556 планировщика, модуль (модули) 1558 файла (файлов) физического регистра и исполнительный кластер (кластеры) 1560 показаны, как возможно представленные во множественном числе, поскольку в определенных вариантах осуществления формируются отдельные конвейеры для определенных типов данных/операций (например, конвейер для скалярного целого числа, конвейер для скалярного числа с плавающей точкой/пакетного целого числа/пакетного числа с плавающей точкой/векторного целого числа/векторного конвейера с плавающей точкой, и/или конвейер для доступа к памяти, каждый из которых имеет свой собственный модуль планировщика, модуль файла (файлов) физического регистра и/или исполнительный кластер, и, в случае отдельного конвейера доступа к памяти, воплощены определенные варианты осуществления, в которых только исполнительный кластер такого конвейера имеет модуль (модули) 1564 доступа к памяти). Следует также понимать, что в случае, когда используются отдельные конвейеры, один или больше из этих конвейеров могут представлять собой конвейер для проблемы/выполнения не по порядку, а остальные работают по порядку.

Набор модулей 1564 доступа к памяти соединен с модулем 1570 памяти, который включает в себя модуль 1572 TLB данных, соединенный с модулем 1574 кэш-данных, соединенный с модулем 1576 кэш уровня 2 (L2). В одном примерном варианте осуществления модуль 1564 доступа к памяти может включать в себя модуль загрузки, модуль сохранения адреса и модуль сохранения данных, каждый из которых соединен с модулем 1572 TLB данных в модуле 1570 памяти. Модуль 1576 кэш уровня L2 соединен с одним или больше другими уровням кэш и, в конечном итоге, с основной памятью.

В качестве примера, примерное переименование регистра, архитектуру ядра проблемы/выполнения не по порядку может воплощать конвейер 1400 следующим образом: 1) выборка 1538 инструкции выполняет этапы 1402 и 1404 выборки и декодирования длины; 2) модуль 1540 декодирования выполняет этап 1406 декодирования; 3) модуль 1552 переименования/распределения выполняет этап 1408 распределения и этап 1410 переименования; 4) модуль (модули) 1556 планировщика выполняет этап 1412 планирования; 5) модуль (модули) 1558 файла (файлов) физического регистра и модуль 1570 памяти выполняет этап 1414 считывания регистра/считывания памяти; исполнительный кластер 1560 выполняет этап 1416 исполнения; 6) модуль 1570 памяти и модуль (модули) 1558 файла (файлов) физического регистра выполняют этап 1418 обратной записи/записи в память; 7) различные модули могут быть вовлечены в выполнение этапа 1422 обработки исключений; и 8) модуль 1554 прекращения инструкции и модуль (модули) 1558 файла (файлов) физического регистра выполняет этап 1424 завершения.

Ядро 1590 может поддерживать один или больше наборов инструкций (например, набор инструкций х86 (с некоторыми исключениями (??удлинениями), которые были добавлены в более новых версиях); набор инструкций MIPS MIPS Technologies, Саннивейл, Калифорния; набор инструкций ARM (с необязательными дополнительными расширениями, такими как HEOH) разработки ARM Holdings, Саннивейл, Калифорния).

Следует понимать, что ядро может поддерживать многопотоковую обработку (выполнение двух или больше параллельных наборов операций или потоков), и может выполнять ее различными способами, включая в себя слоистую многопотоковую обработку, одновременную многопотоковую обработку (когда одно физическое ядро предусматривает логическое ядро для каждого из потоков, и физическое ядро одновременно выполняет многопотоковую обработку), или их комбинацию (например, выборку с расслоением по времени и декодирование и одновременную многопотоковую обработку, такую как в технологии Intel® Hyperthreading).

В то время как переименование регистра описано в контексте выполнения не по порядку, следует понимать, что переименование регистра может использоваться в архитектуре, работающей по порядку. В то время как представленный вариант осуществления процессора также включает в себя отдельные модули 1534/1574 инструкции и кэш-данных, и модуль 1576 совместно используемой кэш L2, альтернативные варианты осуществления могут иметь один внутренний кэш, как для инструкций, так и для данных, такой как, например, внутренний кэш уровня 1 (LI), или множество уровней внутреннего кэш. В некоторых вариантах осуществления система может включать в себя комбинацию внутреннего кэш и внешнего кэш, который является внешним для ядра и/или процессора. В качестве альтернативы, все кэш могут быть внешними для ядра и/или процессора.

На фиг. 4 показана блок-схема многопроцессорной системы 1300, в соответствии с вариантом осуществления. Как показано на фиг. 4, многопроцессорная система 1300 представляет собой систему взаимного соединения из точки в точку, и включает в себя первый процессор 1370 и второй процессор 1380, соединенные через взаимное соединение 1350 из точки в точку. Каждый из процессоров 1370 и 1380 может представлять собой определенную версию устройства 602 обработки по фиг. 6. Как показано на фиг. 4, каждый из процессоров 1370 и 1380 представляет собой многоядерный процессор, включающий в себя первое и второе ядра процессора (то есть, ядра 1374а и 1374b процессора и ядра 1384а и 1384b процессора), хотя потенциально гораздо больше ядер могут присутствовать в процессорах. Ядро процессора также может называться исполнительным ядром. Каждый процессор может включать в себя гибридную логику режима записи в соответствии с настоящим вариантом осуществления. В одном варианте осуществления один или больше процессоров 1370 и 1380 могут выполнять модуль определения профиля (например, модуль 330 определения профиля, представленный на фиг. 7). В другом варианте осуществления модуль идентификатора пути (например, модуль 340 идентификатора пути, представленный на фиг. 7) может быть включен в или может представлять собой часть одного или больше из процессоров 1370 и 1380.

В то время, как показана схема с двумя процессорами 1370, 1380, следует понимать, что объем настоящего раскрытия не ограничен этим. В других вариантах осуществления один или больше дополнительных процессоров могут присутствовать в данном процессоре.

Показаны процессоры 1370 и 1380, включающие в себя интегрированные модули 1372 и 1382 контроллера памяти, соответственно. Процессор 1370 также включает в себя часть своих интерфейсов 1376 и 1378 модулей контроллера шины из точки в точку (P-P); аналогично, второй процессор 1380 включает в себя интерфейсы 1386 и 1388 Р-Р. Процессоры 1370, 1380 могут выполнять обмен информацией через интерфейс 1350 "из точки в точку" (P-P), используя схемы 1378, 1388 интерфейсов Р-Р. Как показано на фиг. 4, IMC 1372 и 1382 соединяют процессоры с соответствующими запоминающими устройствам, а именно, с памятью 1332