Мультипроцессорная система

Иллюстрации

Показать всеИзобретение относится к области вычислительных и коммуникационных систем и может быть использовано при создании вычислительных комплексов различной производительности. Технический результат заключается в повышении отказоустойчивости и пропускной способности коммуникационной сети за счет использования топологии мульти-тор. Мультипроцессорная система содержит группы вычислительных узлов, каждый узел из которых содержит процессорные элементы и адаптер, соединенные между собой интерфейсом связи, в каждую группу вычислительных узлов дополнительно введен коммуникационный узел, включающий в себя коммутаторы, при этом адаптер каждого вычислительного узла одной группы соединен двунаправленными каналами связи с коммутаторами коммуникационного узла той же группы, при этом все коммутаторы одной группы соединены с соответствующими коммутаторами других групп с образованием многомерных торов. 3 ил.

Реферат

Изобретение относится к области вычислительных и коммуникационных систем и может быть использовано при создании вычислительных комплексов различной производительности.

Известна мультипроцессорная система K-Computer (Fujitsu) (см. http://www.fujitsu.com/downloads/TC/sc10/interconnect-of-k-computer.pdf, http://www.fujitsu.com/downloads/MAG/vo148-3/paper05.pdf), построенная по гибридной топологии, в которой 3-мерные решетки объединяются между собой 3-мерными торами. Такая топология получила название Tofu (от английского TOrus FUsion - объединение торов). В мультипроцессорной системе, построенной по такой топологии, вычислительные узлы объединяются в группы по 12 штук с образованием решетки размерности 2×2×3. При этом измерение, состоящее из трех узлов, дополнительно замкнуто в тор. Таким образом, решетка размерности 2×2×3 может рассматриваться как тор аналогичной размерности. Соответствующие узлы из каждой группы объединены между собой с образованием двенадцати 3-мерных торов.

Вышеуказанное устройство является наиболее близким по технической сущности к заявляемому устройству и поэтому выбрано в качестве прототипа.

Недостатками прототипа являются высокая вероятность возникновения блокировок при деградации коммуникационной сети, предотвращение которых значительно увеличивает сложность маршрутных алгоритмов, а передача сообщений между парой вычислительных узлов осуществляется по одному фиксированному маршруту, что приводит к ограничению пропускной способности.

Решаемой технической задачей является создание масштабируемой мультипроцессорной системы с высокой производительностью и надежностью, которая обеспечивает меньшие затраты на коммуникацию сообщений между вычислительными узлами.

Достигаемым техническим результатом является высокая отказоустойчивость и высокая пропускная способность коммуникационной сети за счет использования топологии мульти-тор.

Для достижения технического результата в мультипроцессорной системе, содержащей группы вычислительных узлов, каждый узел из которых содержит процессорные элементы и адаптер, соединенные между собой интерфейсом связи, новым является то, что в каждую группу вычислительных узлов дополнительно введен коммуникационный узел, включающий в себя коммутаторы, при этом адаптер каждого вычислительного узла одной группы соединен двунаправленными каналами связи с коммутаторами коммуникационного узла той же группы, при этом все коммутаторы одной группы соединены с соответствующими коммутаторами других групп с образованием многомерных торов.

Введение в каждую группу коммуникационного узла позволило осуществлять передачу сообщений между парой вычислительных узлов по нескольким параллельным маршрутам одновременно, что в свою очередь повышает пропускную способность сети. Соединение вычислительных узлов и коммутаторов одной группы по топологии «жирного дерева» не приводит к возникновению блокировок при деградации коммуникационной сети и поэтому значительно упрощает алгоритмы системы маршрутизации.

Использование топологии мульти-тор позволяет сохранить высокую отказоустойчивость и коммуникационные характеристики при масштабировании мультипроцессорной системы.

Новая совокупность существенных признаков позволяет сохранить высокую отказоустойчивость и коммуникационные характеристики при масштабировании мультипроцессорной системы за счет использования топологии мульти-тор.

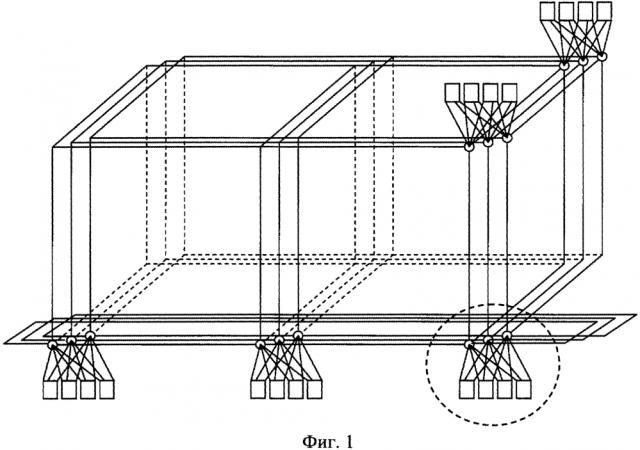

На фигуре 1 представлена блок-схема мультипроцессорной системы, на фигуре 2 - структура одной группы вычислительных узлов.

Мультипроцессорная система содержит группы вычислительных узлов, каждый вычислительный узел от 1.1 до 1.N содержит процессорные элементы от 1.1.1 до 1.N.1 и адаптеры от 1.1.2 до 1.N.2, соединенные между собой интерфейсом связи, вычислительные узлы 1.1…1.N объединены в группы, каждая из которых содержит коммуникационный узел 2, включающий в себя коммутаторы 2.1…2.М, при этом адаптеры 1.1.2…1.N.2 каждого вычислительного узла одной группы соединены двунаправленными каналами связи с коммутаторами 2.1…2.М коммуникационного узла 2 той же группы, все коммутаторы 2.1…2.М одной группы соединены с соответствующими коммутаторами других групп с образованием многомерных торов.

Каждый адаптер 1.1.2…1.N.1 представляет собой плату расширения, подключенную к вычислительному узлу через стандартный интерфейс подключения плат расширения и предназначен для связи вычислительных узлов с коммутаторами коммуникационного узла через M высокопроизводительных портов, что позволяет строить мультипроцессорные системы с числом параллельных торов до М.

Каждый коммутатор 2.1…2.М имеет K+N высокопроизводительных портов и предназначен для передачи сообщений по направлениям топологических связей многомерного тора с максимально возможной производительностью. K портов используются для передачи сообщений по направлениям K/2-мерного, оставшиеся N используются для связи с адаптерами вычислительных узлов.

Базовым элементом топологии мульти-тор является группа вычислительных узлов (см. фиг. 2) с установленными в них адаптерами, объединенными через один уровень коммутации с помощью нескольких коммутаторов.

Каждый коммуникационный узел 2 может содержать от одного до М коммутаторов (количество коммутаторов в коммуникационном узле ограничено количеством портов в адаптере), что обеспечивает функционирование от одной до M подсетей с топологией многомерного тора. Внутри одного коммуникационного узла коммутаторы не соединены между собой и обеспечивают передачу сообщений между коммутаторами, объединенными по топологии многомерного тора. Для этого каждый коммутатор имеет K портов по два для каждого направления: один в направлении увеличения координаты, второй в направлении уменьшения координаты.

К каждому коммутатору 2.1…2.M одного коммуникационного узла подключено до N вычислительных узлов с установленными в них адаптерами 1.1.2…1.N.2. Порты 1, 2…N коммутаторов предназначены для связи с портами 1, 2…M адаптеров. На фигуре 2 показана связь между портами коммутаторов и адаптеров внутри одной группы вычислительных узлов. Порты 1, 2…N коммутатора 2.1, входящего в первую подсеть, подключены к порту 1 всех адаптеров 1.1.2…1.N.2 всех вычислительных узлов, входящих в группу. Порты 1, 2…N второго коммутатора 2.2, входящего во вторую подсеть подключены к порту 2 адаптеров 1.1.2…1.N.2 всех вычислительных узлов, входящих в группу. Соответственно, порты третьего 2.3 и последующего коммутаторов из третьей и последующих подсетей подключены к третьему и последующим портам адаптеров.

Мультипроцессорная система работает следующим образом. Вычислительные узлы объединены между собой топологией мульти-тор. Объединение узлов позволяет программам, которые выполняются на процессорных элементах, обмениваться данными между собой, образуя единое вычислительное поле. От эффективности коммуникации, объединяющей вычислительные узлы, зависит производительность мультипроцессорной системы.

Обмен данными между процессорными элементами осуществляется сообщениями. Каждое сообщение разбивается на пакеты, передающиеся по сети между вычислительными узлами. Каждый передаваемый пакет имеет заголовок, содержащий служебную информацию, в частности адрес источника пакета и адрес получателя пакета, используемые для маршрутизации пакета по сети.

Адрес в сети мульти-тор состоит из двух полей: координатный адрес коммуникационного узла (для трехмерной подсети это X, Y, Z) и номер вычислительного узла в группе (n): X.Y.Z:n.

На фиг. 3 приведен фрагмент сети с топологией мульти-тор третьей степени (три параллельных подсети). Каждая группа содержит по четыре вычислительных узла.

Рассмотрим процесс передачи сообщения от узла с адресом 0.0.0:1 узлу с адресом 0.2.0:2. Передаваемое сообщение разбивается на пакеты адаптерным модулем. Пакеты из сообщения последовательно передаются в порты 1, 2, 3, обеспечивая равномерную загрузку подсетей мульти-тора.

Когда пакет попадает в коммутатор коммуникационного узла, осуществляется его маршрутизация, то есть принятие решения в какой порт перенаправить пакет. Проверяется координатная часть адреса, и если адрес не совпадает, то пакет начинает свое движение в одном из направлений тора: вначале пакет движется по координате X, затем по координате Y и так далее по всем координатам той подсети, по которой пакет начал движении от адаптера. В рассматриваемом примере пакет будет перенаправлен в порт Y+.

При попадании в следующий коммутатор с адресом 0.1.0 при проверке адреса назначения пакет будет перенаправлен далее по направлению Y в направлении увеличения координаты.

В коммутаторе, адрес которого совпадает с координатной частью адреса назначения, пакет маршрутизируется по второму полю адреса - по номеру вычислительного узла n. В рассматриваемом примере пакет будет передан в порт, подключенный к вычислительному узлу с номером 1 в группе.

Когда пакет поступает в адаптер узла назначения, проверяется соответствие адреса назначения пакета и адреса адаптера, и при совпадении пакет передается через интерфейс связи процессорному элементу.

Хотя коммутаторы одного коммуникационного узла не связаны напрямую, но благодаря адаптерам между ними можно передавать пакеты, не занимая топологические порты.

Если на одном из переходов между коммутаторами порт, в который перенаправляется пакет, окажется неисправным, такой пакет передается в один из адаптеров, подключенных к данному коммутатору. Когда в адаптер попадает пакет, координатная часть адреса которого не совпадает с адресом адаптера, пакет перенаправляется в коммутатор из другой подсети, таким образом осуществляется обход неисправных связей, не приводящий к блокировкам в сети.

Такой способ обхода неисправностей не требует усложнения коммутаторов и адаптеров в виде дополнительных виртуальных каналов, так как переход между подсетями только увеличивает длину маршрута на два транзитных участка, но не создает дополнительных циклов (замкнутых путей). Возможность перехода из одной подсети в другую позволяет обойти множественные неисправности оборудования, что повышает надежность коммуникационной сети с топологией мульти-тор.

Описанная выше топология мультипроцессорной системы прошла проверку в составе вычислительного комплекса, построенного на коммуникационной системе СМПО-10G-1. Аппаратная составляющая коммуникационной системы СМПО-10G-1 включает в себя адаптерный блок СМПО-10GA-AD и коммутаторный блок СМПО-10GA-SW.

Адаптерный блок СМПО-10GA-AD (адаптер) представляет собой плату расширения PCI Express 8х Gen 2. Для подключения адаптера к коммуникационному узлу предусмотрено четыре высокоскоростных последовательных порта стандарта QSFP с производительностью 20 Гбит/с.

Коммутаторный блок СМПО-10GA-SW (коммутатор) содержит десять последовательных высокоскоростных портов стандарта QSFP. Шесть портов с производительностью 40 Гбит/с используются для связи с другими коммутаторами с образованием трехмерного тора. Четыре высокоскоростных последовательных порта с производительностью 20 Гбит/с используются для организации связи с адаптерами.

На базе коммуникационной системы СМПО-10G-1 была построена мультипроцессорная система, содержащая 64 вычислительных узла, объединенных в группы по четыре узла. Каждый коммуникационный узел в группе состоит из трех коммутаторов, что позволило реализовать топологию мульти-тор третьей степени. Испытания и замеры производительности, произведенные на вычислительной системе, показали ее высокую производительность и эффективность.

Искусственная деградация коммуникационной системы не привела к блокировкам во время групповых обменов и подтвердила надежность маршрутных алгоритмов, применяемых в топологии мульти-тор для обхода как единичных отказов связей, так и для обхода множественных отказов.

Мультипроцессорная система, содержащая группы вычислительных узлов, каждый узел из которых содержит процессорные элементы и адаптер, соединенные между собой интерфейсом связи, отличающаяся тем, что в каждую группу вычислительных узлов дополнительно введен коммуникационный узел, включающий в себя коммутаторы, соединенные между собой через адаптеры вычислительных узлов той же группы, при этом адаптер каждого вычислительного узла одной группы соединен двунаправленными каналами связи по топологии «жирного дерева» с коммутаторами коммуникационного узла той же группы, причем все коммутаторы коммуникационного узла одной группы соединены с соответствующими коммутаторами коммуникационных узлов других групп с образованием параллельных подсетей с топологиями многомерных торов.