Устройство для логарифмирования двоичных чисел

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано для вычисления значений логарифмической функции от двоичного аргумента. Технический результат заключается в обеспечении возможности получения результата логарифмирования двоичных чисел с меньшими погрешностями и повышении достоверности выходных результатов. Технический результат достигается за счет устройства для логарифмирования двоичных чисел, которое содержит регистры старших и младших разрядов аргумента, первый, второй и третий блоки постоянной памяти, блок управления, коммутатор, сумматор, выходной регистр, триггер числа, сдвигатель, блок управления сдвигателем, блоки сравнения, ячейку памяти константы "1", связанную с первым блоком постоянной памяти. 2 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано для вычисления значений логарифмической функции от двоичного аргумента.

Известно цифровое устройство для логарифмирования двоичных чисел [А.с. 593212, СССР, 1977]. Однако данное устройство имеет низкую точность вычисления логарифма.

Наиболее близким техническим решением к предлагаемому является цифровое устройство для логарифмирования двоичных чисел [А.с. 813414, СССР, 1981]. Оно содержит два блока сравнения, причем первый и второй входы первого блока сравнения соединены соответственно со вторыми входами регистра старших разрядов и первого блока памяти, а выход - с третьим входом сумматора, первый и второй входы второго блока сравнения подключены ко вторым выходам соответственно сумматора и третьего блока памяти, а выход - ко второму входу сдвигателя.

Недостатком этого устройства является низкая точность получаемых результатов.

Задачей настоящего изобретения является разработка устройства для логарифмирования двоичных чисел.

Технический результат настоящего изобретения - возможность получения результата с меньшими погрешностями, повышение достоверности выходных результатов.

Технический результат достигается предложенным устройством для логарифмирования двоичных чисел, который содержит регистр старших и регистр младших разрядов аргумента, первый, второй и третий блоки постоянной памяти, блок управления, коммутатор, сумматор, выходной регистр, триггер числа, сдвигатель, блок управления сдвигателем, первый и второй блоки сравнения, причем первый и второй входы первого блока сравнения соединены соответственно с первыми выходами регистра старших разрядов аргумента и первого блока постоянной памяти, а выход - с первым входом сумматора, первый и второй входы второго блока сравнения подключены ко вторым выходам соответственно сумматора и третьего блока постоянной памяти, а выход - ко второму входу сдвигателя, кроме того, выходы блока управления подключены к первому и второму входам коммутатора, третий и четвертый входы которого связаны с выходом второго блока постоянной памяти и выходом сдвигателя соответственно, причем первый, третий и четвертый входы сдвигателя связаны со входом установки логической "1", с выходом третьего блока постоянной памяти и с выходом блока управления сдвигателем соответственно, первый и второй входы которого связаны через триггер числа с третьим выходом сумматора и напрямую с выходом регистра младших разрядов аргумента, связанного также со вторым блоком постоянной памяти, а выходы первого блока постоянной памяти и коммутатора соединены со вторым и третьим входами сумматора, кроме того, вход третьего блока постоянной памяти соединен с первым выходом сумматора и со входом выходного регистра.

Введение в него дополнительно ячейки памяти константы "1", связанной с входом первого блока памяти, позволит увеличить точность вычисления логарифма двоичных чисел.

Это является новым техническим решением в технике цифровых вычислений логарифма, поскольку результаты проведенного заявителем анализа аналогов и прототипа не позволили выявить признаки, тождественные всем существенным признакам данного изобретения.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность блоков, узлов и связей между ними позволяют повысить достоверность (информативность) выходного результата.

Предложенное устройство для вычисления функций промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических схем).

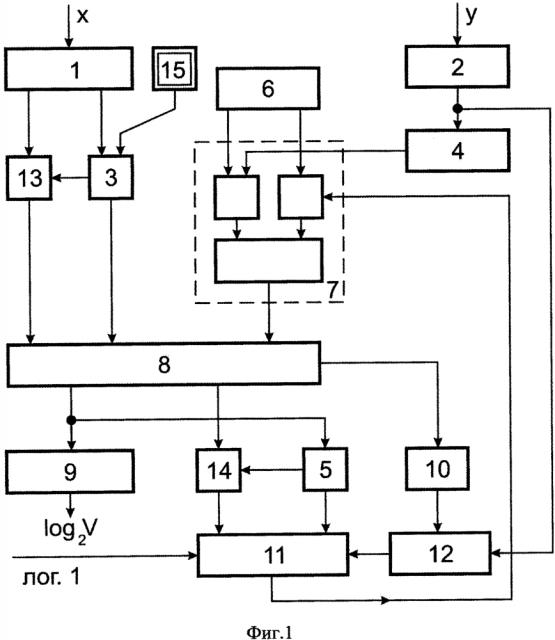

На фиг. 1 представлена блок-схема устройства, а на фиг. 2 - графические данные о точности его работы в сравнении с прототипом.

Устройство содержит регистры старших 1 и младших 2 разрядов аргумента, блоки 3-5 постоянной памяти, блок 6 управления, коммутатор 7, сумматор 8, выходной регистр 9, триггер 10 числа, сдвигатель 11, блок 12 управления сдвигателем, блоки 13 и 14 сравнения, кроме того оно содержит ячейку 15 памяти константы "1", связанную со входом первого блока 3 памяти.

Вычисление двоичного логарифма от нормализованного аргумента V (0,5≤V<1) производится в предлагаемом устройстве на основе соотношений

где x - число, образованное k старшими разрядами аргумента V;

y - число, образованное (N-k) младшими разрядами аргумента V;

N - число двоичных разрядов в аргументе V.

причем

где Δ (x) - функция абсолютной погрешности аппроксимации логарифма прямой линией.

Заметим, что при k=4, а с абсолютной погрешностью менее 2-4.

Пусть

где α - значение разности логарифмов, p - целая часть числа, А - дробная часть числа.

Обозначим

Пусть

,

где n - число двоичных разрядов, необходимых для записи числа β, Δ(β) - функция, итоговой абсолютной погрешности аппроксимации функции прямой.

Заметим, что , а с погрешностью менее 2-4 (при k=4).

Устройство работает следующим образом. На первом этапе входные данные поступают на регистры старших 1 (x) и младших 2 (y) разрядов аргумента. Кроме того, к старшей части x добавляется "1" со стороны ее младших разрядов от ячейки 15 памяти константы "1". От этих регистров 1 и 2 их содержимое (с учетом добавленной "1" в (k+1)-й разряд значения x) передается, соответственно, на входы первого 3 и второго 4 блоков постоянной памяти, где хранятся таблицы мантисс логарифмов старших и младших разрядов аргумента. В таблице, хранящейся в первом 3 блоке постоянной памяти, отсутствуют два старших разряда значений мантисс логарифмов. Значения второго, третьего и четвертого разрядов аргумента поступают на вход блока 13 сравнения, состоящего из элемента ИЛИ и сумматора, осуществляющего сложение числа, образованного вторым, третьим и четвертым разрядами аргумента с кодом 001, если значение четвертого разряда регистра 1 старших разрядов аргумента не совпадает со значением, поступающим с выхода старшего разряда первого 3 блока постоянной памяти. В противном случае происходит сложение с нулем, не изменяющее входного числа. Блок 13 сравнения работает следующим образом. При несовпадении инверсивного значения четвертого разряда регистра 1 старших разрядов аргумента с значением старшего разряда числа, выбранного из первого 3 блока постоянной памяти, происходит увеличение на единицу числа, представленного инверсивным значением второго, третьего и четвертого разрядов аргумента. На выходе блока 13 сравнения получаем два разряда логарифма, образованные двумя старшими разрядами суммы, вычисленной блоком 13 сравнения. С выхода блока 3 постоянной памяти снимаются значения мантиссы log2x с отсутствующими двумя старшими разрядами. С выхода блока 4 постоянной памяти снимается значение мантиссы . Мантиссы логарифмов поступают на входы сумматора 8, причем содержимое на выходе 4 блока постоянной памяти, равное мантиссе , проходит через управляемый коммутатор 7, подключающий в этом такте ко входу сумматора 8 выход блока 4. На выходе сумматора 8 формируется согласно формулам значение β, которое передается на вход третьего 5 блока постоянной памяти, где хранится таблица функции 2β с отсутствующими тремя старшими разрядами значений функции. Три старших разряда суммы с выхода сумматора 8 поступают на вход блока 14 сравнения, состоящего из элемента ИЛИ и сумматора. Значение на выходе старшего разряда блока 5 постоянной памяти также поступает на вход блока 14 сравнения, который осуществляет сложение кода 111 с числом, образованным инверсией трех старших разрядов суммы, поступающих с выхода сумматора 8, в случае, если значение старшего разряда числа, выбранного из блока 5 постоянной памяти, не совпадает со значением инверсии третьего разряда суммы, поступающей из сумматора 8. В противном случае происходит сложение числа, образованного инверсией трех старших разрядов суммы, поступающей с выхода сумматора 8, с нулем, не изменяющее значение этой инверсии. На выходе блока 14 сравнения получаем значение второго и третьего разряда функции 2β, образованные двумя старшими разрядами суммы, полученной блоком 14 сравнения. С выхода блока 5 постоянной памяти снимаются значения функции 2β с отсутствующими тремя старшими разрядами. Таким образом, на выходе блоков 14 и 5 образуется значение функции 2β с отсутствующим старшим разрядом. Значение старшего разряда функции 2β принимается равным логической единице в силу выполнения неравенства для z. Значение функции z=2β поступает на вход сдвигателя 11. Значение знакового разряда сумматора 8 запоминается на триггер 10. Блок 12 управления сдвигателем 11 представляет собой комбинационную схему, подсчитывающую число нулевых разрядов слева до первого единичного разряда в регистре 2 младших разрядов аргумента и суммирующую это число со значением триггера 10, что дает значение требуемого числа сдвигов Р или Р+1 в сдвигателе 11 для получения на его выходе значения 2α из поступающего на вход сдвигателя значения 2β. Образованное на выходе сдвигателя число 2α через управляемый коммутатор 7, подключающий на втором этапе работы устройства ко входу сумматора 8 выходы сдвигателя 11, подается на сумматор 8, где происходит сложение значений 2α и поступающего на другие входы сумматора значения log2x с выхода первого 3 блока памяти и блока 13 сравнения. В результате сложения на сумматоре происходит формирование по исходной формуле значения мантиссы log2V, которое передается на вход выходного регистра 9. Таким образом, предлагаемое устройство преобразует нормализованное значение аргумента V в значение мантиссы log2V.

Благодаря конкатенации "1" из ячейки 25 памяти константы "1" к старшей части (x) аргумента изменяется процесс формирования величины log2x, приводящий к более точной аппроксимации логарифма прямой линией (см формула (6)) в сравнении с аналогичной формулой у прототипа.

На фиг. 2 графически представлены погрешности прототипа и заявленного устройства относительно теоретических значений логарифма по основанию 2.

Устройство для логарифмирования двоичных чисел, содержащее регистр старших и регистр младших разрядов аргумента, первый, второй и третий блоки постоянной памяти, блок управления, коммутатор, сумматор, выходной регистр, триггер числа, сдвигатель, блок управления сдвигателем, первый и второй блоки сравнения, причем первый и второй входы первого блока сравнения соединены соответственно с первыми выходами регистра старших разрядов аргумента и первого блока постоянной памяти, а выход - с первым входом сумматора, первый и второй входы второго блока сравнения подключены ко вторым выходам соответственно сумматора и третьего блока постоянной памяти, а выход - ко второму входу сдвигателя, кроме того, выходы блока управления подключены к первому и второму входам коммутатора, третий и четвертый входы которого связаны с выходом второго блока постоянной памяти и выходом сдвигателя соответственно, причем первый, третий и четвертый входы сдвигателя связаны со входом установки логической "1", с выходом третьего блока постоянной памяти и с выходом блока управления сдвигателем соответственно, первый и второй входы которого связаны через триггер числа с третьим выходом сумматора и напрямую с выходом регистра младших разрядов аргумента, связанного также со вторым блоком постоянной памяти, а выходы первого блока постоянной памяти и коммутатора соединены со вторым и третьим входами сумматора, кроме того, вход третьего блока постоянной памяти соединен с первым выходом сумматора и со входом выходного регистра, отличающееся тем, что дополнительно содержит ячейку памяти константы "1", связанную с входом первого блока постоянной памяти.