Способ измерения временного интервала и варианты устройства его реализующего

Иллюстрации

Показать всеИзобретение относится к области радиоизмерений и может быть использовано при построении цифровых измерителей временных параметров периодических последовательностей импульсов. Технический результат, достигаемый при использовании настоящего изобретения, состоит, главным образом, в расширении функциональных возможностей способа и соответственно устройств его реализующих, за счет снижения погрешности измерений в условиях, когда усреднение классическим способом к повышению точности не приводит. Технический результат достигается, главным образом, за счет периодического изменения фазы счетных импульсов, заполняющих исследуемый временной интервал из последовательности повторяющихся временных интервалов, и усреднения единичных значений, каждое из которых получено при отличающейся фазе счетных импульсов. Основу устройств, реализующих способ, составляют управляемая линия задержки, счетный и арифметический блоки, а также счетчик, в упрощенном варианте - триггер, управляющий линией задержки. 4 н. и 12 з.п. ф-лы, 8 ил.

Реферат

Изобретение относится к области радиоизмерений и может быть использовано при построении цифровых измерителей временных параметров периодических последовательностей импульсов.

В качестве прототипа выбран способ, который достаточно широко применяется в измерителях временных интервалов различного назначении, см., например [Пат. RU 2224263. Опубл. 20.02.2004], предусматривающий при измерении временного интервала в последовательности из N повторяющихся временных интервалов усреднение N единичных результатов подсчета счетных импульсов, заполнивших N временных интервалов, и умножение полученного значения на период T0 следования счетных импульсов. Операция усреднения позволяет снизить среднеквадратическую погрешность измерений в раз без уменьшения периода Т0. Однако только в том случае, если абсолютные ошибки измерений носят случайный характер и имеют симметричное распределение. При невыполнении этого условия усреднение единичных результатов к повышению точности измерений не приводит, а лишь увеличивает время анализа и усложняет измеритель. Это является существенным недостатком способа, так как нередко по техническим причинам повысить точность измерений каким-либо другим путем, например уменьшением периода T0 следования счетных импульсов, не удается. Недостаток способа - ограниченные функциональные возможности.

Устройство, реализующее способ-прототип, содержит счетный и арифметический блоки, выход арифметического блока является выходом устройства, выход счетного блока соединен с первым информационным входом арифметического блока, информационный вход счетного блока является информационным входом устройства, второй информационный вход арифметического блока служит для получения информации о количестве усредняемых временных интервалов [Пат. RU 2224263. Опубл. 20.02.2004].

Недостаток устройства - ограниченные функциональные возможности - обусловлен особенностями способа.

Технический результат, достигаемый при использовании настоящего изобретения, состоит, главным образом, в расширении функциональных возможностей способа, за счет снижения погрешности измерений в условиях, когда усреднение классическим способом к повышению точности не приводит.

Технический результат достигается тем, что в способе измерения временного интервала в последовательности из N повторяющихся временных интервалов, согласно которому оценку временного интервала находят путем усреднения N единичных результатов подсчета счетных импульсов, заполнивших N временных интервалов и умноженных на период T0 следования счетных импульсов, согласно изобретению по окончании каждого временного интервала изменяют фазу последовательности счетных импульсов при сохранении неизменным периода следования счетных импульсов в границах каждого временного интервала.

Для достижения технического результата по первому варианту в устройство, содержащее счетный и арифметический блоки, выход арифметического блока является выходом устройства, выход счетного блока соединен с первым информационным входом арифметического блока, информационный вход счетного блока является информационным входом устройства, согласно изобретению введены управляемая линия задержки и счетчик, выход линии задержки соединен с тактовым входом счетного блока, а управляющий вход - с выходом счетчика, вход линии задержки составляет тактовый вход устройства, суммирующий вход счетчика подключен к информационному входу устройства, к которому также подключен второй информационный вход арифметического блока.

Для достижения технического результата по второму варианту в устройство, содержащее счетный и арифметический блоки, выход арифметического блока является выходом устройства, выход счетного блока соединен с первым информационным входом арифметического блока, информационный вход счетного блока является информационным входом устройства, согласно изобретению введены управляемая линия задержки и T-триггер, выход линии задержки соединен с тактовым входом счетного блока, а управлящий вход - с выходом T-триггера, вход линии задержки составляет тактовый вход устройства, вход T-триггера подключен к информационному входу устройства, к которому также подключен второй информационный вход арифметического блока.

Для достижения технического результата по третьему варианту в устройство, содержащее элемент И, счетчик и арифметический блок, выход которого является выходом устройства, выход счетчика соединен с первым информационным входом арифметического блока, суммирующий вход счетчика соединен с выходом элемента И, первый вход которого является информационным входом устройства, согласно изобретению введены мультиплексор, инвертор и T-триггер, выход которого соединен с адресным входом мультиплексора, выход которого соединен со вторым входом элемента И, первый канальный вход мультиплексора объединен со входом инвертора и является тактовым входом устройства, второй канальный вход мультиплексора соединен с выходом инвертора, тактовый вход T-триггера объединен со вторым информационным входом арифметического блока и подключен к информационному входу устройства.

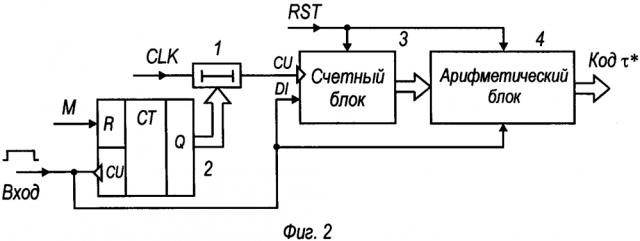

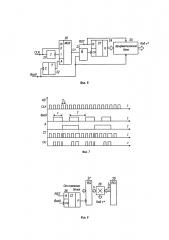

Сущность изобретения поясняется графическим материалом. На фиг. 1 показаны временные диаграммы, поясняющие суть заявленного способа. На фиг. 2 представлена обобщенная функциональная схема устройства, реализующего заявленный способ. На фиг. 3 представлена функциональная схема устройства, согласно п. 4 и п. 5 формулы изобретения, на фиг. 4 - функциональная схема устройства, согласно п. 4 и п. 8 формулы изобретения, на фиг. 5 - функциональная схема устройства, согласно п. 10 формулы изобретения, на фиг. 6 - функциональная схема устройства, согласно п. 15 формулы изобретения, на фиг. 7 - временные диаграммы, иллюстрирующие работу устройства по фиг. 6, а на фиг. 8 - функциональная схема одного из возможных вариантов построения арифметического блока, предназначенного для применения в вышеуказанных устройствах.

Временные диаграммы (фиг. 1) содержат входной u(t) синусоидальный сигнал с периодом T, преобразуемый в последовательность импульсов S, длительность которых оценивается, а также счетные импульсы CLK, CLK1, CLK2, CLK3 с относительным сдвигом T0/4 и пакеты счетных импульсов ССТ.

Функциональная схема по фиг. 2 содержит управляемую линию 1 задержки, счетчик 2, счетный блок 3 и арифметический блок 4, выход которого является выходом устройства, выход счетного блока 3 соединен с первым информационным входом арифметического блока 4, информационный вход DI счетного блока 3 является информационным входом устройства, вход линии 1 задержки составляет тактовый вход CLK устройства, суммирующий вход счетчика 2 подключен к информационному входу устройства, к которому также подключен второй информационный вход арифметического блока 4, выход линии 1 задержки соединен с тактовым входом CU счетного блока 3, а управляющий вход - с выходом счетчика 2.

Функциональная схема по фиг. 3 содержит управляемую линию 5 задержки, счетчик 6, элемент И 7, счетчик 8 и арифметический блок 9, выход которого является выходом устройства, выход счетчика 8 соединен с первым информационным входом арифметического блока 9, второй информационный вход арифметического блока 9 объединен с первым входом элемента И 7 и суммирующим входом счетчика 6 и является информационным входом устройства, тактовым входом CLK которого является вход линии 5 задержки, управляющий вход которой соединен с выходом счетчика 6, а выход - со вторым входом элемента И 7, выход которого соединен с суммирующим входом счетчика 8. Линия 5 задержки состоит из мультиплексора 10 и последовательно соединенных элементов задержки, образующих группу 11.

Функциональная схема по фиг. 4 содержит управляемую линию 12 задержки, счетчик 13, счетчик 14 и арифметический блок 15, выход которого является выходом устройства, выход счетчика 14 соединен с первым информационным входом арифметического блока 15, второй информационный вход арифметического блока 15 объединен с разрешающим входом счетчика 14 и суммирующим входом счетчика 13 и является информационным входом устройства, тактовым входом CLK которого является вход линии 12 задержки, управляющий вход которой соединен с выходом счетчика 13, а выход - с суммирующим входом счетчика 14.

Функциональная схема по фиг. 5 содержит управляемую линию 16 задержки, T-триггер 17, счетный блок 18 и арифметический блок 19, выход которого является выходом устройства, выход счетного блока 18 соединен с первым информационным входом арифметического блока 19, информационный вход DI счетного блока 18 является информационным входом устройства, вход линии 16 задержки составляет тактовый вход CLK устройства, тактовый вход T-триггера 17 подключен к информационному входу устройства, к которому также подключен второй информационный вход арифметического блока 19, выход линии 16 задержки соединен с тактовым входом CU счетного блока 18, а управляющий вход - с выходом T-триггера 17.

Функциональная схема по фиг. 6 содержит мультиплексор 20, инвертор 21, Т-триггер 22, элемент И 23, счетчик 24 и арифметический блок 25, выход которого является выходом устройства, выход счетчика 24 соединен с первым информационным входом арифметического блока 25, суммирующий вход счетчика 24 соединен с выходом элемента И 23, первый вход которого объединен со вторым информационным входом арифметического блока 25 и тактовым входом T-триггера 22 и является информационным входом устройства, выход T-триггера 22 соединен с адресным входом мультиплексора 20, выход которого соединен со вторым входом элемента И 23, первый канальный вход мультиплексора объединен со входом инвертора 21 и является тактовым входом CLK устройства, второй канальный вход мультиплексора соединен с выходом инвертора 21.

Временные диаграммы (фиг. 7) содержат счетные импульсы CLK, подаваемые на тактовый вход устройства по фиг. 6, информационные импульсы, подаваемые на информационный вход устройства, импульсы А на адресном входе мультиплексора 20, импульсы Сl на выходе мультиплексора 20 и импульсы CU на суммирующем входе счетчика 24.

Функциональная схема арифметического блока по фиг. 8 содержит счетчик 26, регистры 27, 29 и перемножитель 28, выход которого является выходом блока, первым информационным входом которого является информационный вход регистра 27, а вторым информационным входом - суммирующий вход счетчика 26, выход переноса которого соединен с тактовым входом регистра 27, выход которого соединен с первым входом перемножителя 28, второй вход которого соединен с выходом регистра 29.

Для пояснения сути предложенного способа обратимся к примеру, показанному на фиг. 1. Задача состоит в нахождении оценки длительности положительной полуволны синусоидального сигнала по результатам измерения нескольких временных интервалов - длительности информационных импульсов S, полученных путем клиппирования указанного сигнала. Положим, что истинное значение полуволны - τ, период синусоидального сигнала - T, а счетные импульсы CLK следуют с периодом T0. Для двух произвольно выбранных соседних импульсов S, передний фронт первого из которых сформирован в момент tm, а второго - в момент tm+1, несложно, пользуясь временными диаграммами, найти ближайшие к ним счетные импульсы, попавшие в измеряемые интервалы. Смещение Δm первого счетного импульса из первого интервала относительно момента времени tm определяется следующим образом:

а смещение Δm+1 первого счетного импульса из второго интервала относительно момента времени tm+1:

где t0 - момент начала формирования счетных импульсов CLK;

km - порядковый номер первого счетного импульса, попавшего в интервал с началом tm;

km+1 - порядковый номер первого счетного импульса, попавшего в интервал с началом tm+1.

Практический интерес представляет разность смещений Δm и Δm+1:

Для того чтобы выяснить, при каких условиях величина Δ постоянна, достаточно приравнять к нулю правую часть равенства (1). В результате имеем

или

Так как km и km+1 являются целыми числами, то несложно видеть, что величина Δ равна нулю, если отношение периодов также является целым числом (период T должен быть кратен периоду T0 счетных импульсов). Таким образом приходим к выводу, что при отношении периодов , равном целому числу, положение счетных импульсов относительно передних фронтов информационных импульсов является постоянным и не зависит от периода T0. Это значит, что если случайные смещения фронтов информационных импульсов пренебрежимо малы по сравнению с величиной T0, то в каждый из исследуемых временных интервалов попадет одинаковое количество счетных импульсов CLK. Из чего следует, что в этих условиях усреднение единичных результатов подсчета счетных импульсов, заполнивших ряд временных интервалов, оказывается бесполезным: оценка временного интервала не будет зависеть ни от объема усредняемых данных, ни от самого факта наличия или отсутствия операции усреднения. При этом погрешность измерений будет определяться строго периодом T0.

Уменьшение погрешности оценки исследуемого временного интервала в условиях, когда доступна последовательность из N повторяющихся временных интервалов, возможно путем периодического изменения фазы счетных импульсов CLK. Иллюстрируют идею временные диаграммы по фиг. 1. В приведенном примере при τ=2,3T0 и N=4 фаза последовательности счетных импульсов сдвигается после каждого временного интервала на величину T0/4. То есть по окончании первого информационного импульса (первого временного интервала) последовательность счетных импульсов сдвигается относительно исходной последовательности CLK на время T0/4 (образуется последовательность CLK1), по окончании второго - на 2T0/4 (образуется последовательность CLK2), по окончании третьего - на 3T0/4 (образуется последовательность CLK3), по окончании четвертого - на 4T0/4. Последний сдвиг осуществляет возврат последовательности к начальной фазе. Таким образом имеем четыре пакета импульсов ССТ, соответствующих последовательно сменяющимся временным интервалам S и смещенных относительно друг друга на величину T0/4. Из диаграмм (см. фиг. 1) видно, что счетные импульсы размещаются в каждом временном интервале по разному, согласно их фазе, что в результате приводит к их различному количеству. Подсчитав общее число счетных импульсов и вычислив среднее арифметическое исходя из того, что N=4, несложно видеть, что оценкой временного интервала τ является величина 2,5T0, полученная с абсолютной погрешностью 0,2T0. Без фазовой модуляции результатом с одинаковой вероятностью могла бы быть либо величина 2T0, либо 3T0, что привело бы к абсолютной погрешности 0,3T0, либо 0,7T0 соответственно.

Снижение погрешности можно объяснить условным уменьшением дискрета счета. Действительно, накопление за N равных интервалов N пакетов импульсов, сдвинутых относительно друг друга на время T0/N, можно рассматривать как счет импульсов в течение одного временного интервала, но с периодом счета в N раз меньшим, чем период используемой последовательности счетных импульсов. Для этого следует мысленно поместить все пакеты ССТ в один временной интервал τ, с сохранением их положения относительно границ этого интервала. При этом оценку τ* можно представить в виде

где n1, n2, …, nN - количество импульсов, попавших соответственно в 1-й, 2-й и N-й интервалы.

Из записи (2) несложно видеть, что представленный алгоритм с формальной точки зрения эквивалентен счету с дискретом T0/N. Однако следует подчеркнуть, что такая трактовка формулы вычисления среднего арифметического возможна только в том случае, если соблюдаются вышеприведенные условия, касающиеся отношения и периодических фазовых сдвигов последовательности CLK.

Для реализации способа служит устройство (см. фиг. 2), в котором фазовые сдвиги в последовательность CLK вносит линия задержки 1, управляемая счетчиком 2. Последний инкрементирует код на своих разрядных выходах по отрицательным фронтам информационных импульсов, длительность которых является оцениваемым параметром. Коэффициент пересчета счетчика 2 выбирают равным N - количеству вводимых шагов задержки. После каждого информационного импульса, поступающего одновременно на суммирующий вход счетчика 2 и вход DI счетного блока 3, вводимый временной сдвиг увеличивается на величину T0/N, но так как последовательность CLK является периодической, то после каждого N-го информационного импульса фаза последовательности возвращается к прежнему значению. Таким образом реализуется циклическое управление фазой последовательности счетных импульсов CLK, поступающих на тактовый вход CU блока 3, назначением которого является подсчет суммарного количества импульсов, входящих в N пакетов, то есть получение суммы вида n1+n2+…+nN. По окончании счета, после N-го пакета (временного интервала) в арифметическом блоке 4, согласно (2) вычисляется произведение накопленной суммы и кода T0/N, который в частном случае может храниться в арифметическом блоке. Показанная на функциональной схеме (см. фиг. 2) связь арифметического блока со входом устройства необходима для получения арифметическим блоком информации о количестве поступивших информационных импульсов. Вход М предназначен для отключения режима модуляции фазы и перевода устройства в обычный режим усреднения с постоянной фазой, а вход обнуления RST служит для обнуления счетного блока перед каждым новым циклом измерений, состоящим из обработки N смежных временных интервалов.

Как управляемая линия задержки 1, так и счетный блок 3 могут быть построены по различным схемам, в зависимости от особенностей применения устройства и предъявляемых к нему требований. Один из вариантов показан на фиг. 3. Здесь линия задержки реализована на основе линейки последовательно соединенных элементов 11 задержки со временем задержки T0/N, отводы которой подключены к канальным входам мультиплексора 10, служащим для коммутации на выход линии задержки импульсов с выбранного отвода. Управляют коммутацией по адресному входу мультиплексора. Что же касается счетного блока, то он показан в классическом исполнении содержащим элемент И 7 и суммирующий счетчик 8. При применении счетчика с разрешающим входом от элемента И можно отказаться, подавая информационные импульсы на разрешающий вход, как показано на фиг. 4. Такое решение позволит обеспечить счет строго по передним фронтам счетных импульсов CLK, исключая ситуации, при которых совпадение во времени переднего фронта информационного импульса с вершиной уже появившегося счетного импульса приводит к укорочению последнего на выходе элемента И и сужению по этой причине первого тактового интервала.

Немалый интерес представляет реализация заявленного способа при N=2. Снижение количества фазовых сдвигов до двух позволит упростить устройство как за счет существенного упрощения линии задержки, так и за счет замены счетчика, управляющего линией задержки, на T-триггер. Это несложно видеть из схемы, показанной на фиг. 5. T-триггер 17, переключаясь по отрицательным фронтам информационных импульсов, управляет линией 16 задержки, вводя таким образом с периодом 2T в последовательность CLK временной сдвиг, равный T0/2. Назначения блоков 18 и 19 те же, что и в ранее рассмотренных устройствах. При тактировании устройства последовательностью импульсов CLK со скважностью равной двум, операция задержки сигнала на полпериода эквивалентна операции инвертирования. Следовательно, функции управляемой линии задержки может выполнять совокупность инвертора с двухканальным мультиплексором, как показано на фиг. 6. Иллюстрируют работу указанного варианта устройства временные диаграммы по фиг. 7, из которых видно, что мультиплексор 20, переключаясь с периодом 2T под действием импульсов А с выхода T-триггера 22 с тем же периодом, меняет фазу последовательности счетных импульсов CLK, образуя таким образом последовательность С1 (см. фиг. 7), подаваемую через элемент И 23 на суммирующий вход CU счетчика 24.

Заметим, что получение оценки согласно (2) не исключает классическую операцию усреднения отдельных результатов. При необходимости введения дополнительного усреднения процедура измерений будет состоять из нескольких циклов, каждый из которых математически определяется выражением (2), а оценкой τ** будет являться величина

где р - порядковый номер цикла (р=1, 2, 3, … Р);

Р - количество циклов;

np1 - количество импульсов, попавших в 1-й временной интервал во время р-го цикла, np2 - количество импульсов попавших во 2-й временной интервал во время р-го цикла и т.д., npN - количество импульсов, попавших в N-й временной интервал во время р-го цикла.

Например, для последнего из рассмотренных вариантов реализации способа, когда N=2, если допустить, что проводится усреднение по пяти циклам, которые можно рассматривать как отдельные результаты, подлежащие усреднению, то есть Р=5, алгоритм (3) примет вид

В приведенной записи множитель перед знаком суммы представлен в виде двух дробей сугубо в иллюстративных целях.

Для введения операции усреднения нет необходимости использовать дополнительные аппаратурные ресурсы, достаточно произвести соответствующую настройку арифметического блока. В качестве примера можно привести схему арифметического блока, представленную на фиг. 8. Счетчик 26 в указанной схеме подсчитывает количество информационных импульсов (временных интервалов), поступивших на вход устройства, и определяет таким образом момент записи в регистр 27 суммы соответствующей правой части (2) или (3). После чего в перемножителе 28 вычисляется произведение указанной суммы и величины T0/N или , в случае введения дополнительной операции усреднения. Для хранения последних служит регистр 29. Таким образом, включение операции усреднения заключается в выборе коэффициента пересчета счетчика 26, соответствующего величине NP и записи кода в регистр 29.

1. Способ измерения временного интервала в последовательности из N повторяющихся временных интервалов, согласно которому оценку временного интервала находят путем усреднения N единичных результатов подсчета счетных импульсов, заполнивших N временных интервалов и умноженных на период T0 следования счетных импульсов, отличающийся тем, что по окончании каждого временного интервала изменяют фазу последовательности счетных импульсов при сохранении неизменным периода следования счетных импульсов в границах каждого временного интервала.

2. Способ по п. 1, отличающийся тем, что фазу последовательности счетных импульсов, следующих с периодом T0, изменяют путем сдвига импульсов на величину, равную T0/N.

3. Способ по п. 1, отличающийся тем, что при N=2 и скважности последовательности счетных импульсов равной двум фазу последовательности счетных импульсов изменяют путем инвертирования счетных импульсов.

4. Устройство, реализующее способ по п. 1, содержащее счетный и арифметический блоки, выход арифметического блока является выходом устройства, выход счетного блока соединен с первым информационным входом арифметического блока, информационный вход счетного блока является информационным входом устройства, отличающееся тем, что в него введены управляемая линия задержки и счетчик, выход линии задержки соединен с тактовым входом счетного блока, а управляющий вход - с выходом счетчика, вход линии задержки составляет тактовый вход устройства, суммирующий вход счетчика подключен к информационному входу устройства, к которому также подключен второй информационный вход арифметического блока.

5. Устройство по п. 4, отличающееся тем, что управляемая линия задержки представляет собой группу последовательно соединенных элементов задержки и мультиплексор, к канальным входам которого, кроме первого, подключены выходы элементов задержки, выход мультиплексора является выходом линии задержки, управляющим входом которой служит адресный вход мультиплексора, входом линии задержки является вход первого элемента задержки из группы, объединенный с первым канальным входом мультиплексора.

6. Устройство по п. 4, отличающееся тем, что арифметический блок служит для умножения кода с выхода счетного блока на код периода T0 следования счетных импульсов и деления на величину, задаваемую количеством N единичных результатов подсчета счетных импульсов, заполнивших N временных интервалов.

7. Устройство по п. 4, отличающееся тем, что счетный блок содержит элемент И и счетчик, выход которого является выходом блока, суммирующий вход счетчика соединен с выходом элемента И, входы которого являются входами блока.

8. Устройство по п. 4, отличающееся тем, что счетный блок содержит счетчик с разрешающим входом, который является первым входом блока, вторым входом которого служит суммирующий вход счетчика, выход которого является выходом блока.

9. Устройство по п. 4, отличающееся тем, что счетчик имеет вход асинхронного обнуления, который используется для перевода устройства в режим работы без модуляции фазы.

10. Устройство, реализующее способ по п. 1, содержащее счетный и арифметический блоки, выход арифметического блока является выходом устройства, выход счетного блока соединен с первым информационным входом арифметического блока, информационный вход счетного блока является информационным входом устройства, отличающееся тем, что в него введены управляемая линия задержки и T-триггер, выход линии задержки соединен с тактовым входом счетного блока, а управлящий вход - с выходом T-триггера, вход линии задержки составляет тактовый вход устройства, вход T-триггера подключен к информационному входу устройства, к которому также подключен второй информационный вход арифметического блока.

11. Устройство по п. 10, отличающееся тем, что линия задержки вносит задержку, равную половине периода следования счетных импульсов, подаваемых на тактовый вход устройства.

12. Устройство по п. 10, отличающееся тем, что арифметический блок служит для умножения кода с выхода счетного блока на код периода T0 следования счетных импульсов и деления на величину, задаваемую количеством N единичных результатов подсчета счетных импульсов, заполнивших N временных интервалов.

13. Устройство по п. 10, отличающееся тем, что счетный блок содержит элемент И и счетчик, выход которого является выходом блока, суммирующий вход счетчика соединен с выходом элемента И, входы которого являются входами блока.

14. Устройство по п. 10, отличающееся тем, что счетный блок содержит счетчик с разрешающим входом, который является первым входом блока, вторым входом которого служит суммирующий вход счетчика, выход которого является выходом блока.

15. Устройство, реализующее способ по п. 1, содержащее элемент И, счетчик и арифметический блок, выход которого является выходом устройства, выход счетчика соединен с первым информационным входом арифметического блока, суммирующий вход счетчика соединен с выходом элемента И, первый вход которого является информационным входом устройства, отличающееся тем, что в него введены мультиплексор, инвертор и Т-триггер, выход которого соединен с адресным входом мультиплексора, выход которого соединен со вторым входом элемента И, первый канальный вход мультиплексора объединен со входом инвертора и является тактовым входом устройства, второй канальный вход мультиплексора соединен с выходом инвертора, тактовый вход T-триггера объединен со вторым информационным входом арифметического блока и подключен к информационному входу устройства.

16. Устройство по п. 15, отличающееся тем, что арифметический блок служит для умножения кода с выхода счетного блока на код периода T0 следования счетных импульсов и деления на величину, задаваемую количеством N единичных результатов подсчета счетных импульсов, заполнивших N временных интервалов.