Электронная система малой мощности, использующая энергонезависимую магнитную память

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в уменьшении потребляемой мощности и времени для считывания и записи. Компьютерная система содержит множество функциональных модулей, причем каждый функциональный модуль содержит функциональный блок и блок магниторезистивной оперативной памяти (MRAM), связанный с функциональным блоком, причем MRAM блок сконфигурирован с возможностью сохранения операционного состояния функционального блока во время состояния ожидания функционального модуля, содержащего этот функциональный блок; при этом компьютерная система сконфигурирована с возможностью переводить один из функциональных модулей в состояние ожидания, когда другой из функциональных модулей находится во включенном состоянии. 2 н. и 13 з.п. ф-лы, 8 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

Настоящее изобретение относится в целом к архитектуре электронной схемы и, более конкретно, к архитектуре системы с малым энергопотреблением, использующей энергонезависимую магнитную память.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

В сегодняшнем управляемом электроникой мире электропитание является ключом для поддержания общества в движении. Однако при увеличивающейся стоимости электропитания спрос на увеличенный срок службы аккумуляторов и проблема потребляемой мощности в электронных устройствах, особенно в портативных устройствах, приобретают первостепенную важность. Когда компьютеры временно не используются, многие используют состояние с пониженным электропитанием, или состояние ожидания, в котором существенно сокращается потребляемая мощность. Портативные устройства, например мобильные телефоны, если они не используются, также обычно переводятся в состояние с пониженным электропитанием, в котором электропитание, или батарея, отсоединяется от многих частей рабочей схемы. Сами электронные компоненты также разрабатывались с пониженными требованиями к мощности электропитания. Если говорить в целом, значительное количество технологий разрабатывалось для сбережения электропитания. Хотя с использованием этих технологий потребляемая мощность была значительно сокращена, разработчики электроники все же обычно испытывают ограничения из-за требований к электропитанию памяти и, в частности, требований к электропитанию памяти, сохраняющей состояние.

Современная электроника обычно проектируется как "просыпающаяся", то есть возобновляющая электропитание при выходе из состояния ожидания (режим ожидания), не теряя какую-либо операционную информацию в памяти при переходе в состояние ожидания. Например, пользователь, который отвечает на телефонный вызов в середине написания письма в текстовом процессоре, может оставить компьютер на достаточно длительное время, чтобы перевести его в режим ожидания. Когда пользователь возвращается, то он может вновь запустить компьютер и немедленно продолжить писать письмо с того же самого места. Точно так же, когда пользователь берет свой телефон, чтобы сделать вызов, телефон обычно запускается из состояния ожидания (если пользователь в данное время не использовал телефон) и оказывается готовым к набору номера и выполнению вызова. Также, если пользователь использует видео, используя процессор цифровых сигналов (DSP) мобильного устройства, и поступает вызов, приводя к нарушению электропитания DSP, пользователь должен иметь возможность возврата к тому же самому состоянию воспроизведения видеозаписи после того, как вызов завершен или проигнорирован. Пользователю не требуется производить начальный запуск устройства и перезагружать информацию с дисковода или другой внешней энергонезависимой памяти в любом из этих примеров. Чтобы достичь этих функциональных возможностей в данный момент, информационное состояние или состояние выполнения приложения обычно сохраняется даже при том, что электронное устройство имеет существенно пониженное электропитание. Электропитание только умеренно снижается, поскольку электропитание все же необходимо для сохранения информации в памяти. Тогда как другие компоненты могут быть полностью остановлены или отключены от электропитания, имеется определенная величина мощности, которая обычно подключена постоянно, чтобы препятствовать потере поддерживаемой в блоках памяти информации.

Множество электронных систем используют статическую оперативную память (SRAM) и динамическую оперативную память (DRAM) из-за их скорости и плотности. Однако и SRAM, и DRAM являются энергозависимой памятью, что означает потерю сохраняемой информации при отключении электропитания. Таким образом, чтобы поддерживать состояние блоков памяти SRAM и DRAM, необходимо поддерживать электропитание. Один из способов избежать этого состояния постоянно подаваемого электропитания заключался в подключении в электронную систему флэш-памяти. Флэш-память представляет собой технологию энергонезависимой памяти, которая может сохранять информацию, когда электропитание отключено. Однако флэш-память обычно слишком медленна, чтобы заменить блоки памяти SRAM и DRAM, и она часто используется как внешняя точка сохранения, чтобы сохранять информацию о состоянии.

На фиг. 1 приведена блок-схема электронной системы 10, иллюстрирующая обычную конфигурацию памяти с использованием энергонезависимой флэш-памяти 106. Система 10 показана с внутренней частью 100 и внешней частью 101. Внешняя часть 101 обычно соединяется с внутренней частью 100 в пределах устройства. Показанные компоненты системы 10 соединяются через шину 102. Блок 103 памяти SRAM предоставляет локальную память для логического блока 104, который включает в себя различные объединенные логические компоненты и схемы-защелки с использованием системной синхронизации. Блок 105 памяти DRAM предоставляется во внешней части 101 для локального, но внешнего для ядра обработки внутренней части 100, большего объема памяти произвольного доступа для системы 10. Система 10 включает в себя также энергонезависимую флэш-память (NVM) 106.

В качестве примера, показанного на фиг. 1, система 10 рассматривается как система для использования в мобильном телефоне. Когда мобильный телефон системы 10 входит в режим ожидания, вся информация о состоянии, сохраняемая в данный момент в SRAM 103 и/или логической схеме 104, перемещается в DRAM 105 в том же самом аппарате. В одном варианте реализации информация о состоянии может быть сохранена во внешней флэш-памяти NVM 106 из DRAM 105. В этом случае информация о состоянии зашифрована, расходуя дополнительное время и энергию.

Таким образом, электропитание от батареи мобильного телефона используется для сканирования SRAM 103 и логической схемы 104 для информации о состоянии и перемещения информации о состоянии в DRAM 105 по шине 102. Дополнительная мощность используется для последующего перемещения информации о состоянии от DRAM 105 по шине 102 во флэш-память NVM 106. Обычно значение потребляемой мощности при передаче данных по шине представляет собой функцию длины шины. Таким образом, расходуется значительная часть мощности батареи, чтобы переместить всю информацию о состоянии. Кроме того, поскольку флэш-память намного медленнее при записи, чем памяти DRAM и SRAM, этот процесс занимает значительное время относительно функционирования мобильного телефона. Это не только электропитание и использование канала во время операции ожидания. Когда мобильный телефон системы 10 использует резервное электропитание, питание батареи снова расходуется, чтобы восстановить информацию о состоянии из флэш-памяти NVM 106 обратно в DRAM 105 (если NVM 106 фактически используется), и в SRAM 103 и логическую схему 104 от DRAM 105. Таким образом, хотя в режиме ожидания система 10 может потреблять меньшую мощность, поскольку электропитание больше не используется для поддержания состояния или в SRAM 103, или в логической схеме 104, значительное количество электроэнергии используется при передаче информации о состоянии на и от DRAM 105 и, возможно, на флэш-память NVM 106, в дополнение к значительному времени, используемому при передаче этой информации назад и вперед.

КРАТКОЕ ИЗЛОЖЕНИЕ СУЩЕСТВА ИЗОБРЕТЕНИЯ

Типичные варианты реализации настоящего раскрытия изобретения относятся к компьютерным системам, включающим в себя, по меньшей мере, один функциональный модуль и блок магниторезистивной оперативной памяти (MRAM), связанный, по меньшей мере, с одним функциональным модулем. Блок MRAM сконфигурирован для сохранения функционального состояния функционального модуля во время состояния пониженного потребления мощности функционального модуля.

Дополнительные типичные варианты реализации настоящего изобретения относятся к способам, включающим в себя этапы, на которых принимают сигнал ожидания, с запросом одного или нескольких функциональных модулей компьютерной системы, для перехода в состояние ожидания, сохраняют, в ответ на прием сигнала ожидания, по меньшей мере, участок текущего операционного состояния функциональных модулей в магнитной оперативной памяти (MRAM), связанной с функциональными модулями, и отключают питание от блока подачи электропитания на функциональные модули после того, как текущее операционное состояние сохранено.

Дополнительные типичные варианты реализации настоящего раскрытия изобретения относятся к системам, которые включают в себя средство приема сигнала ожидания, с запросом одного или нескольких функциональных модулей компьютерной системы на переход в состояние ожидания, средство для сохранения, в ответ на сигнал ожидания, по меньшей мере, участка текущего операционного состояния функциональных модулей в связанной с ними магнитной оперативной памяти (MRAM), и средство для отключения электропитания от функциональных модулей после того, как текущее операционное состояние сохранено. Системы дополнительно включают в себя средство для приема запускающего сигнала, с запросом одного или нескольких функциональных модулей в режиме ожидания на переход в операционный режим, средство для восстановления электропитания функциональных модулей в режиме ожидания в ответ на сигнал запуска и средство для восстановления текущего операционного состояния функциональных модулей.

Выше были отмечены в целом признаки и технические преимущества настоящего изобретения для лучшего понимания нижеследующего подробного описания изобретения. Ниже описываются дополнительные признаки и преимущества изобретения, формирующие предмет формулы изобретения. Специалистам в данной области техники должно быть ясно, что концепция и конкретные раскрытые варианты реализации могут быть легко использованы как основа для модификации или проектирования других структур, реализующих те же цели, что и настоящее изобретение. Специалистам в данной области техники должно быть ясно, что такие эквивалентные конструкции не отступают от сущности и объема изобретения, как это сформулировано в приложенной формуле. Новые признаки, которые характеризуют изобретение, а также организация и способ осуществления, вместе с дополнительными целями и преимуществами, будут лучше поняты из следующего описания при одновременном рассмотрении сопровождающих чертежей. Однако следует ясно осознавать, что каждый из чертежей предоставляется только в целях иллюстрации описания и не означает ограничения настоящего изобретения.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

В дальнейшем изобретение поясняется описанием предпочтительных вариантов воплощения со ссылками на сопроводительные чертежи, на которых:

фиг. 1 изображает блок-схему электронной системы, показывающую конфигурацию обычной памяти с использованием энергозависимой флэш-памяти;

фиг. 2 изображает блок-схему электронной системы, сконфигурированной в соответствии с принципами настоящего изобретения;

фиг. 3 изображает блок-схему другой электронной системы, сконфигурированной в соответствии с принципами настоящего изобретения;

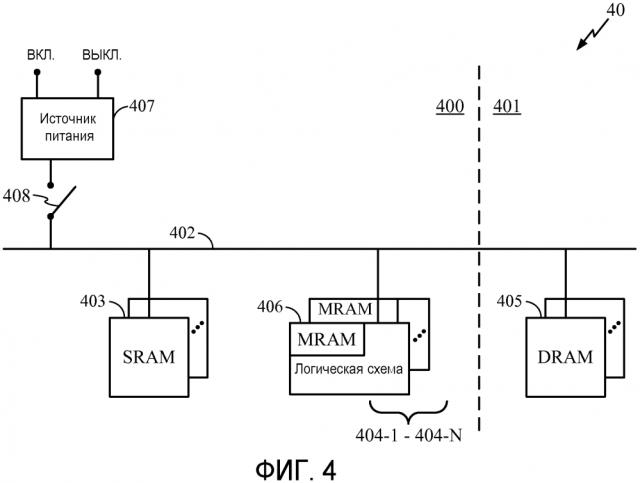

фиг. 4 изображает блок-схему дополнительной электронной системы, сконфигурированной в соответствии с принципами настоящего изобретения;

фиг. 5 изображает блок-схему еще одной дополнительной электронной системы, сконфигурированной в соответствии с принципами настоящего изобретения;

фиг. 6 изображает схематический чертеж, показывающий вид сбоку электронной системы, сконфигурированной в соответствии с принципами настоящего изобретения;

фиг. 7 изображает блок-схему электронной системы, сконфигурированной в соответствии с принципами настоящего изобретения; и

фиг. 8 изображает блок-схему последовательности операций, показывающую примерные блоки, выполняемые, чтобы осуществить различные варианты реализации в соответствии с принципами изобретения.

ОПИСАНИЕ ПРЕДПОЧТИТЕЛЬНЫХ ВАРИАНТОВ ВОПЛОЩЕНИЯ ИЗОБРЕТЕНИЯ

На фиг. 2 показана блок-схема электронной системы 20, сконфигурированной в соответствии с одним вариантом реализации настоящего изобретения. Электронная система 20 имеет внутреннюю часть 200, в которой выполняются операции по обработке, внутренние для функциональных возможностей электронной системы 20 или конкретного свойства, и внешнюю часть 201, которая связана с внутренней частью 200 и предоставляет различные функциональные возможности, например ввод/вывод (I/O), длительную память с произвольным доступом, например блок 205 DRAM, и т.п., которые выполняются или предполагаются выполняемыми, как внешние к внутренней части 200. Электронная система 20 может иметь некоторые внутренние части или функциональные блоки, такие как внутренняя часть 200, предоставляя различные свойства и функциональные возможности.

Электронная система 20 также предоставляет для передачи спинового момента (STT) блок 206 магнитной оперативной памяти (MRAM), который предоставляет внутреннюю энергонезависимую память. Блок 206 STT MRAM использует магнитную полярность, а не сохранение заряда для поддержания ее памяти. Поэтому, когда электропитание 208 отключается от блока 206 STT MRAM, состояние памяти сохраняется, поскольку магнитная полярность поддерживается вне зависимости от электропитания, или электрического заряда, или тока от источника 208 электропитания. Таким образом, когда внутренняя часть 200 переходит в состояние ожидания, информация о состоянии от SRAM 203 и логической схемы 204 сохраняется в блоке 206 STT MRAM. Кроме того, поскольку блок 206 STT MRAM находится в пределах внутренней части 200, потребляемая мощность при передаче данных по шине 202 оказывается меньше, чем потребляемая мощность для электронной системы 10 (фиг. 1). Блок 206 STT MRAM также считывает и записывает намного быстрее, чем внешняя энергонезависимая память, такая как жесткий диск или флэш-память, например, флэш-память NVM 106 электронной системы 10 (фиг. 1). Поэтому еще в большей степени сохраняется мощность, поскольку требуемое для записи информации в блок 206 STT MRAM время оказывается намного меньше.

Как только информация о состоянии перемещается в блок 206 STT MRAM, вся или по существу вся мощность от источника 208 питания может быть отключена от внутренней части 200, поскольку блок 206 STT MRAM не нуждается в электропитании для поддержания своих данных. Когда внутренняя часть 200 питается резервным образом, источник 208 питания восстанавливается, и информация о состоянии перезагружается из блока 206 STT MRAM назад в SRAM 203 и логическую схему 204. Опять-таки из-за более короткого расстояния для перехода на шину 202 и большей скорости, с которой блок 206 STT MRAM считывает и записывает данные, информация о состоянии быстро загружается назад в SRAM 203 и логическую схему 204 так, что обработка приложения может продолжаться, что для пользователя проявляется как намного более быстрая операция, и при этом сохраняется значительная часть мощности питания во время состояния ожидания.

Как рабочая система, электронная система 20 представляет собой мобильный телефон. Внутренняя часть 200 представляет собой мультимедийную часть мобильного телефона. Когда на мобильный телефон поступает вызов в то время, когда пользователь использует мультимедийную часть, эта часть сокращает потребление питания переключением источника 208 питания на внутреннюю часть 200 и переводится в режим ожидания, тогда как пользователь отвечает на запрос. Функциональные возможности телефонии, облегчающие телефонный вызов пользователя, должны осуществляться другой внутренней частью (не показанной) электронной системы 20. Когда вызов завершен, и пользователь хочет возвратиться к своей работе в мультимедийной части, внутренняя часть 200 включается возобновлением работы источника 208 питания, как отмечено выше. При этом в течение периода ожидания фактически не происходит утечки или потребления мощности в пределах внутренней части 200, поскольку электропитание не требуется во время состояния ожидания для блока 206 STT MRAM для поддержания информации о состоянии относительно мультимедийной обработки.

В дополнительном и/или альтернативном варианте реализации настоящего изобретения блок 207 перемещения данных добавляется к внутренней части 200. Блок 207 перемещения данных служит специально для перемещения данных из SRAM 203 в STT MRAM 206. Блок 207 перемещения данных включает в себя список адресов, которые последовательно исполняются при перемещении данных из SRAM 203 на STT MRAM 206 и снова назад. Включение блока 207 перемещения данных позволяет быстрее осуществлять перемещение данных.

На фиг.3 показана блок-схема электронной системы 30, сконфигурированной в соответствии с одним вариантом реализации настоящего раскрытия изобретения. В показанном варианте реализации электронная система 30 содержит цифровой медиа-плейер. Электронная система 30 подобна электронной системе 20 (фиг.2), включающей в себя внутреннюю часть 300, внешнюю часть 301 и шину 302, связывающую каждую из компонент системы. Внутренняя часть 300 включает в себя блок 303 SRAM и блок 306 MRAM. Внешняя часть 301 включает в себя блок 305 DRAM. Электронная система 30 также включает в себя многоядерную логическую схему 304. Многоядерная логическая схема 304 включает в себя множество логических ядер от 304-1 до 304-N, которые выполняют параллельную или совместную обработку данных для электронной системы 30. Внутренняя часть 300 питается от источника 307 питания, который подключается к внутренней части 300 с помощью переключателя 308.

Когда внутренняя часть 300 переключается в состояние ожидания, информация о состоянии, постоянно находящаяся в пределах SRAM 303 и многоядерной логической схеме 304, быстро сохраняется в блоке 306 MRAM. При работе любые конкретные блоки с блоком 306 MRAM могут быть связаны с одним конкретным ядром из логических ядер от 304-1 до 304-N. Опять-таки из-за скорости, с которой элементы MRAM блока 306 MRAM считывают и записывают данные, и более короткой характерной длины шины 302, по которой информация о состоянии распространяется между SRAM 303/многоядерной логической схемой 304 и блоком 306 MRAM, потребляется меньше мощности электропитания при сохранении состояния внутренней части 300, чем в электронной системе 10 (фиг. 1). Как только состояние сохранено, источник 307 питания может быть отключен от внутренней части 300 размыканием переключателя 308 во время состояния ожидания. Таким образом, утечки или потребления мощности во время режима ожидания фактически не происходит. Когда внутренняя часть 300 выходит из режима ожидания, переключатель 308 снова замыкается, восстанавливая электропитание от источника 307 питания. Обратный процесс восстанавливает информацию о состоянии для SRAM 303 и многоядерной логической схемы 304, и внутренняя часть 300 продолжает обработку с той же самой точки, с которой она перешла в режим ожидания.

Варианты реализации на фиг. 2 и 3 демонстрируют использование энергонезависимой магнитной памяти в отдельных компонентах, связанных вместе в одной и той же внутренней части. Однако дополнительные и/или альтернативные варианты реализации настоящего раскрытия изобретения предоставляют вариант, когда энергонезависимые магнитные блоки памяти могут быть объединены на одной и той же кремниевой подложке как логические ядра.

На фиг. 4 показана блок-схема электронной системы 40, сконфигурированной в соответствии с одним вариантом реализации настоящего раскрытия изобретения. В показанном варианте реализации электронная система 40 представляет собой настольный компьютер. Электронная система 40 включает в себя внутреннюю часть 400 и внешнюю часть 401. Внешняя часть 401 включает в себя блок 405 DRAM. Внутренняя часть 400 включает в себя блок 403 SRAM и многоядерную логическую схему 404 и питается от источника 407 питания, связанного с внутренней частью 400 через переключатель 408. Многоядерная логическая схема 404 включает в себя встроенную MRAM 406 в каждом из логических ядер от 404-1 до 404-N. Из-за желательных возможности расширения и совместимости с существующей технологией микросхем MRAM 406 может быть встроена непосредственно в кремниевую подложку многоядерной логической схемы 404 с добавлением всего лишь двух масок. И, напротив, встраивание флэш-памяти в кремниевую подложку логического ядра обычно использует на десять или более дополнительных масок больше, чем число масок, традиционно используемых в производстве других логических схем. В одном варианте реализации, встроенная MRAM 406 разделена по некоторым из логических ядер от 404-1 до 404-N и только фактически встроена в некоторые из этих логических ядер от 404-1 до 404-N.

Со встроенной MRAM 406 потребляемая мощность при передаче информации о состоянии намного меньше, чем требуемая при перемещении всей информации по шине 402. Кроме того, поскольку встроенная MRAM 406 находится на микросхеме, число I/O каналов не ограничивается при перемещении между компонентами вне микросхемы. Таким образом, задержка при передаче данных сокращается, поскольку пропускная способность шины на микросхеме намного выше, чем для шины 402. Когда внутренняя часть 400 входит в состояние ожидания, данные, составляющие текущее операционное состояние, сохраняются на встроенной MRAM 406, и источник 407 питания отключен и изолирован от внутренней части 400 размыканием переключателя 408. Когда внутренняя часть 400 запускается, переключатель 408 замкнут, и источник 407 питания включен и подает питание на компоненты внутренней части 400. Данные для текущего операционного состояния затем восстанавливаются для блока 403 SRAM и многоядерной логической схемы 404. Потребление мощности и время для считывания и записи поэтому сильно сокращаются.

На фиг. 5 показана блок-схема электронной системы 50, сконфигурированной в соответствии с одним вариантом реализации настоящего раскрытия изобретения. Электронная система 50 сконфигурирована, как имеющая одноядерную логическую схему 501, связанную с блоком 500 SRAM по шине 502. Подобно многоядерной логической схеме 404 (фиг. 4) блок 503 MRAM встроен непосредственно в кремниевую подложку одноядерной логической схемы 501. Встраивание MRAM 503 в пределах одноядерной логической схемы 501 предоставляет благоприятное соотношение, как описано в связи с многоядерной логической схемой 404 (фиг. 4). Продолжительность обработки и электропитание сохранены из-за увеличенной пропускной способности средств I/O и увеличенной в результате эффективности при передаче данных на микросхеме. Когда электронная система 50 входит в состояние ожидания, электропитание может быть полностью отключено от электронной системы 50, и состояние будет все же сохраняться в MRAM 503.

Когда компоненты MRAM встроены в подложку основной логической схемы, конфигурация MRAM выполняется относительно основной логической конфигурации, чтобы облегчить встраивание. Блоки MRAM, которые изготовлены в пределах их собственных микросхем, могут быть спроектированы специально так, чтобы оптимизировать работу компонентов MRAM. Таким образом, хотя MRAM, непосредственно встроенные в кремниевую подложку логических компонентов, увеличивают скорость и эффективность любой передачи данных, может быть спроектирована микросхема только с MRAM, которая считывает и записывает намного быстрее и более эффективно, чем встроенная MRAM. Каждый такой вариант реализации будет иметь свои собственные преимущества в зависимости от желаемой для системного проектировщика операции. В одном варианте реализации предоставляются и встроенная MRAM, и автономные блоки MRAM (такие, как на фиг. 3), связанные через шину, чтобы достигнуть преимуществ обеих конфигураций.

На фиг. 6 показан схематический чертеж вида сбоку электронной системы 60, сконфигурированной в соответствии с одним вариантом реализации настоящего раскрытия изобретения. Электронная компонента 60 представляет собой интегральную схему, включающую в себя микросхему 601 MRAM, пакетированную поверх логической микросхемы 600. Микросхема 601 MRAM связана с логической микросхемой 600 с помощью ряда межсхемных соединителей 602, которые содержат прямые кремниевые перемычки (TSV) 603 и соединительные площадки 604 в приведенном варианте реализации. Перемычки TSV 603 позволяют передавать сигналы непосредственно от логической микросхемы 600 на микросхему 601 MRAM. В другом варианте реализации (не показан) MRAM и логические микросхемы, пакетированные в пределах сборки, соединяются с использованием проводных связей вместо TSV. В обоих вариантах реализации сбережение мощности сильно увеличивается по сравнению с потребляемой мощностью при передаче в электронной системе 10 на фиг. 1, передающей данные по шине 102. Как описано в связи с фиг. 2-5, микросхема 601 MRAM способна сохранять свою информацию и поддерживать эту информацию даже при отключенном электропитании. Таким образом, работа электронной системы 60 предусматривает стабильное энергонезависимое сохранение информации от логической микросхемы 600.

Конфигурация пакетированной микросхемы электронной компоненты 60 обеспечивает выполнение операции, подобной объединенной операции MRAM и логических ядер, описанных на фиг. 2-5. Фактически, чтобы создать дополнительные и/или альтернативные варианты реализации, электронная компонента 60 может заменить другие MRAM-логические конфигурации. Например, электронная компонента 60 может заменить логическую схему 204 и STT MRAM 206 на фиг. 2; она может заменить каждый из блоков 306 MRAM и каждое из логических ядер от 304-1 до 304-N на фиг. 3; она может заменить каждое из логических ядер от 404-1 до 404-N и встроенные блоки 406 MRAM на фиг. 4; и она может заменить логическую схему 501 и встроенную MRAM 503 на фиг. 5. Различные варианты реализации настоящего раскрытия изобретения, таким образом, не ограничены какой-либо конкретной конфигурацией блоков MRAM относительно конкретных электронных систем.

Далее, на фиг. 7 показана блок-схема электронной системы 70, сконфигурированной в соответствии с одним вариантом реализации настоящего раскрытия изобретения. Электронная система 70 представляет собой блок 700 многоядерной логической схемы, блок 701 RAM и блок 702 STT MRAM. В варианте реализации электронной системы 70, показанной на фиг. 7, блок 702 STT MRAM используется только для сохранения информации о состоянии для блока 701 RAM. Информация о состоянии в блоке 700 многоядерной логической схемы сохраняется в энергонезависимой памяти в каждой из схем-защелок 703 и 706. Технология, лежащая в основе этой энергонезависимой памяти схемы-защелки, описана очень подробно в принадлежащей тому же правообладателю и также находящейся на рассмотрении патентной заявки с серийным номером XX/XXX, XXX, озаглавленной "ЗАПОМИНАЮЩАЯ СХЕМА-ЗАЩЕЛКА С ЭНЕРГОНЕЗАВИСИМЫМ СОСТОЯНИЕМ", реестр поверенного, номер 80103, раскрытие изобретения которого тем самым полностью включено здесь посредством ссылки.

Блок 700 многоядерной логической схемы включает в себя схемы-защелки 703 и 706, связанные с объединенными логическими блоками 704 и 705. При использовании конфигураций энергонезависимой магнитной памяти, описанной во включенной патентной заявке, для блоков 707 и 708 энергонезависимой памяти, и информация о состоянии, содержащаяся в пределах блока 701 RAM, и информация о состоянии, содержащаяся в пределах блока 700 многоядерной логической схемы, может быть сохранена и удерживаться притом, что электропитание электронной системы 70 отключено. Таким образом, электронная система 70 может перейти в энергосберегающее состояние ожидания, удерживая информацию о состоянии в тот момент, когда пользователь решает «разбудить» систему. Поэтому когда электронная система 70 находится в режиме ожидания, мощность электропитания или мала, или вообще не потребляется и не утекает, поскольку электропитание не требуется для блока 702 STT MRAM или блоков 707 и 708 энергонезависимой памяти в пределах многоядерных логических блоков 700.

На фиг. 8 показана блок-схема последовательности операций с примерными блоками, выполняемыми для осуществления одного варианта реализации настоящего раскрытия изобретения. В блоке 800 принимается сигнал ожидания, с запросом одного или нескольких функциональных модулей компьютерной системы на переход в состояние ожидания. Функциональный модуль представляет собой ряд регистров и объединенную логическую схему, которая выполняет основную функцию. Например, функциональные модули включают в себя целочисленные модули, мультимедийные модули (например, видео-аудио КОДЕР-ДЕКОДЕР) и т.д. В ответ на прием сигнала ожидания, по меньшей мере, участок текущего операционного состояния функциональных модулей сохраняется в блоке 801, в магнитной оперативной памяти (MRAM), связанной с функциональными модулями. Электропитание отключается, в блоке 802, от одного или нескольких функциональных модулей после того, как текущее операционное состояние сохранено. Сигнал запуска принимается в блоке 803 по запросу функционального модуля в режиме ожидания на переход в операционный режим. В ответ на прием сигнала запуска в блоке 804 восстанавливается электропитание от источника питания на функциональные модули в режиме ожидания. Текущее операционное состояние для функциональных модулей восстанавливается в блоке 805.

Следует отметить, что, хотя показанные варианты реализации настоящего раскрытия изобретения были идентифицированы как мобильный телефон, цифровой медиа-плейер и настольный компьютер, различные варианты реализации не ограничены этими воплощениями. Настоящее раскрытие изобретения может использоваться во многих самых различных электронных системах, которые обрабатывают что-либо и имеют состояние обработки, которое может быть поддержано.

В целях этого раскрытия изобретения блок MRAM рассматривается как запоминающий элемент, в котором данные не сохраняются как электрический заряд или протекающие токи, но с помощью магнитных запоминающих элементов. Магнитные элементы обычно формируются из двух ферромагнитных пластин, отделенных тонким изолирующим слоем, каждая из которых может поддерживать магнитное поле. В одном варианте реализации одна из этих двух пластин является постоянным магнитом, установленным с определенной полярностью. Магнитное поле другой пластины может быть сконфигурировано для изменения при согласовании с этим внешним полем. Блок MRAM построен из сетки таких "ячеек".

Притом, что некоторые представленные варианты реализации описаны в связи с магнитной оперативной памятью и более конкретно в связи с магнитной оперативной памятью с передачей спинового момента (STT), описанные признаки могут быть рассмотрены как применяемые также для таких устройств, включающих в себя оперативную память с фазовым кодированием (PCRAM), резистивную оперативную память (R-RAM) или любое устройство, которое может сохранять электрически программируемое состояние резистивной памяти энергонезависимым образом, то есть в отсутствие подачи электропитания, которое является перепрограммируемым для множества состояний, или электрическую, или магнитную, или электромагнитную (например, оптическую), или с комбинацией таких физических эффектов память.

Хотя настоящее изобретение и его преимущества были описаны подробно, следует понимать, что различные вариации, замены и изменения могут быть выполнены, не отступая от существа и объема притязаний изобретения, как это определено в соответствии с приложенной формулой. Например, хотя в предшествующем описании рассматривалась замена памяти некоторых типов, например, DRAM или энергонезависимая RAM, раскрытие изобретения не ограничивается такими вариантами реализации. В действительности участки каждого типа памяти могут быть оставлены, если это необходимо, с заменой на MRAM только определенных участков памяти каждого типа. Кроме того, объем настоящей заявки не предполагает ограничения конкретными вариантами реализации процесса, механизма, производства, состава материалов, средства, способов и этапов, описанных в спецификации. Любому специалисту в данной области техники должно быть ясно из раскрытия настоящего изобретения, что процессы, механизмы, производство, состав материалов, средство, способы или этапы, существующие теперь или разработанные в будущем, которые выполняют по существу ту же самую функцию или достигают по существу того же самого результата, что и описанные здесь соответствующие варианты реализации, могут использоваться в соответствии с настоящим изобретением. Соответственно предполагается, что приложенная формула включает в себя в пределах своего объема притязаний такие процессы, механизмы, производство, составы материалов, средства, способы или этапы.

1. Компьютерная система (20, 30, 40, 50, 60), содержащая:

множество функциональных модулей (200, 300, 400), причем каждый функциональный модуль содержит функциональный блок (204, 304, 404, 501, 700) и блок магниторезистивной оперативной памяти (MRAM) (206, 306, 406, 503, 601, 702), связанный с функциональным блоком, причем MRAM блок сконфигурирован с возможностью сохранения операционного состояния функционального блока (204, 304, 404, 501, 700) во время состояния ожидания функционального модуля, содержащего этот функциональный блок; при этом

компьютерная система сконфигурирована с возможностью переводить один из функциональных модулей в состояние ожидания, когда другой из функциональных модулей находится во включенном состоянии.

2. Компьютерная система (20, 30, 40, 50, 60) по п. 1, дополнительно содержащая:

блок оперативной памяти (RAM), связанный с одним функциональным блоком (204, 304, 404, 501, 700) и блоком MRAM, причем блок RAM сконфигурирован с возможностью сохранять часть операционного состояния одного функционального блока (204, 304, 404, 501, 700) во время состояния с включенным электропитанием указанного одного функционального блока (204, 304, 404, 501, 700), и при этом блок MRAM дополнительно сконфигурирован с возможностью сохранять указанную часть операционного состояния во время состояния ожидания.

3. Компьютерная система (20, 30, 40, 50, 60) по п. 2, дополнительно содержащая:

блок перемещения данных, сконфигурированный с возможностью перемещать часть операционного состояния, расположенный в RAM, в блок MRAM во время состояния ожидания.

4. Компьютерная система (20, 30, 40, 50, 60) по п. 1, в которой блок MRAM представляет собой блок MRAM передачи спинового момента (STT).

5. Компьютерная система (20, 30, 40, 50, 60) по п. 1, в которой операционное состояние содержит множество данных, представляющих операционное состояние функционального блока (204, 304, 404, 501, 700).

6. Компьютерная система (20, 30, 40, 50, 60) по п. 1, в которой блок MRAM содержит STT MRAM микросхему и функциональный блок (204, 304, 404, 501, 700) содержит микросхему функционального блока, и при этом STT MRAM микросхема и микросхема функционального блока уложены в стопку друг на друга, так что микросхема MRAM пакетирована поверх логической микросхемы, и электрически связаны посредством одной или более проводящих контактных площадок.

7. Компьютерная система (20, 30, 40, 50, 60) по п. 1, в которой блок MRAM соединен с функциональным блоком (204, 304, 404, 501, 700) путем заделки в силиконовую подложку функционального блока (204, 304, 404, 501, 700) при изготовлении функционального блока (204, 304, 404, 501, 700).

8. Компьютерная система (20, 30, 40, 50, 60) по п. 1, в которой блок MRAM соединен с функциональным блоком (204, 304, 404, 501, 700) посредством передающей шины компьютерной системы (20, 30, 40, 50, 60).

9. Способ функционирования компьютерной системы, содержащей множество функциональных модулей, содержащий этапы, на которых:

принимают сигнал ожидания, запрашивающий один функциональный модуль (200, 300, 400) компьютерной системы (20, 30, 40, 50, 60), содержащий один функциональный блок (204, 304, 404, 501, 700), на вхождение в состояние ожидания;

в ответ на прием сигнала ожидания сохраняют часть текущего операционного состояния функционального блока (204, 304, 404, 501, 700) в магнитной оперативной памяти (MRAM) в одном функциональном модуле (200, 300, 400), причем (MRAM) соединен с функциональным блоком (204, 304, 404, 501, 700); и

отключают электропитание от одного функционального модуля (200, 300, 400), содержащего функциональный блок (204, 304, 404, 501, 700), после того, как текущее операционное состояние сохранено, когда другой функциональный модуль находится во включенном состоянии.

10. Способ по п. 9, дополнительно содержащий этапы, на которых:

принимают сигнал запуска с запросом функционального блока (204, 304, 404, 501, 700), находящегося в режиме ожидания, на переход в рабочий режим;

в ответ на прием сигнала запуска восстанавливают электропитание функционального блока (204, 304, 404, 501, 700), находящегося в режиме ожидания; и

загружают часть текущего операционного состояния из (MRAM) в функциональный блок (204, 304, 404, 501, 700).

11. Способ по п. 9, в котором на этапе сохранения: