Инструментальный усилитель с повышенным ослаблением входного синфазного сигнала

Иллюстрации

Показать всеИзобретение относится к области измерительной техники и может быть использовано в качестве прецизионного устройства усиления сигналов различных датчиков. Технический результат заключается в повышении коэффициента ослабления входных синфазных сигналов инструментального усилителя. Инструментальный усилитель с повышенным ослаблением входного синфазного сигнала содержит три дифференциальных каскада (3, 8, 13) на транзисторах (1, 2, 6, 7, 11, 12), выходной каскад (20), три вспомогательных транзистора (22-24) и три токостабилизирующих двухполюсника (27, 28, 29), при этом в него дополнительно введены три транзистра (31, 33, 35), три резистора местной отрицательной обратной связи (30, 32, 34) и три токостабилизирующих двухполюсника (36-38). 1 з.п. ф-лы, 7 ил.

Реферат

Изобретение относится к области электроники и измерительной техники и может быть использовано в качестве прецизионного устройства усиления сигналов различных датчиков.

В современной информационно-измерительной технике, приборостроении, датчиковых системах, различных аналого-цифровых интерфейсах находят широкое применение так называемые инструментальные (измерительные) усилители (ИУ), которые обеспечивают прецизионное усиление дифференциального сигнала (ud) и повышенное ослабление синфазной составляющей входных напряжений (uc) [1].

Одним из наиболее перспективных методов построения ИУ является применение в их структуре так называемых мультидифференциальных операционных усилителей (МОУ) [2-4], которые реализуются на основе классических дифференциальных каскадов на полевых [5-22] или биполярных [23-26] транзисторах с резистором местной отрицательной обратной связи. При этом для повышения линейности ИУ резистор местной отрицательной обратной связи выбирается достаточно высокоомным (1-10 кОм), что существенно ухудшает один из важнейших параметров МОУ и ИУ - коэффициент ослабления входного синфазного сигнала (Kос.сф.).

Ближайшим прототипом заявляемого устройства является дифференциальный инструментальный усилитель по А. св. СССР №537435 Института проблем управления РАН. Он содержит (фиг. 1) первый 1 и второй 2 входные полевые транзисторы первого 3 дифференциального каскада, затворы которых соединены с соответствующими первым 4 и вторым 5 входами первого 3 дифференциального каскада, первый 6 и второй 7 входные полевые транзисторы второго 8 дифференциального каскада, затворы которых соединены с соответствующими первым 9 и вторым 10 входами второго 8 дифференциального каскада, первый 11 и второй 12 входные полевые транзисторы третьего 13 дифференциального каскада, затворы которых соединены с соответствующими первым 14 и вторым 15 входами третьего 13 дифференциального каскада, причем первый 14 вход третьего 13 дифференциального каскада связан с источником заданного напряжения 16, а второй 15 вход третьего 13 дифференциального каскада связан с выходом устройства 17 через цепь обратной связи 18, стоки первого 1 входного полевого транзистора первого 3 дифференциального каскада, первого 6 входного полевого транзистора второго 8 дифференциального каскада и первого 11 входного полевого транзистора третьего 13 дифференциального каскада соединены с первым 19 входом выходного каскада 20, выход которого подключен к выходу устройства 17, стоки второго 2 входного полевого транзистора первого 3 дифференциального каскада, второго 7 входного полевого транзистора второго 8 дифференциального каскада и второго 12 входного полевого транзистора третьего 13 дифференциального каскада соединены со вторым 21 входом выходного каскада 20, исток первого 1 входного полевого транзистора первого 3 дифференциального каскада соединен с коллектором первого 22 вспомогательного транзистора, исток первого 6 входного полевого транзистора второго 8 дифференциального каскада соединен с коллектором второго 23 вспомогательного транзистора, исток первого 11 входного полевого транзистора третьего 13 дифференциального каскада соединен с коллектором третьего 24 вспомогательного транзистора, база которого подключена к источнику напряжения смещения 25, эмиттеры первого 22, второго 23 и третьего 24 вспомогательных транзисторов связаны с первой 26 шиной источника питания через соответствующие первый 27, второй 28 и третий 29 токостабилизирующие двухполюсники.

Существенный недостаток известного ИУ состоит в том, что он не обеспечивает высокое ослабление входных синфазных сигналов. В конечном итоге, это снижает прецизионность известного ИУ.

Основная задача предполагаемого изобретения состоит в повышении коэффициента ослабления входных синфазных сигналов ИУ.

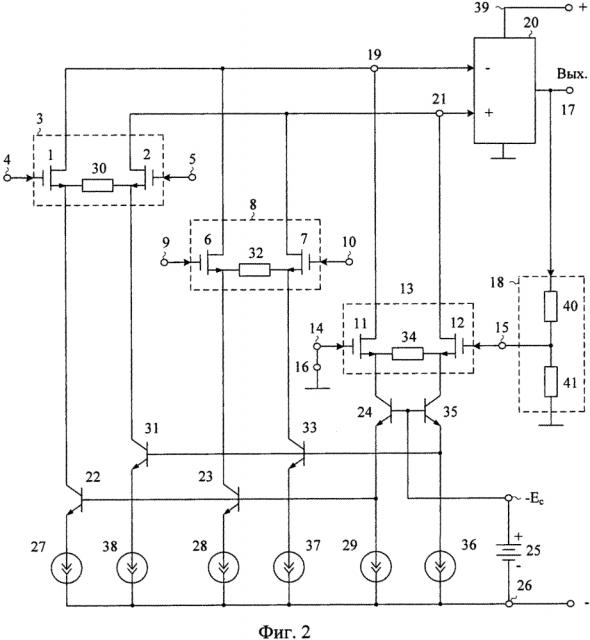

Поставленная задача достигается тем, что в инструментальном усилителе с повышенным ослаблением входного синфазного сигнала, фиг. 1, содержащем первый 1 и второй 2 входные полевые транзисторы первого 3 дифференциального каскада, затворы которых соединены с соответствующими первым 4 и вторым 5 входами первого 3 дифференциального каскада, первый 6 и второй 7 входные полевые транзисторы второго 8 дифференциального каскада, затворы которых соединены с соответствующими первым 9 и вторым 10 входами второго 8 дифференциального каскада, первый 11 и второй 12 входные полевые транзисторы третьего 13 дифференциального каскада, затворы которых соединены с соответствующими первым 14 и вторым 15 входами третьего 13 дифференциального каскада, причем первый 14 вход третьего 13 дифференциального каскада связан с источником заданного напряжения 16, а второй 15 вход третьего 13 дифференциального каскада связан с выходом устройства 17 через цепь обратной связи 18, стоки первого 1 входного полевого транзистора первого 3 дифференциального каскада, первого 6 входного полевого транзистора второго 8 дифференциального каскада и первого 11 входного полевого транзистора третьего 13 дифференциального каскада соединены с первым 19 входом выходного каскада 20, выход которого подключен к выходу устройства 17, стоки второго 2 входного полевого транзистора первого 3 дифференциального каскада, второго 7 входного полевого транзистора второго 8 дифференциального каскада и второго 12 входного полевого транзистора третьего 13 дифференциального каскада соединены со вторым 21 входом выходного каскада 20, исток первого 1 входного полевого транзистора первого 3 дифференциального каскада соединен с коллектором первого 22 вспомогательного транзистора, исток первого 6 входного полевого транзистора второго 8 дифференциального каскада соединен с коллектором второго 23 вспомогательного транзистора, исток первого 11 входного полевого транзистора третьего 13 дифференциального каскада соединен с коллектором третьего 24 вспомогательного транзистора, база которого подключена к источнику напряжения смещения 25, эмиттеры первого 22, второго 23 и третьего 24 вспомогательных транзисторов связаны с первой 26 шиной источника питания через соответствующие первый 27, второй 28 и третий 29 токостабилизирующие двухполюсники, предусмотрены новые элементы и связи - исток второго 2 входного полевого транзистора первого 3 дифференциального каскада связан с истоком первого 1 входного полевого транзистора первого 3 дифференциального каскада через первый 30 резистор местной отрицательной обратной связи и подключен к коллектору первого 31 дополнительного транзистора, исток второго 7 входного полевого транзистора второго 8 дифференциального каскада связан с истоком первого 6 входного полевого транзистора второго 8 дифференциального каскада через второй 32 резистор местной отрицательной обратной связи и подключен к коллектору второго 33 дополнительного транзистора, исток второго 12 входного полевого транзистора третьего 13 дифференциального каскада подключен к истоку первого 11 входного полевого транзистора третьего 13 дифференциального каскада через третий 34 резистор местной отрицательной обратной связи и связан коллектором третьего 35 дополнительного транзистора, причем база третьего 35 дополнительного транзистора соединена с источником напряжения смещения 25, эмиттер третьего 35 дополнительного транзистора подключен к первой 26 шине источника питания через третий 36 дополнительный токостабилизирующий двухполюсник и связан с базами первого 31 и второго 33 дополнительных транзисторов, эмиттеры которых соединены с первой 26 шиной источника питания через второй 37 и первый 38 токостабилизирующие двухполюсники, а базы первого 22 и второго 23 вспомогательных транзисторов подключены к эмиттеру третьего 24 вспомогательного транзистора.

На фиг. 1 показана схема ИУ-прототипа, созданная в Институте проблем управления РАН, а на чертеже фиг. 2 представлена схема заявляемого ИУ с повышенным ослаблением входного синфазного сигнала в соответствии с п. 1 формулы изобретения.

На фиг. 3 приведена схема двух входных каскадов ИУ фиг. 2, которая используется для аналитического расчета эффективности предлагаемого схемотехнического решения.

На фиг. 4 представлена схема фиг. 3, реализованная на элементах аналогового базового матричного кристалла АБМК_1_3, выпускаемого ОАО «Интеграл» (г. Минск).

На фиг. 5 приведена схема фиг. 4 в среде PSpice на моделях АБМК_1_3, в которой моделировалась передача на выход out (коэффициент Kс.сф.) входного синфазного сигнала V4.

На фиг. 6 приведена схема двух входных каскадов ИУ прототипа фиг. 1 в среде PSpice на моделях АБМК_1_3 для определения ее коэффициента передачи дифференциального сигнала (Kd).

На фиг. 7 показана частотная зависимость коэффициентов ослабления входного синфазного сигнала входных каскадов заявляемого ИУ и ИУ-прототипа. Из данных графиков следует, что в заявляемом ИУ коэффициент ослабления входного синфазного сигнала улучшается на 40 дБ (т.е. в 100 раз).

Инструментальный усилитель с повышенным ослаблением входного синфазного сигнала фиг. 2 содержит первый 1 и второй 2 входные полевые транзисторы первого 3 дифференциального каскада, затворы которых соединены с соответствующими первым 4 и вторым 5 входами первого 3 дифференциального каскада, первый 6 и второй 7 входные полевые транзисторы второго 8 дифференциального каскада, затворы которых соединены с соответствующими первым 9 и вторым 10 входами второго 8 дифференциального каскада, первый 11 и второй 12 входные полевые транзисторы третьего 13 дифференциального каскада, затворы которых соединены с соответствующими первым 14 и вторым 15 входами третьего 13 дифференциального каскада, причем первый 14 вход третьего 13 дифференциального каскада связан с источником заданного напряжения 16, а второй 15 вход третьего 13 дифференциального каскада связан с выходом устройства 17 через цепь отрицательной обратной связи 18, стоки первого 1 входного полевого транзистора первого 3 дифференциального каскада, первого 6 входного полевого транзистора второго 8 дифференциального каскада и первого 11 входного полевого транзистора третьего 13 дифференциального каскада соединены с первым 19 входом выходного каскада 20, выход которого подключен к выходу устройства 17, стоки второго 2 входного полевого транзистора первого 3 дифференциального каскада, второго 7 входного полевого транзистора второго 8 дифференциального каскада и второго 12 входного полевого транзистора третьего 13 дифференциального каскада соединены со вторым 21 входом выходного каскада 20, исток первого 1 входного полевого транзистора первого 3 дифференциального каскада соединен с коллектором первого 22 вспомогательного транзистора, исток первого 6 входного полевого транзистора второго 8 дифференциального каскада соединен с коллектором второго 23 вспомогательного транзистора, исток первого 11 входного полевого транзистора третьего 13 дифференциального каскада соединен с коллектором третьего 24 вспомогательного транзистора, база которого подключена к источнику напряжения смещения 25, эмиттеры первого 22, второго 23 и третьего 24 вспомогательных транзисторов связаны с первой 26 шиной источника питания через соответствующие первый 27, второй 28 и третий 29 токостабилизирующие двухполюсники. В схему введены исток второго 2 входного полевого транзистора первого 3 дифференциального каскада, который связан с истоком первого 1 входного полевого транзистора первого 3 дифференциального каскада через первый 30 резистор местной отрицательной обратной связи и подключен к коллектору первого 31 дополнительного транзистора, исток второго 7 входного полевого транзистора второго 8 дифференциального каскада, который связан с истоком первого 6 входного полевого транзистора второго 8 дифференциального каскада через второй 32 резистор местной отрицательной обратной связи и подключен к коллектору второго 33 дополнительного транзистора, исток второго 12 входного полевого транзистора третьего 13 дифференциального каскада, который подключен к истоку первого 11 входного полевого транзистора третьего 13 дифференциального каскада через третий 34 резистор местной отрицательной обратной связи и связан с коллектором третьего 35 дополнительного транзистора, причем база третьего 35 дополнительного транзистора соединена с источником напряжения смещения 25, эмиттер третьего 35 дополнительного транзистора подключен к первой 26 шине источника питания через третий 36 дополнительный токостабилизирующий двухполюсник и связан с базами первого 31 и второго 33 дополнительных транзисторов, эмиттеры которых соединены с первой 26 шиной источника питания через второй 37 и первый 38 токостабилизирующие двухполюсники, а базы первого 22 и второго 23 вспомогательных транзисторов подключены к эмиттеру третьего 24 вспомогательного транзистора.

В схеме фиг. 2 цепь отрицательной обратной связи 18 реализована на резисторах 40 и 41, а выходной каскад 20 подключен ко второй 39 шине источника питания.

В схеме фиг. 3 свойства нагрузки моделируются резисторами нагрузки 42 и 43. При этом выходные сигналы снимаются с выхода Вых. 2 (44) и выхода Вых. 1 (45) и в дальнейшем преобразуются выходным каскадом 20 в напряжение на выходе устройства 17.

В качестве источника напряжения смещения 25 (фиг. 2, фиг. 3, фиг. 4) могут применяться традиционные цепи смещения потенциалов (стабилитроны, резистивные делители и т.п.). При этом обозначения и работа элементов в схеме фиг. 4 полностью соответствует обозначениям и работе элементов в схеме фиг. 3.

Рассмотрим работу схемы фиг. 3 для случая, когда выходные сигналы снимаются с Вых. 1 и Вых. 2, а на первый 4 и второй 5 входы первого 3 дифференциального каскада подаются одинаковые синфазные напряжения (uc=uc1=uc2).

В результате воздействия входного синфазного сигнала uc=uc1=uc2 на первый 4 и второй 5 входы первого 3 дифференциального каскада изменяются коллекторные токи первого 22 вспомогательного и первого 31 дополнительного транзисторов, а также токи стоков первого 1 и второго 2 входных полевых транзисторов первого 3 дифференциального каскада.

где rк22, rк31 - сопротивления закрытых коллекторных переходов первого 22 вспомогательного и первого 31 дополнительного транзисторов.

Токи irк22 и irк31 передаются в эмиттерные цепи третьего 24 вспомогательного и третьего 35 дополнительного транзисторов и вызывают соответствующие изменения токов истока iu и токов стока ic первого 11 и второго 12 входных полевых транзисторов третьего 13 дифференциального каскада:

где α24≈1, α24≈1 - коэффициент передачи по току эмиттера третьего 24 вспомогательного и третьего 35 дополнительного транзисторов.

В результате приращения токов в резисторах нагрузки 42 и 43 определяются формулами

Как следствие, коэффициенты передачи входного синфазного сигнала для выхода 1 и выхода 2 можно найти из уравнений:

В схеме ИУ-прототипа

Таким образом, при введении новых элементов и связей между ними коэффициенты передачи синфазного сигнала с первого 4 и второго 5 входов первого 3 дифференциального каскада на выходы 44, 45 уменьшаются в β=80÷100 раз, где .

Коэффициент передачи дифференциального напряжения входного каскада на первом 1 и втором 2 входных полевых транзисторов первого 3 дифференциального каскада определяется формулой

где R30 - сопротивление первого 30 резистора местной отрицательной обратной связи;

R42, R43 - сопротивление резисторов нагрузки 42, 43.

Если выбрать Kd1≈1, то коэффициент ослабления входного синфазного сигнала (Kос.сф.) в предлагаемой схеме определяется уравнением

Сравнительное компьютерное моделирование схем фиг. 5, фиг. 6, фиг. 7 показывает, что заявляемый ИУ имеет более чем в 100 раз лучшее значение коэффициента ослабления входного синфазного сигнала. Это существенно снижает погрешности ИУ при работе с сигналами, имеющими синфазную составляющую.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Авербух, В. Инструментальные усилители. / В. Авербух // Схемотехника, №1 (3), 2001. - С. 26-29; Схемотехника, №2 (4), 2001. - С. 22-24.

2. Холенарсипур П. Три - это много для инструментального усилителя. / П. Холенарсипур // Компоненты и технологии, №6, 2008 г. - С. 26-30.

3. Прокопенко Н.Н. Основные свойства, параметры и базовые схемы включения мультидифференциальных операционных усилителей с высокоимпедансным узлом. / Н.Н. Прокопенко, О.В. Дворников, П.С. Будяков // Электронная техника. Серия 2. Полупроводниковые приборы. Выпуск 2 (233), 2014 г. - С. 53-64.

4. Прокопенко Н.Н. Основные параметры и уравнения базовых схем включения мультидифференциальных операционных усилителей с высокоимпедансным узлом. / Н.Н. Прокопенко, Н.В. Бутырлагин, И.В. Пахомов // Проблемы разработки перспективных микро- и наноэлектронных систем - 2014. Сборник трудов. Часть 3. / Под общ. ред. академика РАН А.Л. Стемпковского. - М.: ИППМ РАН, 2014. - С. 111-116.

5. Патент US 6.617.922, fig.3.

6. Патент US 6.469.576, fig.2.

7. Патент US 7.170.349, fig.2.

8. Патент US 6.628.168, fig.1, fig.2.

9. Патент US 5.990.737, fig.7.

10. Патент US 7.199.612, fig.4.

11. Патент US 6.977.526, fig.1.

12. 3аявка на патент US 2009/0206929, fig.5.

13. Заявка на патент US 2008/0150636, fig.3D.

14. Заявка на патент US 2003/0132803, fig.7.

15.3аявка на патент US 2006/0244530, fig.2.

16. Патент US 6.388.519, fig.1.

17. Патент US 6.011.436, fig.4.

18. Патент US 6.559.720, fig.4.

19. 3аявка на патент US 2008/0186091, fig.4.

20. 3аявка на патент US 2013/0099782, fig.2.

21. Патент US 5.510.745.

22. Патент US 7.145.359, fig.4.

23. Заявка на патент WO 03/043281, fig.6.

24. Патент US 5.729.161, fig.2.

25. Патент US 4.847.519, fig.2.

26. Патент US 3.916.215.

1. Инструментальный усилитель с повышенным ослаблением входного синфазного сигнала, содержащий первый (1) и второй (2) входные полевые транзисторы первого (3) дифференциального каскада, затворы которых соединены с соответствующими первым (4) и вторым (5) входами первого (3) дифференциального каскада, первый (6) и второй (7) входные полевые транзисторы второго (8) дифференциального каскада, затворы которых соединены с соответствующими первым (9) и вторым (10) входами второго (8) дифференциального каскада, первый (11) и второй (12) входные полевые транзисторы третьего (13) дифференциального каскада, затворы которых соединены с соответствующими первым (14) и вторым (15) входами третьего (13) дифференциального каскада, причем первый (14) вход третьего (13) дифференциального каскада связан с источником заданного напряжения (16), а второй (15) вход третьего (13) дифференциального каскада связан с выходом устройства (17) через цепь обратной связи (18), стоки первого (1) входного полевого транзистора первого (3) дифференциального каскада, первого (6) входного полевого транзистора второго (8) дифференциального каскада и первого (11) входного полевого транзистора третьего (13) дифференциального каскада соединены с первым (19) входом выходного каскада (20), выход которого подключен к выходу устройства (17), стоки второго (2) входного полевого транзистора первого (3) дифференциального каскада, второго (7) входного полевого транзистора второго (8) дифференциального каскада и второго (12) входного полевого транзистора третьего (13) дифференциального каскада соединены со вторым (21) входом выходного каскада (20), исток первого (1) входного полевого транзистора первого (3) дифференциального каскада соединен с коллектором первого (22) вспомогательного транзистора, исток первого (6) входного полевого транзистора второго (8) дифференциального каскада соединен с коллектором второго (23) вспомогательного транзистора, исток первого (11) входного полевого транзистора третьего (13) дифференциального каскада соединен с коллектором третьего (24) вспомогательного транзистора, база которого подключена к источнику напряжения смещения (25), эмиттеры первого (22), второго (23) и третьего (24) вспомогательных транзисторов связаны с первой (26) шиной источника питания через соответствующие первый (27), второй (28) и третий (29) токостабилизирующие двухполюсники, отличающийся тем, что исток второго (2) входного полевого транзистора первого (3) дифференциального каскада связан с истоком первого (1) входного полевого транзистора первого (3) дифференциального каскада через первый (30) резистор местной отрицательной обратной связи и подключен к коллектору первого (31) дополнительного транзистора, исток второго (7) входного полевого транзистора второго (8) дифференциального каскада связан с истоком первого (6) входного полевого транзистора второго (8) дифференциального каскада через второй (32) резистор местной отрицательной обратной связи и подключен к коллектору второго (33) дополнительного транзистора, исток второго (12) входного полевого транзистора третьего (13) дифференциального каскада подключен к истоку первого (11) входного полевого транзистора третьего (13) дифференциального каскада через третий (34) резистор местной отрицательной обратной связи и связан коллектором третьего (35) дополнительного транзистора, причем база третьего (35) дополнительного транзистора соединена с источником напряжения смещения (25), эмиттер третьего (35) дополнительного транзистора подключен к первой (26) шине источника питания через третий (36) дополнительный токостабилизирующий двухполюсник и связан с базами первого (31) и второго (33) дополнительных транзисторов, эмиттеры которых соединены с первой (26) шиной источника питания через второй (37) и первый (38) токостабилизирующие двухполюсники, а базы первого (22) и второго (23) вспомогательных транзисторов подключены к эмиттеру третьего (24) вспомогательного транзистора.

2. Инструментальный усилитель с повышенным ослаблением входного синфазного сигнала по п. 1, отличающийся тем, что в качестве источника заданного напряжения (16) используется потенциал общей шины источника питания.