Устройство для вычисления функции y=x1/n

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и автоматике и может найти применение в быстродействующих вычислительных комплексах. Техническим результатом является повышение достоверности функционального преобразования. Устройство содержит регистр, блок памяти, блок вычисления интерполяционных поправок, сумматор, первый и второй сдвигатели и распределитель. Для обеспечения достоверности результата при любых значениях аргумента между распределителем и вторым сдвигателем дополнительно введена схема пересчета импульсов (в n раз). 1 табл., 1 ил.

Реферат

Изобретение относится к вычислительной технике и автоматике, может найти широкое применение в быстродействующих высокоточных автоматизированных вычислительных комплексах, например, при решении задач навигации (n - натуральное число).

Известен цифроаналоговый функциональный преобразователь [А.с. 413502 СССР, 1974], содержащий входной регистр, блок памяти, блок вычисления интерполяционных поправок и сумматор. Однако такой преобразователь имеет низкую точность функционального преобразования.

Наиболее близким к изобретению является устройство для вычисления функции [А.с. 746544 СССР, 1980], содержащее регистр, блок памяти, блок вычисления интерполяционных поправок и сумматор, два сдвигателя и распределитель. Первый вход первого сдвигателя подключен к выходу регистра и входу распределителя, а второй - к первому выходу распределителя, второй выход которого соединен с первым входом второго сдвигателя, первый выход первого сдвигателя соединен с первым входом блока памяти, а второй - с первым входом блока вычисления интерполяционных поправок и вторым входом блока памяти, выход которого подключен к второму входу блока интерполяционных поправок, выход которого подключен к первому входу сумматора, второй вход которого подключен к второму выходу блока памяти, а выход сумматора - к второму входу второго сдвигателя, выход которого является выходом устройства.

Основным недостатком этого устройства является недостоверность выходных значений функции при некоторых значениях аргумента.

Задачей настоящего изобретения является повышение достоверности функционального преобразования.

Технический результат предлагаемого изобретения - обеспечение достоверности результата при любых значениях аргумента.

Технический результат достигается тем, что устройство для вычисления функции включает регистр, блок памяти, блок вычисления интерполяционных поправок, сумматор, первый и второй сдвигатели и распределитель, при этом первый вход первого сдвигателя подключен к выходу регистра и входу распределителя, а второй - к первому выходу распределителя, первый выход первого сдвигателя соединен с первым входом блока памяти, а второй - с первым входом блока вычисления интерполяционных поправок и вторым входом блока памяти, первый выход которого подключен к второму входу блока интерполяционных поправок, выход которого подключен к первому входу сумматора, второй вход которого подключен к второму выходу блока памяти, а выход сумматора - к второму входу второго сдвигателя, выход которого является выходом устройства, которое дополнительно содержит схему пересчета (в n раз), соединенную по входу со вторым выходом распределителя и по выходу - с первым входом второго сдвигателя.

Введение схемы пересчета (в n раз) и ее связей (по входу) со вторым выходом распределителя и (по выходу) - с первым входом второго сдвигателя позволило обеспечить достоверность функционального преобразования при любых значениях аргумента.

Предложенное устройство имеет изобретательский уровень, так как из опубликованных научных данных и существующих технических решений явным образом не следует, что заявляемая совокупность схемы пересчета (уменьшение числа импульсов в n раз) и ее связей с другими блоками прототипа позволяют обеспечить достоверность работы при любых значениях исходных данных.

Предложенное устройство для вычисления функции промышленно применимо, поскольку его техническая реализация возможна с использованием типовых элементов микроэлектронной техники (интегральных логических схем).

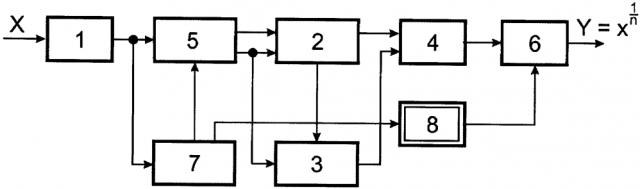

На фиг. представлена блок-схема устройства, а в таблице - расчет результатов преобразований для прототипа и заявленного устройства.

Устройство содержит регистр 1, блок 2 памяти, блок 3 вычисления интерполяционных поправок, сумматор 4, первый 5 и второй 6 сдвигатели, распределитель 7, схему 8 пересчета.

Причем первый вход первого сдвигателя 5 подключен к выходу регистра 1 и к входу распределителя 7, а второй вход - к первому выходу распределителя 7, второй выход которого соединен через схему 8 пересчета с первым входом второго сдвигателя 6, первый выход первого сдвигателя соединен с первым входом блока 2 памяти, а второй - с первым входом блока 3 вычисления интерполяционных поправок и вторым входом блока 2 памяти, выход которого подключен к второму входу блока 3 интерполяционных поправок, выход которого подключен к первому входу сумматора 4, второй вход которого подключен к второму выходу блока 2 памяти, а выход сумматора 4 - к второму входу второго сдвигателя 6, выход которого является выходом устройства.

Устройство работает следующим образом. Входной код аргумента запоминается в регистре 1. С выхода регистра 1 он поступает на распределитель 7, где осуществляется его анализ. Если величина кода больше значения , то код непосредственно без сдвига проходит на входы блока 2 памяти и блока 3 вычисления интерполяционных поправок. Полученные табличные значения функции и интерполяционная поправка суммируются в сумматоре 4 и также без сдвига проходят на выход устройства.

В случае если значение кода аргумента будет равно или меньше , то из распределителя поступает команда: в первый сдвигатель 5 произвести сдвиг кода x влево на m разрядов вправо, а во втором сдвигателе 6 на разрядов вправо, где - целая часть частного от деления. Остальные узлы (блок памяти, блок вычисления интерполяционных поправок и сумматор) функционируют, как и в предыдущем случае.

Первый сдвигатель 5 осуществляет операцию умножения кода аргумента x на величину , где m - величина сдвига, что переводит код аргумента в область малых ошибок функционального преобразования. С помощью блока 2 памяти, блока 3 вычисления интерполяционных поправок и сумматора 4 осуществляется преобразование кода в код функции .

Второй сдвигатель 6 с помощью схемы 8 пересчета в n раз выполняет операцию деления кода функции на величину , что и позволяет получить значение . Управление работой с двигателей осуществляется распределителем 7.

Благодаря дополнительно введенной схеме 8 пересчета (в n раз) и ее связям с другими блоками исключена недостоверность результата у прототипа при некоторых значениях аргумента x (см.таблицу).

В графе 6 для прототипа наблюдаем недостоверное значение функции в отличие от правильного значения у заявляемого устройства.

Устройство для вычисления функции , включающее регистр, блок памяти, блок вычисления интерполяционных поправок, сумматор, первый и второй сдвигатели и распределитель, при этом первый вход первого сдвигателя подключен к выходу регистра и входу распределителя, а второй - к первому выходу распределителя, первый выход первого сдвигателя соединен с первым входом блока памяти, а второй - с первым входом блока вычисления интерполяционных поправок и вторым входом блока памяти, первый выход которого подключен к второму входу блока интерполяционных поправок, выход которого подключен к первому входу сумматора, второй вход которого подключен к второму выходу блока памяти, а выход сумматора - к второму входу второго сдвигателя, выход которого является выходом устройства, отличающееся тем, что дополнительно содержит схему пересчета (в n раз), соединенную по входу со вторым выходом распределителя и по выходу - с первым входом второго сдвигателя.