Устройство захвата изображения, система захвата изображения, способ управления для устройства захвата изображения и способ проверки для устройства захвата изображения

Иллюстрации

Показать всеИзобретение относится к устройству захвата изображения и способу его проверки. Техническим результатом является уменьшение схемы для множества размещенных по столбцам аналого-цифровых (АЦ) схем и обнаружение неисправности блока удержания. Предложено устройство захвата изображения, содержащее: множество пикселей, размещенных по строкам и столбцам, причем каждый из пикселей выводит сигнал фотоэлектрического преобразования на основе падающего света; множество блоков АЦ-преобразования, и блок выбора, выполненный с возможностью выполнения выбора запоминающего бит элемента, который удерживает сигнал первого бита цифрового сигнала, среди множества запоминающих бит элементов совместно в запоминающем блоке в каждом из множества блоков АЦ-преобразования. 4 н. и 13 з.п. ф-лы, 28 ил.

Реферат

Уровень техники

Область техники, к которой относится изобретение

[0001] Настоящее изобретение относится к устройству захвата изображения, системе захвата изображения, способу управления для устройства захвата изображения и способу проверки для устройства захвата изображения.

Описание предшествующего уровня техники

[0002] Имеется устройство захвата изображения, включающее в себя множество пикселей, размещенных в матрицу, и множество аналого-цифровых (АЦ) блоков преобразования, соответственно соответствующих столбцам, по которым размещено множество пикселей.

[0003] Такое устройство захвата изображения, описанное в выложенном патентном документе Японии № 2012-60334, включает в себя множество размещенных по столбцам АЦ-схем, каждая из которых включает в себя блок удержания данных и блок коммутации данных. При обнаружении неисправности блоком удержания данных блок коммутации данных каждой из размещенных по столбцам АЦ-схем выполняет битовый сдвиг данных, подлежащих выводу в блок удержания данных так, чтобы почти не возникала нехватка данных, вызываемая неисправностью в блоке удержания данных.

[0004] В устройстве захвата изображения, описанном в выложенном патентном документе Японии № 2012-60334 вследствие предоставления блока коммутации данных каждой из множества размещенных по столбцам АЦ-схем для устранения снижения качества изображения возникает проблема, заключающаяся в увеличении области схемы для множества размещенных по столбцам АЦ-схем.

Раскрытие изобретения

[0005] Согласно одному варианту выполнения настоящего изобретения предложено устройство захвата изображения, включающее в себя: множество пикселей, размещенных по строкам и столбцам, причем каждый из пикселей выполнен с возможностью вывода сигнала фотоэлектрического преобразования на основе падающего света; множество блоков АЦ-преобразования, причем каждый из блоков АЦ-преобразования предоставлен для соответствия столбцу из множества пикселей и выполнен с возможностью преобразования сигнала фотоэлектрического преобразования в многобитовый цифровой сигнал; и блок выбора, причем каждый из множества блоков АЦ-преобразования включает в себя запоминающий блок, который выполнен с возможностью удержания цифрового сигнала, при этом запоминающий блок включает в себя первый запоминающий бит элемент и второй запоминающий бит элемент, и блок выбора выполнен с возможностью выполнения выбора запоминающего бит элемента, который выполнен с возможностью удержания сигнала первого бита цифрового сигнала, среди первого запоминающего бит элемента и второго запоминающего бит элемента, совместно в запоминающем блоке в каждом из множества блоков АЦ-преобразования.

[0006] Дополнительные признаки настоящего изобретения станут очевидными из последующего описания примерных вариантов осуществления со ссылкой на прилагаемые чертежи.

Краткое описание чертежей

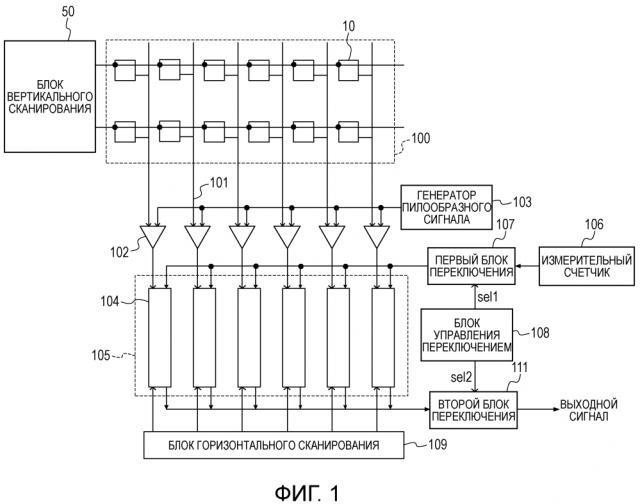

[0007] На Фиг.1 показана примерная конфигурация устройства захвата изображения.

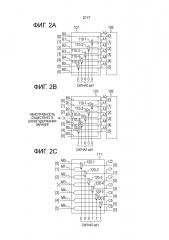

[0008] На Фиг.2A показаны конфигурации и действия первого блока переключения и измерительного счетчика.

[0009] На Фиг.2B показаны конфигурации и действия первого блока переключения и измерительного счетчика.

[0010] На Фиг.2C показаны конфигурация и действие второго блока переключения.

[0011] На Фиг.3A показаны конфигурации и действия первого блока переключения и измерительного счетчика.

[0012] На Фиг.3B показаны конфигурации и действия первого блока переключения и измерительного счетчика.

[0013] На Фиг.3C показаны конфигурация и действие второго блока переключения.

[0014] На Фиг.4A показаны конфигурации и действия первого блока переключения и измерительного счетчика.

[0015] На Фиг.4B показаны конфигурации и действия первого блока переключения и измерительного счетчика.

[0016] На Фиг.5 показаны конфигурация и действие второго блока переключения.

[0017] На Фиг.6A показаны конфигурации и действия первого блока переключения и измерительного счетчика.

[0018] На Фиг.6B показаны конфигурации и действия первого блока переключения и измерительного счетчика.

[0019] На Фиг.7 показаны конфигурация и действие второго блока переключения.

[0020] На Фиг.8A показаны конфигурации и действия первого блока переключения и измерительного счетчика.

[0021] На Фиг.8B показаны конфигурации и действия первого блока переключения и измерительного счетчика.

[0022] На Фиг.9 показаны конфигурация и действие второго блока переключения.

[0023] На Фиг.10 показана примерная конфигурация устройства захвата изображения.

[0024] На Фиг.11A показана примерная конфигурация и примерное действие измерительного счетчика.

[0025] На Фиг.11B показана примерная конфигурация и примерное действие измерительного счетчика.

[0026] На Фиг.12A показана примерная конфигурация и примерное действие измерительного счетчика.

[0027] На Фиг.12B показана примерная конфигурация и примерное действие измерительного счетчика.

[0028] На Фиг.13 показана примерная конфигурация устройства захвата изображения.

[0029] На Фиг.14 показано примерное действие устройства захвата изображения.

[0030] На Фиг.15 показана примерная конфигурация устройства захвата изображения.

[0031] На Фиг.16A показана блок-схема примера последовательности проверки.

[0032] На Фиг.16B показана блок-схема примера последовательности проверки.

[0033] На Фиг.17A показана примерная конфигурация системы захвата изображения.

[0034] На Фиг.17B показана блок-схема примера последовательности проверки.

Описание вариантов осуществления изобретения

[0035] Далее со ссылкой на чертежи будут описаны соответствующие примерные варианты осуществления.

Первый примерный вариант осуществления

[0036] На Фиг.1 показана конфигурация устройства захвата изображения согласно настоящему примерному варианту осуществления. Множество пикселей 10 размещено по строкам и столбцам в участке 100 с пикселями. Блок 50 вертикального сканирования сканирует пиксели 10 в участке 100 с пикселями по каждой строке.

[0037] Каждый из множества пикселей 10 выводит сигнал фотоэлектрического преобразования на основе падающего света в вертикальную сигнальную линию 101 в каждом столбце в соответствии со сканированием блока 50 вертикального сканирования. Блок 102 сравнения выводит сигнал результата сравнения, указывающий результат сравнения между сигналом фотоэлектрического преобразования и пилообразным сигналом, выводимым из генератора 103 пилообразного сигнала, в запоминающий блок 104. Пилообразный сигнал является сигналом, имеющим потенциал, который изменяется в зависимости от времени. Запоминающий блок 104 в каждом столбце включает в себя шесть запоминающих биты элементов, которые удерживают 6-битовый цифровой сигнал, и одиночный запоминающий избыточный бит элемент. Запоминающий избыточный бит элемент является запоминающим бит элементом, составляющим часть множества запоминающих биты элементов, предоставленных запоминающему блоку 104. Запоминающий избыточный бит элемент является также запоминающим бит элементом, который удерживает сигнал предварительно определенного бита счетного сигнала. Блок АЦ-преобразования устройства захвата изображения согласно настоящему примерному варианту осуществления составляют блок 102 сравнения и запоминающий блок 104. То есть каждый из множества блоков АЦ-преобразования предоставлен таким образом, чтобы соответствовать столбцу, в котором размещены пиксели 10. Блок 105 удержания включает в себя множество запоминающих блоков 104.

[0038] Тактовые сигналы вводятся в измерительный счетчик 106 от тактового генератора, который не изображен на чертеже. Измерительный счетчик 106 генерирует 6-битовый счетный сигнал, получаемый посредством подсчета количества тактов. Счетный сигнал совместно подается во множество запоминающих блоков 104 из измерительного счетчика 106 через первый блок 107 переключения. Первый блок 107 переключения является блоком выбора, выполненным с возможностью выбора запоминающего бит элемента, который удерживает сигнал первого бита счетного сигнала, соответствующего цифровому сигналу, среди множества запоминающих биты элементов совместно в запоминающем блоке 104 в каждом из множества блоков АЦ-преобразования. Кроме того, блок выбора согласно настоящему примерному варианту осуществления включает в себя блок 108 управления переключением.

[0039] Управление первым блоком 107 переключения осуществляется посредством сигнала sel1, выводимого из блока 108 управления переключением.

[0040] Измерительный счетчик начинает измерять количество тактов синхронно с состоянием, при котором генератор 103 пилообразного сигнала начинает изменять потенциал пилообразного сигнала, который зависит от времени. Измерительный счетчик 106 также выводит счетный сигнал, полученный посредством измерения, в первый блок 107 переключения. При изменении соотношения амплитуд между потенциалом пилообразного сигнала и потенциалом сигнала фотоэлектрического преобразования блок 102 сравнения изменяет значение сигнала упомянутого сигнала результата сравнения. Запоминающий блок 104 в каждом столбце удерживает счетный сигнал, выводимый из первого блока 107 переключения, в момент времени, в который изменяется значение сигнала упомянутого сигнала результата сравнения. После этого, генератор 103 пилообразного сигнала заканчивает изменение потенциала пилообразного сигнала, который зависит от времени. Измерительный счетчик 106 также заканчивает измерение количества тактов. Соответственно, запоминающий блок 104 в каждом столбце удерживает счетный сигнал на основе потенциала сигнала фотоэлектрического преобразования. Счетный сигнал, удерживаемый в запоминающем блоке 104 в каждом столбце, является цифровым сигналом, полученным посредством АЦ-преобразования сигнала фотоэлектрического преобразования.

[0041] Блок 109 горизонтального сканирования последовательно сканирует запоминающий блок 104 в каждом столбце. С помощью сканирования посредством блока 109 горизонтального сканирования цифровой сигнал последовательно выводится из запоминающего блока 104 в каждом столбце во второй блок 111 переключения.

[0042] Управление вторым блоком 111 переключения осуществляется посредством сигнала sel2, выводимого из блока 108 управления переключением. Второй блок 111 переключения является блоком вывода, выполненным с возможностью вывода сигнала, полученного посредством обработки цифрового сигнала, выводимого из запоминающего блока 104 в каждом столбце, во внешнюю часть устройства захвата изображения. Второй блок 111 переключения выполняет действие по перестройке порядка множества битов счетного сигнала, выводимого из запоминающего блока 104.

[0043] На Фиг.2A, Фиг.2B и Фиг.2C совместно показаны конфигурации и действия измерительного счетчика 106 и первого блока 107 переключения.

[0044] На Фиг.2A показано действие в случае, в котором не существует какой-либо неисправности в запоминающих блоках 104 во множестве столбцов в блоке 105 удержания. На Фиг.2B показано действие в случае, в котором существует неисправность в запоминающем бит элементе, который удерживает сигнал бита [3] по меньшей мере одного запоминающего блока 104 среди запоминающих блоков 104 во множестве столбцов в блоке 105 удержания. Конфигурации и действия измерительного счетчика 106 и первый блок 107 переключения будут описаны со ссылкой на Фиг.2A.

[0045] Измерительный счетчик 106 последовательно выводит 6-битовые сигналы, соответствующие битам с [0] по [5] счетного сигнала в соответствующие линии с A0 по A5 данных. Биты с [0] по [5] счетного сигнала размещены с бита более низкого порядка по бит более высокого порядка в указанном порядке. Первый блок 107 переключения включает в себя схемы с 110-1 по 110-5 выбора. Сигнал sel1 вводится к соответствующие схемы с 110-1 по 110-5 выбора из блока 108 управления переключением. Схемы с 110-1 по 110-5 выбора последовательно соответственно выводят счетный сигнал в линии с B0 по B5 данных на основе значения сигнала упомянутого сигнала sel1. Линии с B0 по B5 данных соответственно соединены с шестью запоминающими биты элементами, предоставленными запоминающему блоку 104 в каждом столбце. Линия BD данных соединена с запоминающим избыточный бит элементом, предоставленным каждому из запоминающих блоков 104 во множестве столбцов. Линии с B0 по B5 данных и линия BD данных совместно соединены со множеством запоминающих блоков 104.

[0046] На Фиг.2A значение сигнала упомянутого сигнала sel1 составляет (00000) в указанном порядке со схемы 110-5 выбора по схему 110-1 выбора. На Фиг.2A по отношению к каждой из схем с 110-1 по 110-5 выбора линия данных, выбранная в соответствии со значением сигнала упомянутого сигнала sel1, представлена кодами 0 и 1. Например, когда введен сигнал sel1, имеющий значение 0, то схема 110-1 выбора выводит сигнал линии A1 данных в линию B1 данных. С другой стороны, когда введен сигнал sel1, имеющий значение 1, то схема 110-1 выбора выводит сигнал линии A0 данных в линию B1 данных. Поэтому, в случае, в котором значение сигнала упомянутого сигнала sel1 составляет (00000) в указанном порядке со схемы 110-5 выбора по схему 110-1 выбора, то сигналы битов с [0] по [5] счетного сигнала последовательно соответственно выводятся в линии с B0 по B5 данных из первого блока 107 переключения. Кроме того, сигнал бита [5] счетного сигнала выводится в линию BD данных из первого блока 107 переключения.

[0047] На Фиг.2A показано первое действие. В первом действии сигнал бита [4], соответствующий первому биту, удерживается в запоминающем бит элементе, соединенном с линией B4 данных, соответствующем первому запоминающему бит элементу среди множества запоминающих биты элементов. Впоследствии, сигнал бита [5], соответствующий биту более высокого порядка по отношению к первому биту на один бит, удерживается в запоминающем бит элементе, соединенном с линией B5 данных, который соответствует второму запоминающему бит элементу среди множества запоминающих биты элементов.

[0048] Далее, со ссылкой на Фиг.2B будут описаны конфигурации и действия измерительного счетчика 106 и первого блока 107 переключения. Конфигурация на Фиг.2B является той же самой, что и на Фиг.2A.

[0049] На Фиг.2B показано действие в случае, в котором существует неисправность в одном запоминающем бит элементе по меньшей мере в одном из запоминающих блоков 104 в блоке 105 удержания. В данном документе, неисправность существует в запоминающем бит элементе, соединенном с линией B3 данных. Обнаружение неисправности предварительно выполняется посредством проверки сигнала, выводимого из запоминающего блока 104. Блок 108 управления переключением устанавливает значение сигнала упомянутого сигнала sel1 в качестве (11000) в данном порядке со схемы 110-5 выбора по схему 110-1 выбора. Соответственно, сигнал бита [3] счетного сигнала, который является тем же самым, что и в линии B3 данных, выводится в линию B4 данных, а сигнал бита [4] счетного сигнала выводится в линию B5 данных в запоминающем блоке 104 в каждом столбце. Сигнал бита [5] счетного сигнала выводится в линию BD данных. Таким образом, в действии на Фиг.2B, каждый из получателей вывода сигналов битов, равных биту [3] и выше, сдвигаются к более высокому порядку на один бит по отношению к действию на Фиг.2A. Соответственно, сигналы битов с [0] по [4] счетного сигнала удерживаются в запоминающих биты элементах в запоминающем блоке 104 в каждом столбце, а сигнал бита [5] счетного сигнала удерживается в запоминающем избыточный бит элементе. Соответственно, даже в случае, в котором неисправность существует в запоминающем бит элементе, соединенном с линией B3 данных, сигналы битов с [0] по [5] счетного сигнала удерживаются в запоминающем блоке 104 в каждом столбце.

[0050] На Фиг.2B показано второе действие. Во втором действии сигнал бита [4], соответствующий первому биту, удерживается в запоминающем бит элементе, соединенном с линией B5 данных, который соответствует второму запоминающему бит элементу среди множества запоминающих биты элементов. Кроме того, согласно настоящему примерному варианту осуществления, в качестве части второго действия сигнал бита [5], который является битом более высокого порядка на один бит по отношению к сигналу бита [4], соответствующему первому биту, удерживается в запоминающем избыточный бит элементе, соединенном с линией BD данных.

[0051] Далее, со ссылкой на Фиг.2C будут описаны конфигурация и действие второго блока 111 переключения. Действие второго блока 111 переключения на Фиг.2C представляет собой случай, в котором первый блок 107 переключения выполняет действие, изображенное на Фиг.2B.

[0052] Второй блок 111 переключения включает в себя схемы с 120-1 по 120-6 выбора. На Фиг.2C относительно каждой из схем с 120-1 по 120-6 выбора, линия данных, выбранная в соответствии со значением сигнала упомянутого сигнала sel2, выводимого из блока 108 управления переключением, представлена кодами 0 и 1.

[0053] Запоминающий бит элемент, соединенный с линией B0 данных, соединен с линией M0 данных в запоминающем блоке 104 в каждом столбце. В дальнейшем, схожим образом запоминающие биты элементы, соединенные с линиями с B1 по B5 данных, соответственно соединены с линиями с M1 по M5 данных в указанном порядке. Запоминающий избыточный бит элемент, соединенный с линией BD данных, соединен с линией B6 данных.

[0054] В соответствии со сканированием блока 109 горизонтального сканирования сигналы битов с [0] по [5] счетного сигнала соответственно выводятся во второй блок 111 переключения через линии M0 и M2 данных и линии с M4 по M6 данных из запоминающего блока 104 в каждом столбце. Запоминающий бит элемент, соединенный с линией M3 данных, не удерживает счетный сигнал. Поэтому счетный сигнал не выводится в линию M3 данных из запоминающего блока 104.

[0055] Блок 108 управления переключением устанавливает значение сигнала упомянутого сигнала sel2 в качестве (000111) в указанном порядке со схемы 120-1 выбора по схему 120-6 выбора. Соответственно, сигналы, выводимые в соответствующие линии с C0 по C5 данных, являются сигналами битов с [0] по [5] счетного сигнала в указанном порядке. Сигнал выводимый в линию C6 данных, является сигналом бита [5] счетного сигнала. Следует отметить, что, несмотря на то, что не показано на чертеже, в случае, в котором первый блок 107 переключения выполняет действие с Фиг.2A, блок 108 управления переключением устанавливает значение сигнала упомянутого сигнала sel2 в качестве (000000) в начальном порядке со схемы 120-1 выбора по схему 120-6 выбора. Соответственно, биты счетного сигнала, выводимого вторым блоком 111 переключения в соответствующие линии с C0 по C6 данных, являются теми же самым, что и изображенные на Фиг.2C. Соответственно, битовые числа счетного сигнала, выводимого вторым блоком 111 переключения в соответствующие линии с C0 по C6 данных, когда первый блок 107 переключения задействован в конфигурации, изображенной на Фиг.2A, могут быть установлены идентичными битовым числам, когда первым блоком 107 переключения задействован в конфигурации, изображенной на Фиг.2B. Соответственно, можно избегать переключения действий в соответствии с присутствием или отсутствием неисправности в запоминающем блоке 104 в схеме вне устройства захвата изображения.

[0056] Кроме того, так как устройство захвата изображения согласно настоящему примерному варианту осуществления включает в себя первый блок 107 переключения, то схема вне устройства захвата изображения, в которую счетный сигнал выводится из второго блока 111 переключения, может удерживать счетный сигнал, не ощущая нехватку бита, даже когда в запоминающем блоке 104 существует неисправность.

[0057] Таким образом устройство захвата изображения согласно настоящему примерному варианту осуществления может изменять биты счетного сигнала, выводимого первым блоком 107 переключения в линии с B0 по B5 данных в соответствии с неисправностью в запоминающем бит элементе в запоминающем блоке 104. Первый блок 107 переключения изменяет биты счетного сигнала совместно по отношению ко множеству запоминающих блоков 104. Соответственно, можно уменьшить область схемы по сравнению со случаем, в котором запоминающий блок 104 в каждом из множества блоков АЦ-преобразования снабжен блоком переключения. Кроме того, даже когда в запоминающем блоке 104 существует неисправность, поскольку первый блок 107 переключения изменяет биты счетного сигнала, выводимого в линии с B0 по B5 данных, запоминающий блок 104 может удерживать счетный сигнал.

[0058] Таким образом, устройство захвата изображения согласно настоящему примерному варианту осуществления может обеспечить технологию для устранения снижения качества изображения, вызванного неисправностью в блоке АЦ-преобразования, при одновременном устранении увеличения масштаба схемы множества блоков АЦ-преобразования.

[0059] Следует отметить, что согласно настоящему примерному варианту осуществления описания были предоставлены для случая, в котором запоминающий бит элемент, соединенный с линией B3 данных, имеет неисправность, однако такая конфигурация может быть применена к случаю, в котором любой из запоминающих биты элементов, соединенных с линиями с B0 по B5 данных, имеет неисправность.

[0060] Кроме того, согласно настоящему примерному варианту осуществления линия BD данных выполнена так, чтобы сигнал бита [5] счетного сигнала передавался через нее, однако такая конфигурация не ограничена вышеупомянутым. Далее, будет описано другое устройство захвата изображения согласно настоящему примерному варианту осуществления.

[0061] На Фиг.3A показаны конфигурации первого блока 107 переключения и измерительного счетчика 106 другого устройства захвата изображения. Также на Фиг.3A компоненту, имеющему ту же самую функцию, что и на Фиг.2A, назначена та же самая ссылочная позиция, что и на Фиг.2A. На Фиг.2A запоминающий избыточный бит элемент в запоминающем блоке 104 в каждом столбце удерживает сигнал бита [5], соответствующий самому старшему биту. На Фиг.3A показан пример, в котором запоминающий избыточный бит элемент в запоминающем блоке 104 в каждом столбце удерживает сигнал бита [0], соответствующий самому младшему биту.

[0062] На Фиг.3A показано действие в случае, в котором никакой неисправности не существует в запоминающих биты элементах. Значение сигнала упомянутого сигнала sel1 составляет (00000) по порядку со схемы 110-5 выбора по схему 110-1 выбора.

[0063] На Фиг.3A показано первое действие. Первое действие, упоминаемое в данном документе, является действием, в котором сигнал бита [1], соответствующий первому биту, удерживается в запоминающем бит элементе, соединенном с линией B1 данных, соответствующем первому запоминающему бит элементу из множества запоминающих биты элементов. Впоследствии, сигнал бита [0], соответствующий биту более низкого порядка по отношению к первому биту на один бит, удерживается в запоминающем бит элементе, соединенном с линией B0 данных, соответствующем второму запоминающему бит элементу среди множества запоминающих биты элементов.

[0064] На Фиг.3B показано действие в случае, в котором запоминающий бит элемент, соединенный с линией данных B2, имеет неисправность в конфигурациях первого блока 107 переключения и измерительного счетчика 106, изображенных на Фиг.3A. Блок 108 управления переключением устанавливает значение сигнала упомянутого сигнала sel1 в качестве (00011) по порядку со схемы 110-5 выбора по схему 110-1 выбора. Следовательно, сигналы бита [1] и бита [2] счетного сигнала соответственно выводятся в линию B0 данных и линию B1 данных. Кроме того, сигналы битов с [3] по [5] счетного сигнала соответственно выводятся в линии с B3 по B5 данных. Сигнал бита [0] счетного сигнала выводится в линию BD данных. Таким образом, в отличие от действия на Фиг.3A в действии на Фиг.3B каждый из сигналов битов, низших или равных биту [2], сдвигаются к более низкому порядку на один бит.

[0065] На Фиг.3B показано второе действие. Второе действие, упоминаемое в данном документе, является действием, в котором сигнал бита [1], соответствующий первому биту, удерживается в запоминающем бит элементе, соединенном с линией B0 данных, соответствующем второму запоминающему бит элементу среди множества запоминающих биты элементов. Кроме того, согласно настоящему примерному варианту осуществления в качестве части второго действия, в дополнение, сигнал бита [0], соответствующий биту более низкого порядка по отношению к сигналу бита [1], соответствующему первому биту, на один бит, удерживается в запоминающем избыточный бит элементе, соединенном с линией BD данных.

[0066] На Фиг.3C показана конфигурация второго блока 111 переключения. Также на Фиг.3C компоненту, имеющему ту же самую функцию, что и на Фиг.2C, назначена та же самая ссылочная позиция, что и на Фиг.2C.

[0067] Блок 108 управления переключением устанавливает значение сигнала упомянутого сигнала sel2 в качестве (111000) в указанном порядке со схемы 120-1 выбора по схему 120-6 выбора. С другой стороны, в случае, в котором первый блок 107 переключения выполняет действие на Фиг.3A, блок 108 управления переключением устанавливает значение сигнала упомянутого сигнала sel2 в качестве (000000) в указанном порядке со схемы 120-1 выбора по схему 120-6 выбора.

[0068] Соответственно, битовые числа, выводимые в линии с C0 по C6 данных, когда первый блок 107 переключения задействован в конфигурации на Фиг.3A, идентичны битовым числам, когда первый блок 107 переключения задействован в конфигурации на Фиг.3B.

[0069] Таким образом данное действие может быть подходящим образом исполнено в случае, в котором запоминающий избыточный бит элемент в запоминающем блоке 104 в каждом столбце удерживает либо самый старший бит счетного сигнала, либо самый младший бит. Запоминающий избыточный бит элемент в запоминающем блоке 104 в каждом столбце не должен удерживать сигнал самого старшего бита или самого младшего бита счетного сигнала, а может удерживать сигнал одного из битов счетного сигнала.

[0070] Кроме того, согласно настоящему примерному варианту осуществления по отношению к пикселям 10 в одном столбце предоставлен один блок АЦ-преобразования, однако могут быть внедрены и другие варианты размещения. Например, для совместного использования пикселями 10 в двух столбцах предоставляется один блок АЦ-преобразования, или по отношению к пикселям 10 в одном столбце могут предоставляться два блока АЦ-преобразования.

[0071] Следует отметить, что согласно настоящему примерному варианту осуществления в случае, в котором также не существует никакой неисправности в запоминающем бит элементе в запоминающем блоке 104, первый блок 107 переключения выводит счетный сигнал в линию BD данных как на Фиг.2A или на Фиг.3A. В качестве другого примера, в случае, в котором в запоминающем бит элементе в запоминающем блоке 104 не существует никакой неисправности, может быть приемлемо, если первый блок 107 переключения не выводит счетный сигнал в линию BD данных.

[0072] Следует отметить, что согласно настоящему примерному варианту осуществления счетный сигнал является 6-битовым сигналом, однако приемлемо, если счетный сигнал является 2-битовым сигналом или выше.

Второй примерный вариант осуществления

[0073] Теперь относительно устройства захвата изображения согласно настоящему примерному варианту осуществления будет, главным образом, описана конфигурация, отличающаяся от конфигурации первого примерного варианта осуществления.

[0074] Конфигурация устройства захвата изображения согласно настоящему примерному варианту осуществления является той же самой, что и изображенная на Фиг.1. Однако, согласно настоящему примерному варианту осуществления для запоминающего блока 104 в каждом столбце предоставлено два запоминающих избыточные биты элемента.

[0075] На Фиг.4A показана конфигурация первого блока 107 переключения согласно настоящему примерному варианту осуществления. Также на Фиг.4A компоненту, имеющему ту же самую функцию, что и на Фиг.2A, назначена та же самая ссылочная позиция, что и на Фиг.2A. Первый блок 107 переключения согласно настоящему примерному варианту осуществления включает в себя каскад 112 выбора в первом каскаде, включающем в себя схемы с 1110-1 по 1110-5 выбора, и каскад 113 выбора во втором каскаде, включающем в себя схемы с 1111-1 по 1111-6 выбора. Сигнал sel1, выводимый из блока 108 управления переключением, является 11-битовым сигналом.

[0076] Измерительный счетчик 106 выводит 6-битовый счетный сигнал в соответствующие линии с A0 по A5 данных. Каскад 112 выбора в первом каскаде и каскад 113 выбора во втором каскаде соответственно выводят сигналы соответствующих битов счетного сигнала в линии с B0 по B5 данных, линию BD 1 данных и линию BD 2 данных в соответствии со значением сигнала упомянутого сигнала sel1. В случае, в котором все сигналы, вводимые в соответствующие схемы выбора сигнала sel1, имеют значение 0 как на Фиг.4A, то сигналы битов с [0] по [5] счетного сигнала выводятся в линии с B0 по B5 данных в указанном порядке. Сигнал бита [5] счетного сигнала выводится как в линию BD 1 данных, так и в линию BD 2 данных.

[0077] На Фиг.4A показано первое действие. В первом действии, упоминаемом в данном документе, сигнал бита [4], соответствующий сигналу первого бита, удерживается в запоминающем бит элементе, соединенном с линией B4 данных, соответствующей первому запоминающему бит элементу. Впоследствии, сигнал бита [5], соответствующий второму биту, который является битом более высокого порядка по отношению к первому биту на один бит, удерживается в запоминающем бит элементе, соединенном с линией B5 данных.

[0078] Далее, со ссылкой на Фиг.4B будет описано действие первого блока 107 переключения. На Фиг.4B показано действие в случае, в котором обнаружены неисправности в запоминающих биты элементах, соединенных с линией B3 данных и линией B5 данных, во множестве запоминающих блоков 104. Случай, в котором неисправности обнаружены в запоминающих биты элементах, соединенных с линией B3 данных и линией B5 данных, относится, например, к случаю, в котором запоминающий бит элемент, соединенный с линией B3 данных, имеет неисправность в конкретном запоминающем блоке 104, и запоминающий бит элемент, соединенный с линией B5 данных, в другом запоминающем блоке 104 имеет неисправность. Кроме того, в качестве другого примера такое действие может быть применено к случаю, в котором как запоминающие биты элементы, соединенные с линией B3 данных, так и запоминающий бит элемент, соединенный с линией B5 данных, в одном запоминающем блоке 104 имеют неисправность.

[0079] На Фиг.4B показано второе действие. Второе действие, упоминаемое в данном документе, является действием, в котором сигнал бита [4], соответствующий сигналу первого бита, удерживается в запоминающем избыточный бит элементе, соединенном с линией BD 1 данных, а сигнал бита [5], соответствующий сигналу второго бита, удерживается в запоминающем избыточный бит элементе, соединенном с линией BD 2 данных.

[0080] Блок 108 управления переключением устанавливает значение сигнала битов, выводимых в схему 1111-6 выбора, схему 1110-5 выбора и схему 1110-4 выбора, в качестве 1 и значение сигнала битов, выводимых в другие схемы выбора, в качестве 0 для сигнала sel1. Соответственно, сигналы битов с [0] по [2] счетного сигнала соответственно выводятся в линии с B0 по B2 данных. Сигнал бита [3] счетного сигнала выводится в линию B4 данных. Сигналы битов [4] и [5] счетного сигнала соответственно выводятся в линию BD 1 данных и линию BD 2 данных.

[0081] Таким образом счетный сигнал может быть удержан в запоминающем блоке 104 в каждом столбце в устройстве захвата изображения согласно настоящему примерному варианту осуществления даже в случае существования неисправностей в соответствующих запоминающих биты элементах во взаимно различных запоминающих блоках, то есть, в случае, в котором неисправности существуют во множестве запоминающих биты элементов, соединенных с взаимно различными линиями данных.

[0082] На Фиг.5 показана конфигурация и действие второго блока 111 переключения согласно настоящему примерному варианту осуществления. Также на Фиг.5 компоненту, имеющему ту же самую функцию, что и на Фиг.2C, назначена та же самая ссылочная позиция, что и на Фиг.2C. На Фиг.5 показано действие в случае, в котором первый блок 107 переключения выполняет действие с Фиг.4B. Второй блок 111 переключения включает в себя каскад 114 выбора в первом каскаде, включающем в себя схемы с 1200-1 по 1200-7 выбора, и каскад 115 выбора во втором каскаде, включающем в себя схемы с 1210-1 по 1210-6 выбора. Сигнал sel2, выводимый блоком 108 управления переключением, является 13-битовым сигналом. Блок 108 управления переключением устанавливает значение сигнала битов, выводимых в схему 1200-6 выбора, схему 1200-7 выбора, схему 1210-4 выбора, схему 1210-5 выбора и схему 1210-6 выбора, в качестве 1 и значение сигнала битов, выводимых в другие схемы выбора, в качестве 0 для сигнала sel2. Несмотря на то, что не изображено на чертеже, в случае, в котором первый блок 107 переключения выполняет действие с Фиг.4A, блок 108 управления переключением устанавливает значение сигнала всех битов сигнала sel2 в качестве 0. Соответственно, битовые числа, счетного сигнала, выводимого в линии с C0 по C5 данных, могут быть соответственно идентичны друг другу в случае, в котором первый блок 107 переключения выполняет либо действие с Фиг.4A, либо действие с Фиг.4B. Соответственно, устройство захвата изображения согласно настоящему примерному варианту осуществления может получать тот же самый технический результат, что и технический результат, описанный согласно первому примерному варианту осуществления. Кроме того, даже в случае, в котором неисправности обнаружены во множестве запоминающих биты элементов во множестве запоминающих блоков 104, устройство захвата изображения согласно настоящему примерному варианту осуществления может удерживать счетный сигнал в запоминающем блоке 104 в каждом столбце, не ощущая нехватку битов.

[0083] Следует отметить, что согласно настоящему примерному варианту осуществления изображен пример, в котором запоминающий избыточный бит элемент удерживает сигнал бита [5], однако такой запоминающий избыточный бит элемент может удерживать другой бит счетного сигнала.

[0084] Например, теперь будет описан пример, в котором запоминающий избыточный бит элемент удерживает сигнал бита [0].

[0085] На Фиг.6A показано действие, выполняемое первым блоком 107 переключения для вывода сигнала бита [0] в линию BD 1 данных и линию BD 2 данных.

[0086] На Фиг.6A показано первое действие. В первом действии, упоминаемом в данном документе, сигнал бита [0], соответствующий сигналу первого бита, удерживается в запоминающем бит элементе, соединенном с линией B0 данных, соответствующем первому запоминающему бит элементу. Впоследствии, сигнал бита [1], соответствующий второму биту, который является битом более высокого порядка по отношению к первому биту на один бит, удерживается запоминающим бит элементом, соединенным с линией B1 данных.

[0087] На Фиг.6B показано действие в случае, в котором обнаружены неисправности в запоминающих биты элементах, соединенных с линией B1 данных и линией B3 данных. Блок 108 управления переключением устанавливает значение сигнала соответствующих битов сигнала sel1, выводимого в схемы 1111-4, 1111-3, 1111-2, 1111-1, 1110-2 и 1110-1 выбора, в качестве 1 и значение сигнала соответствующих битов сигнала sel1, выводимого в другие схемы выбора, в качестве 0. Соответственно, первый блок 107 переключения выводит сигнал бита [0] в линию BD 2 данных и выводит сигнал бита [1] в линию BD 1 данных. Кроме того, первый блок 107 переключения выводит сигнал бита [2] в линию B0 данных и выводит сигнал бита [3] в линию данных B2. Кроме того, первый блок 107 переключения выводит сигнал бита [4] в линию B4 данных и выводит сигнал бита [5] в линию B5 данных.

[0088] На Фиг.6B показано второе действие. Второе действие, упоминаемое в данном документе, является действием, в котором сигнал бита [0], соответствующий сигналу первого бита, удерживается в запоминающем избыточный бит элементе, соединенном с линией BD 2 данных, а сигнал бита [1], соответствующий сигналу первого бита, удерживается в запоминающем избыточный бит элементе, соединенном с линией BD 1 данных.

[0089] На Фиг.7 показано действие второго блока 111 переключения в случае, в котором первый блок 107 переключения выполняет действие с Фиг.6B. Относительно сигнала sel2 блок 108 управления переключением устанавливает значения сигнала соответствующих битов сигнала sel2, выводимого в схемы 1200-1, 1200-2, 1200-3, 1200-4, 1200-5, 1210-1, 1210-2 и 1210-3 выбора, в качестве 1 и устанавливает значения сигнала битов, выводимых в другие схемы выбора, в качестве 0. С другой стороны в случае, в котором первый блок 107 переключения выполняет действие, изображенное на Фиг.6A, блок 108 управлени