Процессор, способ, система и изделие для векторного индексированного доступа к памяти плюс арифметической и/или логической операции

Иллюстрации

Показать всеИспользование: для выполнения инструкций с использованием процессора. Сущность изобретения заключается в том, что процессор включает в себя блок декодирования для приема инструкции векторной индексированной загрузки плюс арифметической и/или логической (A/L) операции плюс сохранения. Инструкция предназначена для указания исходного операнда упакованных индексов памяти, имеющего множество упакованных индексов памяти. Инструкция также указывает исходный операнд упакованных данных, имеющий множество элементов упакованных данных. Процессор также включает в себя исполнительный блок, соединенный с блоком декодирования. Исполнительный блок, в ответ на инструкцию, загружает множество элементов данных из ячеек памяти, соответствующих множеству упакованных индексов памяти, выполняет A/L операции на множестве элементов упакованных данных исходного операнда упакованных данных и загруженном множестве элементов данных и сохраняет множество элементов результирующих данных в ячейках памяти, соответствующих множеству упакованных индексов памяти. Технический результат: обеспечение возможности повышения производительности процессора. 4 н. и 21 з.п. ф-лы, 29 ил.

Реферат

Область техники, к которой относится изобретение

Варианты осуществления, описанные в данном документе, в основном, относятся к микропроцессорам. В частности, варианты осуществления, описанные в данном документе, в основном, относятся к микропроцессорам, обеспечивающим доступ к памяти в ответ на инструкции.

Уровень техники

Процессоры обычно используются для выполнения инструкций для доступа к системной памяти. Например, процессоры могут выполнять инструкции загрузки для загрузки или считывания данных из системной памяти и/или инструкции сохранения для хранения или записи данных в системной памяти.

Некоторые процессоры используются для выполнения векторных индексированных инструкций загрузки (например, для загрузки векторных элементов с использованием векторных индексов). Эти векторные индексированные инструкции загрузки также упоминаются в данной области техники как векторные инструкции сбора или просто gather-инструкции. Intel® справочник по программированию по усовершенствованному вектору расширения, справочный номер документа 319433-011, опубликовано в июне 2011, описывает несколько векторных gather-инструкций (VGATHER). Примеры включают в себя VGATHERDPD, VGATHERQPD, VGATHERDPS, VGATHERQPS, VPGATHERDD, VPGATHERQD, VPGATHERDQ и VPGATHERQQ. Эти инструкции сбора могут использоваться для сбора или загрузки множества элементов данных из памяти с использованием множества соответствующих индексов памяти.

Некоторые процессоры используются для выполнения векторных индексированных инструкций для сохранения данных (например, сохранить векторные элементы с использованием векторных индексов). Эти векторные индексированные инструкции на сохранение данных также упоминаются в данной области техники, как векторные инструкции разброса или просто scatter-инструкции. Intel® справочник по программированию по архитектуре расширения набора инструкций, справочный номер документа 319433-015, опубликован в июле 2013, описывает несколько векторных scatter-инструкций (VSCATTER). Эти инструкции разброса могут использоваться для разнесенияпо разным участкам памяти или хранения нескольких элементов данных из исходного операнда в системную память, используя множество соответствующих индексов памяти.

Краткое описание чертежей

Изобретение описывается со ссылкой на прилагаемые чертежи, иллюстрирующие варианты осуществления, а именно:

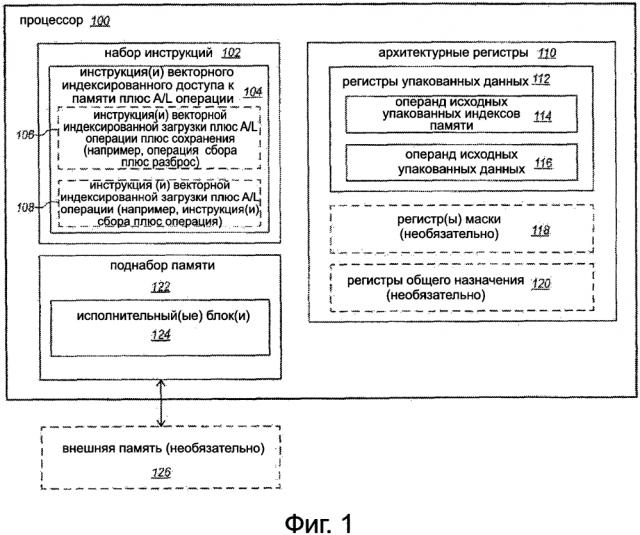

Фиг. 1 представляет собой блок-схему варианта осуществления процессора, который выполнен с возможностью выполнять одну или более инструкций векторного индексированного доступа к памяти плюс арифметическую и/или логическую операцию.

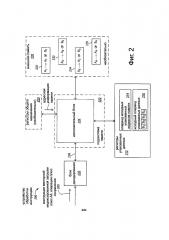

Фиг. 2 представляет блок-схему варианта осуществления устройства обработки инструкции, которое выполнено с возможностью выполнять одну или более инструкций векторного индексированного доступа к памяти плюс арифметическую и/или логическую операцию.

Фиг. 3 представляет собой блок-схему, иллюстрирующую один вариант осуществления структуры расположения исполнительного блока в процессоре.

Фиг. 4 является блок-схемой алгоритма варианта осуществления способа обработки варианта осуществления векторной индексированной инструкции загрузки плюс арифметической и/или логической операции плюс хранение.

Фиг. 5 представляет собой блок-схему, иллюстрирующую вариант осуществления векторной индексированной инструкции загрузки плюс арифметической и/или логической операции плюс операции сохранения.

Фиг. 6 представляет собой блок-схему, иллюстрирующую вариант осуществления замаскированной векторной индексированной инструкции загрузки плюс арифметической и/или логической операции плюс операции сохранения.

Фиг. 7 представляет блок-схему, иллюстрирующую вариант осуществления векторной индексированной инструкции загрузки плюс арифметической и/или логической операции.

Фиг. 8 является блок-схемой варианта осуществления формата для векторной индексированной инструкции загрузки плюс арифметической и/или логической операции плюс инструкции сохранения.

Фиг. 9 является блок-схемой варианта осуществления формата для векторной индексированной инструкции загрузки плюс арифметической и/или логической операции.

Фиг. 10 представляет собой блок-схему примера варианта осуществления конкретного подходящего набора упакованных данных регистров.

Фиг. 11 представляет собой блок-схему примера варианта осуществления конкретного подходящего набора упакованных данных операции маскирования регистров.

Фиг. 12 является схемой, иллюстрирующей пример варианта осуществления конкретных подходящих 64-разрядных упакованных данных операции маскирования регистров.

Фиг. 13А является блок-схемой, иллюстрирующей универсальный векторный дружественный формат инструкции и шаблоны инструкции класса А согласно вариантам осуществления изобретения.

Фиг. 13В является блок-схемой, иллюстрирующей универсальный векторный дружественный формат инструкции и шаблоны инструкции класса В согласно вариантам осуществления изобретения.

Фиг. 14А представляет собой блок-схему, иллюстрирующую примерный конкретный векторный дружественный формат инструкции согласно вариантам осуществления изобретения.

Фиг. 14В является блок-схемой, иллюстрирующей поля конкретного векторного дружественного формата инструкции, образующие полное поле кода операции согласно одному варианту осуществления изобретения.

Фиг. 14С является блок-схемой, иллюстрирующей поля конкретного векторного дружественного формата инструкции, образующие поле индекса регистра согласно одному варианту осуществления изобретения.

Фиг. 14D является блок-схемой, иллюстрирующей поля конкретного векторного дружественного формата инструкции, образующие поле операции приращения согласно одному варианту осуществления изобретения.

Фиг. 15 представляет блок-схему архитектуры регистра согласно одному варианту осуществления изобретения.

Фиг. 16А представляет собой блок-схему, иллюстрирующую оба примерный упорядоченный конвейер и примерный порядок переименования регистров, конвейер с изменением выполнения последовательности команд согласно вариантам осуществления изобретения.

Фиг. 16В показывает ядро процессора, включающее в себя блок предварительной обработки данных, соединенный с блоком механизма исполнения, и оба соединены с блоком памяти.

Фиг. 17А является блок-схемой одноядерного процессора, подключенного к накристальному межсетевому соединению и с ее локальным подмножеством кэша уровня 2 (L2), согласно вариантам осуществления изобретения.

Фиг.17В представляет собой развернутый вид части ядра процессора, показанного на фиг. 17А, согласно вариантам осуществления изобретения.

Фиг. 18 представляет собой блок-схему процессора, который может иметь более одного ядра, может иметь интегрированный контроллер памяти и может иметь интегрированный графический блок согласно вариантам осуществления изобретения.

Фиг. 19 показывает блок-схему системы в соответствии с одним вариантом осуществления настоящего изобретения.

Фиг. 20 показывает блок-схему первого более конкретного примера системы в соответствии с вариантом осуществления настоящего изобретения.

Фиг. 21 показывает блок-схему второго более конкретного примера системы в соответствии с вариантом осуществления настоящего изобретения.

Фиг. 22 показывает блок-схему SoC в соответствии с вариантом осуществления настоящего изобретения.

Фиг. 23 представляет собой блок-схему, на которой представлена сравнительная информация относительно использования преобразователя инструкций для преобразования двоичных инструкций в исходном наборе инструкций в двоичные инструкции в целевом наборе инструкций согласно вариантам осуществления изобретения.

Подробное описание вариантов осуществления

Приведенное в настоящем документе описание относится к инструкциям векторного индексированного доступа к памяти плюс арифметической и/или логической (A/L) операции, процессорам для исполнения таких инструкций, способам, выполняемых процессорами при обработке или выполнении таких инструкций, и системам, включающие в себя один или более процессоров для обработки или выполнения таких инструкций. В следующем описании приводятся многочисленные конкретные подробные детали (напр., конкретные инструкции операций, форматы данных, конфигурации процессора, детали микроархитектуры, системные конфигурации, форматы команд, последовательности операций и др.). Впрочем, варианты осуществления могут быть реализованы на практике без этих конкретных деталей. В других случаях известные схемы, структуры и способы не были подробно проиллюстрированы, чтобы не усложнять понимание описания.

Фиг. 1 представляет собой блок-схему варианта осуществления процессора 100, выполненный с возможностью реализовывать или выполнять одну или более инструкций 104 векторного индексированного доступа к памяти плюс арифметической и/или логической (A/L) операции. Процессор соединен с возможной внешней памятью 126 (например, динамическая память с произвольным доступом (DRAM), флэш-память, другие системы памяти и др.). Память 126 показана, как возможная, потому что в некоторых вариантах осуществления процессор 100 описывается без памяти 126.

В некоторых вариантах осуществления процессор может быть процессором общего назначения (например, настольный, ноутбук, планшет, КПК, сотовый телефон как вычислительные устройства). В качестве альтернативы, процессор может быть специализированным процессором. Примеры подходящих специализированных процессоров включают в себя, но не ограничиваясь этим, графические процессоры, сетевые процессоры, коммуникационные процессоры, криптографические процессоры, сопроцессоры и цифровые сигнальные процессоры (DSPs), что представляет собой только несколько примеров. Процессор может быть любым из различных процессоров со сложным набором команд (CISC), различных процессоров с сокращенным набором команд (RISC), различных процессоров со сверх длинным командным словом (VLIW), различных их гибридных вариаций или других типов процессоров целиком.

Процессор включает в себя архитектурно-видимые или архитектурные регистры 110. Термин архитектурные регистры часто используется в данной области техники для обозначения тех регистров, которые видимы для программного обеспечения (например, программатор) и/или регистры, указанные инструкциями набора инструкций для идентификации операндов. Эти архитектурные регистры противопоставляются другим неархитектурным или неархитектурно видимым регистрам в данной микроархитектуре (например, регистры временного запоминания используются инструкциями и др.). Для простоты, эти архитектурные регистры будут часто упоминаться в данном документе просто как регистры. Регистры, как правило, представляют местоположения хранения данных на кристальном процессоре. Регистры могут быть реализованы по-разному в разных микроархитектурах, используя известные технологии, и не ограничиваются каким-либо конкретным типом схемы. Примеры подходящих типов регистров включают в себя, но не ограничиваются этим, выделенные физические регистры, динамически выделенные физические регистры, используя переименование регистров и их комбинации. Иллюстрированные регистры включают в себя набор векторных или упакованных данных регистров 112, каждый выполнен с возможностью хранить векторные или упакованные данные. В некоторых вариантах осуществления регистры могут также возможно включать в себя упакованные данные операции маскировки регистров 118, хотя это не обязательно. В некоторых вариантах осуществления регистры могут также включать в себя регистры 120 общего назначения, хотя это не обязательно.

Процессор имеет набор 102 инструкций. Набор инструкций включает в себя набор инструкций, которые поддерживаются процессором. Инструкции из набора команд представляют собой инструкции языка ассемблера, инструкции машинного уровня, макроинструкции или инструкции для выполнения процессором, в отличие от микроинструкций, микро-ops или инструкции, которые являются результатом декодирования макроинструкций посредством блока декодирования и предоставляются для выполнения в исполнительный блок. Набор инструкций включает в себя одну или более инструкций 104 векторного индексированного доступа к памяти плюс арифметической и/или логической (A/L) операции. Каждая одна или более инструкций векторного индексированного доступа к памяти плюс A/L операции выполнена с возможностью вызывать процессор выполнить операцию векторного индексированного доступа к памяти совместно с векторной A/L операцией.

В некоторых вариантах осуществления одна или более инструкций 104 векторного индексированного доступа к памяти плюс A/L операции может возможно включать в себя одну или более инструкций 106 векторной индексированной загрузки плюс A/L операции плюс операции сохранения (например, одну или более gather-плюс A/L операции плюс scatter-инструкции). Для примера, в некоторых вариантах осуществления инструкция 106 векторной индексированной загрузки плюс A/L операции плюс операции сохранения (например, инструкция gather-плюс A/L операции плюс scatter-инструкция) может быть выполнена с возможностью вызывать процессор собирать элементы данных из ячеек памяти во внешней памяти 126, указанные исходным операндом 114 упакованных индексов памяти, выполнять A/L операции на собранных элементах данных и элементов данных исходного операнда 116 упакованных данных, и разбрасывать полученные элементы данных в ячейках памяти во внешней памяти 126, указанные исходным операндом 114 упакованных индексов памяти.

В некоторых вариантах осуществления, одна или более инструкции 104 векторного индексированного доступа к памяти плюс A/L операции может возможно включать в себя одну или более инструкций 108 векторной индексированной загрузки плюс A/L операции (например, одну или более gather-инструкции плюс A/L операции). Для примера, в некоторых вариантах осуществления, инструкция 108 векторной индексированной загрузки плюс A/L операции (например, gather-инструкция плюс A/L операции) может быть выполнена с возможностью вызывать процессор собирать элементы данных из ячеек памяти во внешней памяти 126, указанными исходным операндом 114 упакованных индексов памяти, выполнять A/L операцию на собранных элементах данных и элементах данных исходного операнда 116 упакованных данных, и сохранение полученных элементов данных, как результат упаковки данных, на местах хранения процессора (например, в одном или более упакованных данных регистров).

Различные типы векторных A/L операций пригодны для инструкций 104. Некоторые примеры подходящих A/L операций включают в себя, но не ограничиваются этим, векторные или упакованные операции сложения, операции вычитания, операции умножения, операции деления, операции умножения-сложения, операции сдвига, операции поворота, операции логики И, операции логики ИЛИ, операции логики НЕТ, операции логики И-НЕТ, операции осреднения, операции максимизации, операции минимизации и операции сравнения, что представляет собой только некоторые из возможных примеров. В различных вариантах осуществления, могут использоваться в любом месте от одной инструкции 104 векторного индексированного доступа к памяти плюс A/L операции до многих таких разных инструкций. Например, может быть несколько или много gather-инструкций плюс операция плюс scatter-инструкций для различных типов A/L операций (например, добавление, умножение, сдвиг и др.) и/или несколько или много gather-инструкций плюс различные типы A/L операций.

В некоторых вариантах осуществления, инструкции 104 могут возможно указывать на упакованные данные операции маскировки операнда в маскированных регистрах 118, хотя это не обязательно. Упакованные данных операции маскировки операндов и упакованные данные операции маскированных регистров будут дополнительно рассмотрены ниже. В некоторых вариантах осуществления, инструкции 104 могут возможно указывать на (например, неявно указывать) регистр 120 общего назначения (например, один, имеющий базовый адрес или другую адресную информацию памяти), хотя это не обязательно. Альтернативно, адресная информация памяти может быть предоставлена иным способом.

Процессор также включает в себя один или несколько исполнительных блоков 124. Исполнительный блок(и) выполнен с возможностью реализовывать или выполнять инструкцию(и) 104 векторного индексированного доступа к памяти плюс A/L операции. Примеры подходящих исполнительных блоков включают в себя, но не ограничены этим, блоки доступа к памяти, исполнительные блоки памяти, блоки сбора данных, блоки разброса данных, арифметические и/или логические блоки (ALUs) и тому подобное, и их комбинации. В некоторых вариантах осуществления исполнительный блок памяти (или другой блок, способный осуществлять сбор или разброс данных или другую операцию векторного индексированного доступа к памяти) может быть модифицирован, чтобы включать в себя арифметический и/или логический блок или схему. В других вариантах осуществления исполнительный блок памяти (или другие блоки, способные осуществлять сбор или разброс данных или другую операцию векторного индексированного доступа к памяти) могут быть соединены с A/L блоком или схемой. В некоторых вариантах осуществления один или несколько исполнительных блоков 124 могут быть включены в состав подсистемы 122 памяти, которая используется для доступа к внешней памяти 126.

Фиг. 2 представляет собой блок-схему варианта осуществления устройства 200 обработки инструкции. В некоторых вариантах осуществления, устройство 200 обработки инструкции может быть, или может быть включено в состав, процессора 100, показанного на фиг. 1. Признаки и детали, описанные выше, для процессора 100 могут также возможно применяться к устройству 200 обработки инструкции. Альтернативно, устройство 200 обработки инструкции может быть, или может быть включено в состав, аналогичным или другим процессором, чем процессор 100. Кроме того, процессор 100 может включать в себя аналогичное или иное устройство обработки инструкции, чем устройство 200 обработки инструкции.

Устройство 200 обработки инструкции соединено к возможной внешней памяти 226 (например, динамической памяти с произвольным доступом (DRAM), флэш-памяти, другим системам памяти и др.). Например, устройство обработки инструкции и внешняя память могут быть соединены посредством шины или других межсоединений на печатной плате, через набор микросхем или другим образом, известным в данной области техники. Внешняя память отображается как возможная, потому что некоторые варианты осуществления относятся к устройству обработки инструкции без внешней памяти (например, перед установкой процессора в систему).

Устройство 200 обработки инструкции может принимать инструкцию 206 векторной индексированной загрузки плюс A/L операции плюс сохранения. Например, инструкция может быть принята из блока доставки инструкции, очереди команд, памяти и т.д. В некоторых вариантах осуществления, инструкция 206 может представлять собой инструкцию сбора плюс A/L операции плюс разброса. Инструкция 206 может четко определять (например, через один или более битов или поле) или иным образом (например, неявно указывать, указывать косвенно посредством эмуляции сопоставления регистра и др.) указывать исходный операнд 214 упакованных индексов памяти, имеющий множество упакованных индексов памяти. Каждый индекс памяти в исходном операнде упакованных индексов памяти может указывать на соответствующее место в памяти во внешней памяти 226. В некоторых вариантах осуществления индексы памяти могут быть 16-бит, 32-бит или 64-битными индексами памяти, хотя объем изобретения этим не ограничен. В некоторых вариантах осуществления, инструкция 206 может также явно указывать (например, через один или более битов или поле) или иным образом (например, неявно указывать, указывать косвенно через эмуляцию сопоставление регистров и др.) указывать исходный операнд 216 упакованных данных, имеющий множество элементов упакованных данных.

Устройство включает в себя набор регистров 212 упакованных данных. Регистры упакованных данных могут представлять собой архитектурные регистры. Регистры могут быть реализованы по-разному в различных микроархитектурах, используя известные технологии, и не ограничиваются каким-либо конкретным типом схемы. Примеры подходящих типов регистров включают в себя, но не ограничиваются этим, выделенные физические регистры, динамически выделенные физические регистры, используя переименование регистров, и их комбинации. Как показано, в некоторых вариантах осуществления исходный операнд 214 упакованных индексов памяти и исходный операнд 216 упакованных данных могут храниться в регистрах упакованных данных. Например, инструкция 206 может иметь одно или более полей или набор битов, чтобы указать эти регистры упакованных данных в качестве исходных операндов. Альтернативно, в других местах хранения может возможно использоваться для одного или более из этих операндов.

Устройство 200 обработки инструкции включает в себя блок декодирования инструкций или декодер 230. В некоторых вариантах осуществления блок декодирования может располагаться в ядре. Блок декодирования может принимать и декодировать машинные инструкции более высокого уровня или макроинструкции (например, инструкция 206) и выводить одну или более микроинструкций низкого уровня, микрокод точки входа, микроинструкции или другие низкоуровневые инструкции или управляющие сигналы 236, что соответствуют и/или получают из исходной инструкции более высокого уровня. Одна или более низкоуровневых инструкций или управляющие сигналы могут выполнять операцию инструкции более высокого уровня в рамках одной или более низкоуровневой операции (например, уровня схемы или на аппаратном уровне). Блок декодирования может быть реализован с помощью различных механизмов, включающие в себя, но не ограничиваясь этим, памяти микрокода только для чтения (ROMs), справочные таблицы, аппаратные реализации, программируемые логические матрицы (PLAs) и другие механизмы, известные в данной области техники. В других вариантах осуществления, вместо блока декодирования могут быть использованы эмулятор инструкций, переводчик, интерпретатор или другие логические блоки преобразования инструкции (например, реализованные в программном обеспечении, аппаратных средствах, микропрограммном обеспечении или их комбинациях). В еще других вариантах осуществления может быть использована комбинация логических блоков преобразования инструкции (например, модуль эмуляции) и блока декодирования. Некоторые или все логические блоки преобразования инструкций могут потенциально быть размещены вне кристалла от остальной части устройства обработки инструкций, например, на отдельном кристалле и/или памяти.

Обращаясь снова к фиг. 2, один или несколько исполнительных блоков 224 соединены с блоком 230 декодирования, регистрами 212 упакованных данных и с внешней памятью 226. В некоторых вариантах осуществления один или несколько исполнительных блоков могут также возможно быть соединены с регистрами 220 общего назначения, которые могут возможно использоваться для хранения базового адреса и/или другой адресной информации памяти для преобразования индексов памяти в адреса памяти. Альтернативно, адресная информация памяти может быть предоставлена иным образом.

Исполнительный блок выполнен с возможностью, в ответ на и/или как результат инструкции 206 векторной индексированной загрузки плюс A/L операции плюс сохранения (например, в ответ на один или более управляющих сигналов 236 декодированный или иным образом преобразованный из инструкции 206, или в ответ на один или более управляющий сигнал 236 декодированный из одной или более инструкций, используемый для эмуляции инструкция 206) выполнять операцию векторной индексированной загрузки плюс A/L операцию плюс операцию сохранения. Операция загрузки, A/L операция и операция сохранения могут все представлять собой векторные операции. В некоторых вариантах осуществления, операция может включать в себя процессорный сбор данных или иной способ загрузки множества элементов данных из потенциально несмежных ячейках памяти во внешней памяти 226, обозначаемой соответствующими индексами памяти исходного операнда 214 упакованных индексов памяти, выполнения A/L операцию на собранных или загруженных элементах данных и ассоциированных элементах данных исходного операнда 216 упакованных данных, и разброс или иной способ сохранения результирующих элементов данных в соответствующих ячейках памяти во внешней памяти 226, указанные соответствующими индексами памяти исходного операнда 214 упакованных индексов памяти.

В иллюстрируемом примере варианта осуществления, первая ячейка 232 памяти изначально включает в себя элемент А1 данных, вторая ячейка 233 памяти изначально включает в себя элемент А2 данных, третья ячейка 234 памяти изначально включает в себя элемент A3 данных и четвертая ячейка 235 памяти изначально включает в себя элемент А4 данных. Каждая из этих ячеек памяти соответственно может соответствовать с первого по четвертый индексы памяти исходного операнда 214 упакованных индексов памяти. Исходный операнд 216 упакованных данных включает в себя соответствующие элементы B1, В2, В3 и В4 данных. В результате выполнения инструкции, элемент А1 данных в первой ячейке 232 памяти может быть перезаписан с А1 посредством операции (ОР) на В1, элемент А2 данных во второй ячейке 233 памяти может быть перезаписан с А2 OP В2, элемент A3 данных в третьей ячейке 234 памяти может быть перезаписан с A3 ОР В3 и данные А4 элемента в четвертой ячейке 235 памяти может быть перезаписан с А4 OP В4. В этом примерном варианте осуществления, операция (ОР) может представлять собой любую подходящую операцию "вертикального" типа упакованных данных, например, упакованное сложение, упакованное вычитание, упакованное умножение, упакованное деление, упакованное умножение-сложение, упакованный сдвиг (например, сдвиг А1 на В1, сдвиг А2 на В2 и т.д.), упакованный поворот (например, поворот А1 на В1, поворот А2 на В2 и т.д.), упакованная логическая И, упакованная логическая ИЛИ, упакованная логическая НЕ, упакованная логическая И-НЕТ, упакованные усреднения, упакованная максимизация, упакованная минимизация, упакованное сравнение или тому подобное. Хотя в этом примере "вертикальные" операции будут использоваться в операции, выполняемой на паре соответствующих элементов данных (например, элементов данных в соответствующих позициях битов в операндах), и "вертикальный" тип операции не требуется. В других вариантах осуществления, другие виды операций могут быть выполнены, такие как, например, "горизонтальный" тип операции, часть "горизонтальной" операции, часть "вертикальной" операции, операции с участием более чем просто один элемент данных и т.д.

Примеры подходящих исполнительных блоков включают в себя, но не ограничены этим, блоки доступа к памяти, исполнительные блоки памяти, блоки сбора данных, блоки разброса данных, арифметические и/или логические блоки (ALUs) и тому подобное, и их комбинации. В некоторых вариантах осуществления исполнительный блок памяти (или другой блок, способный осуществлять операцию сбора и/или разброса и/или другие операции векторного индексированного доступа к памяти), может быть изменен, чтобы включать в себя арифметический и/или логический блок или схему. В других вариантах осуществления исполнительный блок памяти (или другой блок, способный осуществлять операцию сбора и/или разброса и/или другие операции векторного индексированного доступа к памяти) может быть соединен с арифметическим и/или логическим блоком или схемой. Один или несколько исполнительных блоков и/или устройство может содержать специфическую или конкретную логику (например, схему, транзисторы или другие аппаратные средства, потенциально объединенные с программным обеспечением и/или аппаратно-программным обеспечением), выполненную с возможностью выполнять и/или обрабатывать инструкцию 206. В некоторых вариантах осуществления один или несколько исполнительных блоков могут включать в себя, по меньшей мере, некоторые транзисторы, интегральную схему, часть интегральной схемы или другую схему или оборудование.

В некоторых вариантах осуществления, один или несколько исполнительных блоков 224 могут быть включены в состав подсистемы 222 памяти, которая используется для доступа к внешней памяти 226, хотя это не обязательно. Как будет рассмотрено дополнительно ниже, как правило, чем ближе один или несколько исполнительных блоков 224 к внешней памяти 226, тем выше эффективность. Например, это может быть отчасти из-за не необходимости хранить данные на одном или более высоком уровне кэша и/или нет необходимости передавать данные по межсоединению всем, вплоть до самого высокого уровня кэша и/или в ядро.

С целью упрощения описания, была проиллюстрирована простая структура устройства 200 обработки инструкции, хотя устройство обработки инструкции может возможно включать в себя один или более других компонентов. Примеры таких обычных компонентов включают в себя, но не ограничиваются ими, блок выборки инструкций, блок планирования инструкции, блок предсказания ветви, кэш данных и инструкции, буферы предыстории преобразования данных (TLB), буферы предварительной выборки, очереди микроинструкции, устройства, задающие последовательность микроинструкций, блоки шинного интерфейса, блок удаления/подтверждения, блок переименования регистра и другие компоненты, обычно используемые в процессорах. Кроме того, варианты осуществления могут иметь несколько ядер, логические процессоры или блок механизма исполнения, имеющие тот же или другой набор инструкций и/или ISA. Есть множество различных комбинаций и конфигураций таких компонентов в процессорах и варианты осуществления не ограничиваются какой-либо конкретной такой комбинацией или конфигурацией.

В некоторых вариантах осуществления, операция может быть выполнена посредством исполнительного блока, находящегося за пределами ядер (например, с помощью исполнительного блока, расположенного с и/или непосредственно последнего уровня кэша, предпоследнего уровня кэша или одного из последних уровней кэша. В некоторых вариантах осуществления, операция может быть выполнена с помощью исполнительного блока на данных, поставленных или полученных из последнего уровня кэша, предпоследнего уровня кэша или одного из последних уровней кэша. В некоторых вариантах осуществления один или несколько исполнительных блоков 224 могут быть логически развернуты на том же уровне иерархии памяти, как последний уровень кэшпамяти (или один из самых низких уровней кэш-памяти), в противоположность логическому развертыванию одного или нескольких исполнительных блоков 224 на высшем уровне кэша (или один из самых высоких уровней кэша). Обычно, чем выше уровень кэша между высоким уровнем кэша и уровнем иерархии памяти, на котором работает один или несколько исполнительных блоков, тем выше эффективность. В некоторых вариантах осуществления, операция может быть выполнена над данными, которые обходят все или, по меньшей мере, один или более высоких уровней кэша, что выше, чем кэш, из которого данные предоставляются (например, последний уровень кэша). В таких вариантах осуществления, собранные или иным образом загруженные данные, не должны передаваться ни в какой-либо более высокий уровень кэша и/или в ядро, до обработки и затем разбросаны или иным образом сохранены обратно в памяти. Целесообразно, избегая необходимости хранить эти данные на более высоких уровнях кэша, способствует освобождению пространства на более высоких уровнях кэша. Это освобожденное пространство может использоваться для хранения других данных, которые могут помочь улучшить производительность. Более того, в некоторых вариантах осуществления, операция может быть выполнена на данных, содержащихся в регистрах временного запоминания, в отличие архитектурных регистров. Это может помочь освободить архитектурные регистры так, чтобы они были доступны для использования другими инструкциями. Это может также помочь улучшить производительность (например, помогая уменьшить подкачку данных в регистрах и др.). Более того, может быть также уменьшена полоса пропускания соединения и/или других ресурсов, которые иным образом были бы необходимы для передачи данных на самый высокий или более высокий уровень кэша и/или в ядро. Такая ширина полосы пропускания соединения и/или иные ресурсы могут быть использованы для других целей, которые также могут помочь повысить производительность.

Фиг. 3 представляет собой блок-схему, иллюстрирующую один вариант осуществления расположения исполнительного блока 324 в процессоре 300. Процессор включает в себя один или более ядер 350. На чертеже, процессор включает в себя первое ядро 350-1, возможно N-e ядро 350-N, где N может представлять собой любое подходящее количества ядер. Первое ядро включает в себя блок 330 декодирования, который может быть аналогичен блокам декодирования, описанными в данном документе, и может декодировать инструкцию векторного индексированного доступа к памяти плюс A/L операции. Первое ядро также включает в себя исполнительный блок 351. Ядро также включает в себя архитектурные регистры 310, которые могут быть указаны инструкциями, выполненными первым ядром. Первое ядро дополнительно включает в себя кэш 352 первого уровня (L1) и возможно кэш 353 второго уровня (L2). Энное ядро может возможно быть схожим или таким же, как первой ядро, хотя это не обязательно. Процессор также включает в себя кэш 354 последнего уровня (LLC), соединенный с ядрами. Процессор также включает в себя блок 355 памяти, соединенный с LLC и ядрами. Блок памяти соединен с внешней памятью 326.

В некоторых вариантах осуществления блок памяти может включать в себя исполнительный блок, используемый для выполнения или реализации инструкции векторного индексированного доступа к памяти плюс A/L операции. Исполнительный блок включает в себя блок 356 доступа к памяти, который выполнен с возможностью выполнять операцию векторного индексированного доступа к памяти (например, операцию сбора и/или операцию разброса). Исполнительный блок также включает в себя блок 357 A/L, соединенный с блоком доступа к памяти. Блок A/L может быть выполнен с возможностью выполнить A/L операцию на данных, к которым разрешен доступ (например, загруженные векторные данные с помощью индексов). Блок 356 доступа к памяти и блок 357 A/L могут взаимодействовать или работать вместе, чтобы выполнять вариант реализации инструкции векторного индексированного доступа к памяти плюс A/L операции. В некоторых вариантах осуществления исполнительный блок 324 может выполнять операции над данными, загруженными из внешней памяти 326 перед загрузкой в LLC, будучи загруженными в LLC, или на данных, полученных из LLC после загрузки в LLC. В некоторых вариантах осуществления исполнительный блок 324 может выполнять операции над данными, которые отсутствуют в ядре 350, L1 кэш 352 или кэш L2 353. В некоторых вариантах осуществления исполнительный блок может включать в себя регистры 358 временного запоминания для содействия в выполнении этих инструкций. Например, регистры временного запоминания могут использоваться для хранения загруженных данных и/или промежуточных или временных данных, сгенерированных при выполнении инструкции. Использование таких регистров временного запоминания помогает избежать необходимости занимать архитектурные регистры 310.

Фиг. 4 представляет собой блок-схему варианта осуществления способа 460 обработки варианта осуществления инструкции векторной индексированной загрузки плюс A/L операции плюс операции сохранения. В различных вариантах осуществления способ может быть выполнен процессором общего назначения, процессором специального назначения или другим устройством обработки инструкций или цифровым логическим устройством. В некоторых вариантах осуществления, операции и/или способ, показанный на фиг. 4, могут быть выполнены посредством и/или в любых устройствах, показанных на фиг. 1-3. Компоненты, признаки и конкретные возможные детали, описанные в настоящем документе для устройства, показанного на фиг. 1-3, также возможно применяются к операц