Определение длины группы символьных данных, содержащей символ окончания

Иллюстрации

Показать всеГруппа изобретений относится к области обработки текста и может быть использована для определения длины символьных данных, в состав которых входит символ окончания. Техническим результатом является повышение производительности обработки. Символьные данные, длина которых подлежит определению, в параллельном режиме загружаются в один или более векторных регистров. Для загрузки данных в векторный регистр до определенной границы применяется команда, которая также предоставляет возможность определить число загруженных символов с использованием, например, другой команды. Затем применяется команда для определения индекса первого символа окончания, например пустого или нулевого символа, которая в параллельном режиме в данных выполняет поиск символа окончания. Применение этих команд позволяет определить длину символьных данных с использованием только одной команды ветвления. 2 н. и 23 з.п. ф-лы, 27 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение относится к сфере обработки текста. Более точно, изобретение относится к сфере обработке символьных данных.

Предпосылки создания изобретения

При работе с текстовой информацией часто требуется выполнять различные виды обработки символьных данных, в том числе обработку символьных строк. Некоторые виды обработки содержат поиск места окончания (например, конца строки), определение длины символьных данных, поиск определенного символа и т.д. Команды и/или приемы, применяемые в настоящее время для выполнения указанных видов обработки, становятся все менее эффективными.

Сущность изобретения

Для устранения недостатков уровня техники предлагается способ определения длины группы данных, включающий: загрузку в регистр из памяти данных, содержащихся в определенном блоке пространства памяти, причем загружаемые данные являются по меньшей мере частью указанной группы данных, длину которой требуется определить, а сама указанная группа данных, длину которой требуется определить, содержит символ окончания, указывающий конец этой группы данных и представляющий собой известное заранее определенное значение, выбранное в качестве значения, определяющего окончание группы данных, причем данные загружают от начального адреса до конечного адреса в памяти, конечный адрес вычисляют с использованием размера границы блока пространства памяти и маски границы, определяемой на основе размера границы и используемой для определения близости к определенной границе, из памяти загружают переменное число байтов данных без пересечения заданной границы блока пространства памяти, из которого данные загружают в регистр, а переменное число байтов основано на начальном адресе и конечном адресе; определение значения переменной-счетчика, отражающего количество загруженных в регистр данных; определение процессором для данных, загруженных в регистр, значения переменной окончания, используемой при определении длины группы данных, включающее проверку загруженных в регистр данных для определения того, содержат ли загруженные в регистр данные символ окончания в некотором местоположении в регистре, причем если загруженные в регистр данные содержат символ окончания, то переменной окончания присваивают значение, указывающее местоположение символа окончания в регистре, а если загруженные в регистр данные не содержат символа окончания, то переменной окончания присваивают заранее определенное значение, используемое при определении длины группы данных; проверку наличия дополнительных данных, которые должны быть учтены, выполняемую по значению переменной-счетчика и/или по значению переменной окончания, причем если проверка выявила наличие подлежащих учету дополнительных данных, то значение переменной-счетчика увеличивают в соответствии с количеством указанных дополнительных данных, и по значению переменной-счетчика определяют длину группы данных, а если проверка выявила отсутствие подлежащих учету дополнительных данных, то значение переменной-счетчика используют в качестве указанной длины группы данных.

Объектом изобретения является также компьютерная система для определения длины группы данных, содержащая запоминающее устройство и процессор, обменивающийся информацией с запоминающим устройством, и сконфигурированная для осуществления описанного выше способа.

С помощью способов, составляющих сущность настоящего изобретения, реализуются дополнительные особенности и преимущества. В данной заявке подробно описываются прочие варианты осуществления и аспекты настоящего изобретения, они рассматриваются как часть настоящего изобретения.

Таким образом, изобретение относится к способу определения длины группы данных, представляющему собой универсальную и производительную альтернативу известным методам.

Краткое описание чертежей

Далее описывается вариант (варианты) осуществления изобретения с использованием в качестве примера ссылок на прилагающиеся чертежи. На чертежах показано:

на фиг. 1 - схема примера вычислительной среды, в состав которой могут входить и в которой могут использоваться один или более аспектов настоящего изобретения,

на фиг. 2А - схема другого примера вычислительной среды, в состав которой могут входить и в которой могут использоваться один или более аспектов настоящего изобретения,

на фиг. 2Б - более детальная схема запоминающего устройства из состава вычислительной среды, показанной на фиг. 2А, согласно варианту осуществления настоящего изобретения,

на фиг. 3 - схема варианта процедуры определения длины группы символьных данных согласно варианту осуществления настоящего изобретения,

на фиг. 4А - схема примера главного запоминающего устройства, из которого данные, длина которых подлежит определению, загружаются в векторный регистр, согласно варианту осуществления настоящего изобретения,

на фиг. 4Б - схема примера векторного регистра, в который загружены данные из главного запоминающего устройства, схема которого показана на фиг. 4А, согласно варианту осуществления настоящего изобретения,

на фиг. 4В - схема другого примера главного запоминающего устройства, из которого данные, длина которых подлежит определению, загружаются в векторный регистр, согласно варианту осуществления настоящего изобретения,

на фиг. 4Г и 4Д - схемы примеров векторных регистров, в которые загружены данные из главного запоминающего устройства, схема которого показана на фиг. 4В, согласно варианту осуществления настоящего изобретения,

на фиг. 5 - схема варианта формата команды векторного типа для загрузки до границы блока (от англ.: Vector Load to Block Boundary) согласно варианту осуществления настоящего изобретения,

на фиг. 6А - схема варианта процедуры, связанной с командой векторного типа для загрузки до границы блока, согласно варианту осуществления настоящего изобретения,

на фиг. 6Б - схема другого варианта процедуры, связанной с командой векторного типа для загрузки до границы блока, согласно варианту осуществления настоящего изобретения,

на фиг. 7 - схема варианта формата команды векторного типа для поиска неравнозначного элемента (от англ.: Vector Find Element Not Equal) согласно варианту осуществления настоящего изобретения,

на фиг. 8 - схема варианта процедуры, связанной с командой векторного типа для поиска неравнозначного элемента, согласно варианту осуществления настоящего изобретения,

на фиг. 9 - схема взаимодействия узлов обработки, реализующая процедуру, показанную на фиг. 8, согласно варианту осуществления настоящего изобретения,

на фиг. 10 - схема варианта формата команды расчета загрузки до границы блока (от англ.: Load Count to Block Boundary) согласно варианту осуществления настоящего изобретения,

на фиг. 11 - схема варианта процедуры, связанной с командой расчета загрузки до границы блока, согласно варианту осуществления настоящего изобретения,

на фиг. 12 - схема примера файла регистра согласно варианту осуществления настоящего изобретения,

на фиг. 13 - графическое представление варианта осуществления компьютерного программного продукта, содержащего один или более аспектов настоящего изобретения,

на фиг. 14 - схема варианта осуществления хост-компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 15 - схема другого варианта осуществления компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 16 - схема другого варианта осуществления компьютерной системы, содержащей вычислительную сеть, для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 17 - схема варианта осуществления различных узлов компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 18А - схема варианта осуществления исполнительного устройства из состава компьютерной системы, показанной на фиг. 17, для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 18Б - схема варианта осуществления устройства ветвления из состава компьютерной системы, показанной на фиг. 17, для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 18В - схема варианта осуществления устройства загрузки-хранения из состава компьютерной системы, показанной на фиг. 17, для внедрения и использования одного или более аспектов настоящего изобретения,

на фиг. 19 - схема варианта осуществления эмулируемой хост-компьютерной системы для внедрения и использования одного или более аспектов настоящего изобретения.

Подробное описание

Согласно варианту осуществления настоящего изобретения, предоставляется возможность эффективной обработки символьных данных, в том числе (но не ограничиваясь) буквенных символов на любом языке, чисел, образованных из цифр, знаков пунктуации и/или прочих символов. Указанные символьные данные могут являться строками данных или не являться строками данных. С символьными данными связаны стандарты, примерами которых, в том числе, являются: ASCII (от английского American Standard Code for Information Interchange - Американский стандартный код обмена информацией); Юникод (стандарт Международной организации по стандартизации представления символов всех национальных алфавитов), в том числе (но не ограничиваясь) UTF 8 (от английского Unicode Transformation Format - формат преобразования Юникода); UTF16 и т.д.

Согласно одному из вариантов осуществления, предоставляется способ определения длины группы символьных данных, содержащей в своем составе символ окончания (например, строки символьных данных, оканчивающейся нулевым символом), с использованием параллельной обработки, не приводящий к возникновению необоснованных программных исключений (ошибок). Группа символьных данных (в настоящей заявке также используется термин "символьные данные" или "символьные данные с символом окончания"), длина которой подлежит определению, в одном из вариантов осуществления загружается в один или более векторных регистров. В частности, согласно варианту осуществления применяется команда [например, команда векторного типа для загрузки до границы блока (от англ.: Vector Load to Block Boundary)], которая в параллельном режиме загружает данные в векторный регистр до выбранной границы (такой как граница кэш-памяти или граница страницы) и позволяет определить число загруженных символов (значение переменной-счетчика). Например, для того, чтобы определить число загруженных символов, используется другая команда [например, команда расчета загрузки до границы блока (от англ.: Load Count to Block Boundary)]. Затем применяется команда [например, команда векторного типа для поиска неравнозначного элемента (от англ.: Vector Find Element Not Equal)] для поиска в загруженных данных символа-разделителя в пределах группы символьных данных, т.е. первого символа окончания, такого как равный нулю или пустой символ (символ конца строки). Эта команда проверяет совокупность байтов в параллельном режиме.

Если символ-разделитель не выявлен командой векторного типа для поиска неравнозначного элемента, то загружаются дополнительные данные из группы символьных данных, и повторяется расчет значения переменной-счетчика и поиск символа-разделителя. Переменная-счетчик содержит аккумулируемое значение, отслеживающее число загруженных байтов (могут использоваться другие единицы измерения) группы символьных данных. Загрузка, расчет и поиск символа-разделителя производятся до тех пор, пока не будет выявлен символ-разделитель. С помощью указанных команд длина символьных данных определяется с использованием только одной команды ветвления. Кроме того, проверка символьных данных производится быстро, в параллельном режиме, что предотвращает возникновение ложных программных исключений (ошибок).

Согласно настоящей заявке, длина элемента векторного регистра (также используется термин "вектор") составляет, например, один, два или четыре байта; векторным операндом является, например, операнд типа SIMD (от английского Single Instruction, Multiple Data - одиночный поток команд, множественный поток данных), состоящий из множества элементов. Согласно другим вариантам осуществления, длина элементов может быть иной, и векторный операнд необязательно имеет тип SIMD и/или может содержать один элемент.

Схема одного из вариантов осуществления вычислительной среды для внедрения и использования одного или более вариантов настоящего изобретения показана на фиг. 1. Вычислительная среда 100 содержит, например, процессор 102 [например, центральное процессорное устройство (ЦПУ)], запоминающее устройство 104 (например, главное запоминающее устройство) и одно или более устройств ввода-вывода и/или один или более интерфейсов 106, соединенных с другой вычислительной средой, например, через одну или более шин 108 и/или с помощью иных соединений.

Согласно варианту осуществления процессор 102 основан на архитектуре z/Architecture (торговая марка, обозначающая архитектуру линейки мейнфреймов), предложенной корпорацией International Business Machines Corporation (корпорацией IBM) и являющейся частью сервера, такого как сервер System z (торговая марка, обозначающая линейку мейнфреймов), который также предлагается корпорацией International Business Machines Corporation и в котором реализована архитектура z/Architecture. Один из вариантов осуществления архитектуры z/Architecture описан в публикации IBM "z/Architecture Principles of Operation" (от англ.: "Принцип действия архитектуры z/Architecture", публикация IBM № SA22-7832-08, 9-е издание, август 2010 г.). Согласно одному из вариантов осуществления, процессор выполняет команды операционной системы, такой как z/OS, также предлагаемой корпорацией IBM. IBM®, Z/ARCHITECTURE® и Z/OS® являются зарегистрированными торговыми марками корпорации International Business Machines Corporation, Армонк, штат Нью-Йорк, США. Прочие наименования, используемые в настоящей заявке, могут также быть зарегистрированными торговыми марками, торговыми марками или наименованиями продуктов корпорации International Business Machines Corporation или других компаний.

Согласно другому варианту осуществления, процессор 102 основан на архитектуре POWER Architecture (от английского Performance Optimization With Enhanced RISC - оптимизация производительности с применением улучшенной архитектуры RISC), предложенной корпорацией IBM. Одна из реализаций архитектуры POWER Architecture описана в публикации корпорации IBM "Power ISA™ Version 2.06 Revision В" от 23 июля 2010 г.POWER ARCHITECTURE® является зарегистрированной торговой маркой корпорации International Business Machines Corporation.

Согласно другому варианту осуществления, процессор 102 основан на архитектуре Intel, предложенной корпорацией Intel. Одна из реализаций архитектуры Intel описана в публикациях "Intel® 64 and IA-32 Architectures Developerʹs Manual: Vol. 2B, Команды Set Reference, A-L", номер заказа 253666-041US, декабрь 2011 г., и "Intel® 64 and IA-32 Architectures Developerʹs Manual: Vol. 2B, Команды Set Reference, M-Z", номер заказа 253667-041US, декабрь 2011 г.. Intel® является зарегистрированной торговой маркой корпорации Intel Corporation, г. Санта-Клара, штат Калифорния, США.

Согласно другому варианту осуществления, схема компьютерного окружения для внедрения и использования одного или более аспектов настоящего изобретения показана на фиг. 2А. В данном примере компьютерное окружение 200 содержит, например, собственное ЦПУ 202, запоминающее устройство 204 и одно или более устройств ввода-вывода и/или интерфейсов 206, соединенных между собой, например, через одну или более шин 208 и/или соединений другого типа. Например, компьютерное окружение 200 может содержать: процессор PowerPC, сервер pSeries или сервер xSeries, предложенные корпорацией International Business Machines Corporation, Армонк, штат Нью-Йорк, США; сервер HP Superdome с процессорами Intel Itanium II, предложенный корпорацией Hewlett Packard Corporation, г. Пало-Альто, штат Калифорния, США; и/или другие электронно-вычислительные машины, основанные на архитектурах, предложенных корпорациями International Business Machines Corporation, Hewlett Packard, Intel, Oracle или другими компаниями и корпорациями.

Собственное ЦПУ 202 содержит один или более собственных регистров 210, таких как один или более регистров общего назначения и/или один или более регистров специального назначения, используемых при выполнении вычислений в компьютерном окружении. Перечисленные регистры содержат информацию, которая отражает состояние компьютерного окружения в каждый отдельно взятый момент времени.

Кроме того, собственное ЦПУ 202 выполняет команды и программный код, которые хранятся в запоминающем устройстве 204. Согласно одному из примеров, ЦПУ выполняет код 212 эмулятора, хранящийся в запоминающем устройстве 204. Этот код позволяет компьютерному окружению, сконфигурированному по одной архитектуре, эмулировать (т.е. имитировать) другую архитектуру. Например, код 212 эмулятора позволяет электронным вычислительным машинам, основанным на архитектурах, отличных от z/Architecture, таким как процессоры PowerPC, серверы pSeries, серверы xSeries, серверы HP Superdome или другим, имитировать архитектуру z/Architecture и выполнять программное обеспечение и команды, разработанные для архитектуры z/Architecture.

Использование кода 212 эмулятора показано более подробно на схеме фиг. 2Б. Гостевые команды 250 содержат команды программного обеспечения (например, машинные команды), которые были разработаны для выполнения на архитектуре, отличной от архитектуры собственного ЦПУ 202. Например, гостевые команды 250 могли были быть разработаны для исполнения на процессоре 102, построенном по архитектуре z/Architecture, однако вместо этого эмулируются на собственном ЦПУ 202, которое может быть, например, процессором типа Intel Itanium II. В одном из примеров код 212 эмулятора содержит устройство 252 выборки команд, предназначенное для получения одной или более гостевых команд 250 из запоминающего устройства 204 и, возможно, для выполнения локальной буферизации (временного хранения) полученных команд. Этот код 212 эмулятора также содержит процедуру 254 трансляции команд, предназначенную для определения типа поступившей гостевой команды и трансляции указанной гостевой команды в одну или более соответствующих собственных команд 256 (т.е. команд, предназначенных для исполнения собственным ЦПУ, построенным по собственной архитектуре). В состав процедуры трансляции входят, например, идентификация функции, которая должна выполняться гостевой командой, и выбор собственной команды или набора команд для выполнения этой функции.

Кроме того, эмулятор 212 содержит процедуру 260 управления эмуляцией, обеспечивающую исполнение собственных команд. Процедура 260 управления эмуляцией может заставить собственное ЦПУ 202 выполнять программу из собственных команд, которая имитирует одну или более раннее поступивших гостевых команд, и по окончании этого вычислительного процесса возвращать управление упомянутой процедуре выборки команд для имитации получения следующей гостевой команды или группы гостевых команд. Процесс выполнения собственных команд 256 может содержать загрузку данных в регистр из запоминающего устройства 204, передачу данных из регистра обратно в запоминающее устройство для хранения или выполнение некоторой арифметической или логической операции в соответствии с указаниями процедуры трансляции.

Каждая процедура реализована, например, в программном обеспечении, которое хранится в запоминающем устройстве и выполняется собственным ЦПУ 202. В других примерах одна или более процедур или операций реализованы в постоянном запоминающем устройстве (ПЗУ), в аппаратном или программном обеспечении или в их комбинации. Упомянутые регистры эмулируемого процессора могут имитироваться с использованием регистров 210 собственного ЦПУ или с использованием пространства памяти запоминающего устройства 204. Согласно вариантам осуществления, гостевые команды 250, собственные команды 256 и код 212 эмулятора могут располагаться в одном и том же запоминающем устройстве или могут храниться распределенно (т.е. в различных запоминающих устройствах).

В рассматриваемом примере ПЗУ хранит, например, микрокод, милликод и/или макрокод процессора. Код содержит, например, команды аппаратного уровня и/или структуры данных, используемые при реализации машинных кодов более высокого уровня. В одном из вариантов осуществления код содержит, например, проприетарный код, который обычно является микрокодом и содержит выверенное программное обеспечение или микрокод, специфический для окружающего аппаратного обеспечения и контролирующий доступ операционной системы к аппаратному обеспечению вычислительной системы.

В одном из примеров загружаемая, транслируемая и исполняемая гостевая команда 250 является одной из описанных в настоящей заявке команд. Такая команда, предназначенная для одной архитектуры (например, для архитектуры z/Architecture), извлекается из запоминающего устройства, транслируется и представляется набором собственных команд 256 другой архитектуры (например, архитектуры PowerPC, pSeries, xSeries, Intel и т.д.). Затем указанные собственные команды исполняются.

Согласно варианту осуществления описанные команды являются командами векторного типа и являются частью векторного функционала (т.е. векторной среды, набора команд векторного типа и средств их обработки), предоставляемого согласно аспекту настоящего изобретения. Векторный функционал позволяет работать, например, с векторами фиксированной длины в пределах от одного до шестнадцати элементов. Каждый вектор содержит данные, которые обрабатываются векторными командами, определенными в векторном функционале. Согласно варианту осуществления, если вектор образован из набора элементов, то каждый элемент обрабатывается параллельно с другими элементами. Выполнение команды не завершено, пока не завершена обработка всех элементов.

Согласно настоящей заявке, векторные команды могут применяться в составе различных архитектур, в том числе (но не ограничиваясь) z/Architecture, Power, Intel и т.д. Несмотря на то, что описываемый в настоящей заявке вариант осуществления ориентирован на архитектуру z/Architecture, векторные команды и один или более аспектов настоящего изобретения могут базироваться и предназначаться для многих других типов архитектур. Архитектура z/Architecture используется исключительно в качестве одного из примеров.

Согласно варианту осуществления, по которому векторный функционал реализован как часть архитектуры z/Architecture, для того, чтобы использовать векторные регистры и команды, в специализированном управляющем регистре (например, управляющем регистре 0) флаги разрешения векторного функционала и векторных регистров должны быть установлены в состояние, например, логической единицы. Если векторный функционал инсталлирован, и векторная команда выполняется без разрешающих флагов, то возникает программное исключение (ошибка) данных. Если же векторный функционал не инсталлирован, и делается попытка выполнить векторную команду, то возникает программное исключение (ошибка) исполнения.

Векторные данные располагаются в запоминающем устройстве, например, в той же самой последовательности, слева направо, как и прочие форматы данных. Разряды формата данных с номерами от 0 до 7 образуют байт в крайней левой (с наименьшим номером) ячейке хранения байтов пространства памяти; разряды с номерами от 8 до 15 образуют байт в следующей за предыдущей ячейке памяти и т.д. В другом примере векторные данные могут располагаться в пространстве памяти запоминающего устройства в иной последовательности, например, справа налево.

Многие векторные команды, поддерживаемые векторным функционалом, снабжены полем, состоящим из специальных разрядов. Такое поле, называемое полем RXB (от английского register extension bit - бит расширения регистра), содержит наиболее значимый разряд для обозначений (т.е. для адресов) векторных регистров операндов. Разряды обозначений векторных регистров операндов, не оговоренные спецификацией команды, являются зарезервированными и должны быть установлены в состояние логического нуля.

Согласно варианту осуществления поле RXB состоит из четырех разрядов (например, с номерами от 0 до 3), и значения этих разрядов имеют следующее назначение:

разряд 0 - наиболее значимый разряд обозначения векторного регистра первого операнда;

разряд 1 - наиболее значимый разряд обозначения векторного регистра второго операнда, если такой операнд и соответствующий регистр предусмотрены командой;

разряд 2 - наиболее значимый разряд обозначения векторного регистра третьего операнда, если такой операнд и соответствующий регистр предусмотрены командой;

разряд 3 - наиболее значимый разряд обозначения векторного регистра четвертого операнда, если такой операнд и соответствующий регистр предусмотрены командой.

Каждый разряд устанавливается в состояние логического нуля или логической единицы, например, ассемблером, в зависимости от номера регистра. Например, в регистрах с номерами от 0 до 15 разряд устанавливается в состояние логического нуля, в регистрах с номерами от 16 до 31 разряд устанавливается в состояние логической единицы и т.д.

Согласно варианту осуществления каждый разряд поля RXB является разрядом расширения определенного поля в составе команды, указывающего на один или более векторных регистров. Например, в одной или более векторных командах разряд с номером 0 поля RXB служит разрядом-расширением части команды с номерами позиций от 8 до 11, эта часть команды обозначается, например, как V1; разряд с номером 1 поля RXB служит разрядом-расширением части команды с номерами позиций от 12 до 15, эта часть команды обозначается, например, как V2, и т.д.

Согласно другому варианту осуществления, поле RXB содержит дополнительные разряды, и для указания на каждый вектор или регистр в качестве разрядов-расширений используются по два и более разрядов.

В настоящей заявке изложено, что согласно аспекту настоящего изобретения для определения длины группы символьных данных, содержащей символ окончания, например строки данных, оканчивающейся пустым символом, используют различные команды. Далее подробно изложена процедура обработки, связанная с определением длины, а также применяемые для этого различные команды.

Согласно варианту осуществления, как показано на фиг. 3, для определения длины символьных данных, таких как символьная строка, оканчивающаяся пустым символом, символьные данные на шаге 300 загружаются в векторный регистр. Для этого используется, например, команда векторного типа для загрузки до границы блока. Указанная команда загружает до 16 байтов данных в параллельном режиме из главного запоминающего устройства без пересечения определенной границы пространства памяти главного запоминающего устройства. Подробные сведения об этой команде приводятся далее.

Затем на шаге 302 с использованием, например, команды расчета загрузки до границы блока, описанной далее, определяется число загруженных байтов.

Затем на шаге 304 в регистре с загруженными символьными данными выполняется поиск окончания (например, равного нулю символа или пустого символа или иного символа окончания). В одном из примеров для поиска символа окончания (например, равного нулю символа или пустого символа или иного символа, который обозначает окончание) используется команда векторного типа для поиска неравнозначного элемента, описанная далее. В одном из примеров эта команда выполняет поиск в содержимом регистра равных нулю элементов, которые также называют пустыми элементами (например, все разряды элемента имеют значение ноль). Равный нулю или пустой элемент обозначает окончание символьных данных, например, окончание определенной строки данных. Результатом поиска является значение индекса (порядкового номера, позиции), например, индекса байта первого по счету равного нулю элемента, называемого в настоящей заявке символом окончания, или же (если символ окончания не выявлен) заранее определенное значение, например, длина вектора, в котором велся поиск.

Затем на шаге 306 принимается решение, не превышает ли число загруженных символов (например, определенное командой расчета загрузки до границы блока) значение индекса символа окончания (например, определенного командой векторного типа для поиска неравнозначного элемента). Если не превышает, то на шаге 308 переменной Length (от англ.: длина) присваивается текущее значение Length, увеличенное на число загруженных символов, и выполнение процедуры продолжается с шага 300. В противном случае на шаге 310 значение переменной Length устанавливается равным текущему значению Length, увеличенному на значение индекса символа окончания, и процедура определения длины завершается.

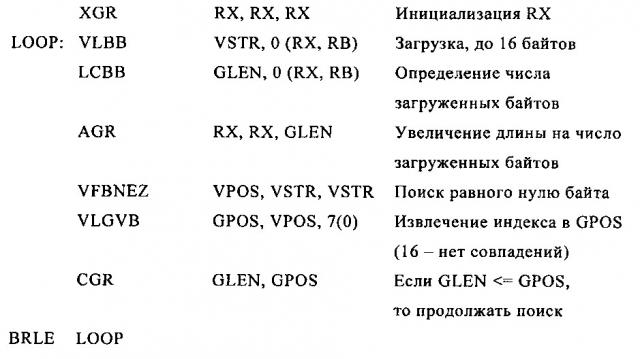

Ниже приведен пример псевдокода, используемого для определения длины строки с символом-окончанием, например, символьной строки, оканчивающейся равным нулю символом. Через RB обозначена строка символов (@), значение ее длины будет помещено в регистр RX

Согласно приведенному примеру псевдокода, вначале инициализируется регистр RX, который используется для хранения значения длины строки данных. Инициализация осуществляется, например, выполнением операции сложения по модулю 2 (XOR), операнды которой - RX и RX, причем результат возвращается в RX. В результате инициализации содержимое регистра RX обнуляется. Затем начинается цикл, в вектор VSTR загружаются 16 байтов данных. Далее определяется число байтов данных, загруженных в вектор VSTR, это число помещается в регистр GLEN общего назначения. Затем содержимое RX увеличивается на число загруженных байтов.

Затем выполняется поиск равного нулю символа (символа окончания), результат помещается в вектор VPOS. Этот результат либо является индексом равного нулю символа, либо (если равного нулю символа не выявлено) длиной вектора, например, равной шестнадцати. Затем результат из вектора VPOS извлекается и помещается в регистр GPOS общего назначения. Значение в регистре GPOS сравнивается со значением GLEN. Если значение GLEN меньше или равно значению GPOS, то процедура возвращается назад к операции VLBB, после чего загружаются дополнительные данные. В противном случае выполняются завершающие операции SGR и AGR.

На фиг. 4А показана схема примера главного запоминающего устройства 400. Из этого устройства данные загружаются в векторный регистр, длина этих данных подлежит определению. Видно, что главное запоминающее устройство 400 содержит строку данных "Hello World!", которая начинается с ячейки памяти с адресом 0×6FF3. В ходе загрузки данных не должна пересекаться граница пространства памяти главного запоминающего устройства, показанная вертикальной штриховой линией 402. Указанные данные загружаются в векторный регистр 420, пример которого показан на фиг. 4Б.

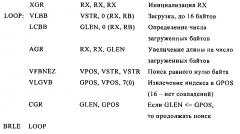

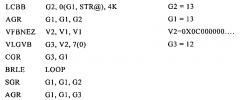

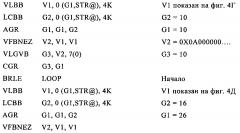

Один из примеров псевдокода для загрузки данных из главного запоминающего устройства, показанного на фиг. 4А (обозначенного в псевдокоде как STR@):

Другой пример главного запоминающего устройства 450 показан на фиг. 4В. Из этого устройства данные также загружаются в векторный регистр, длина этих данных также подлежит определению. Видно, что главное запоминающее устройство 450 содержит символьные данные "Hello World!", начало которых располагается в ячейке памяти с адресом 0×6FF6. Граница пространства памяти запоминающего устройства, которая не должна быть пересечена в ходе загрузки данных, показана вертикальной штриховой линией 452. Граница располагается до окончания символьных данных. Таким образом, в векторный регистр 470, пример которого показан на фиг. 4Г, сперва загружаются символьные данные вплоть до границы, а затем оставшаяся часть символьных данных загружается в векторный регистр 490, как показано на фиг. 4Д.

Один из примеров псевдокода для загрузки данных из главного запоминающего устройства, показанного на фиг. 4В (обозначенного в псевдокоде как STR@):

В соответствии с вышеизложенным, в одном из вариантов осуществления используются различные команды для определения длины символьных данных с символом окончания, таких как символьная строка, завершающаяся нулевым символом. Примеры указанных команд подробно описываются далее.

Одна из команд, используемая для загрузки в регистр - команда векторного типа для загрузки до границы блока (мнемонический код команды - VLBB), пример этой команды описывается с помощью схемы на фиг. 5. В одном из примеров команда 500 векторного типа для загрузки до границы блока содержит: поля 502а (например, разряды 0-7) и 502b (например, разряды 40-47) кода операции, идентифицирующие команду векторного типа для загрузки до границы блока; поле 504 векторного регистра (например, разряды 8-11) служащее для указания векторного регистра (V1); поле 506 индекса (Х2) (например, разряды 12-15); поле 508 базы (В2) (например, разряды 16-19); поле 510 смещения (D2) (например, разряды 20-31); поле 512 маски (М3) (например, разряды 32-35); поле 514 RXB (например, разряды 36-39). В одном из примеров каждое из полей 504-514 является отдельным и независимым от поля (полей) кода операции. Кроме того, в одном из вариантов осуществления указанные поля являются отдельными и независимыми одно от другого, однако согласно другим вариантам осуществления, два и более полей могут объединяться. Дальнейшие сведения об использовании перечисленных полей приводятся ниже.

В одном из примеров выбранные разряды (например, первые два разряда) кода операции, входящие в состав поля 502а кода операции, указывают длину и формат команды. В данном конкретном примере длина составляет три полуслова, и формат команды - векторный регистр-и-индекс-сохранение, с расширенным полем кода операции. Поле вектора (обозначение V) совместно с соответствующим разрядом поля RXB указывает на векторный регистр. В частности, для векторных регистров, регистр, содержащий операнд, указывается с использованием, например, четырехразрядного поля регистра и дополнительного разряда из поля расширения (RXB), этот разряд является наиболее значимым разрядом. Например, если значение в четырехразрядном поле - 0110, а значение разряда-расширения - 0, то их пятиразрядная комбинация дает число 00110, указывающее на регистр с номером 6 в десятичной системе счисления.

Нижний индекс в обозначении поля команды соответствует номеру операнда, к которому это поле относится. Например, нижний индекс 1 в обозначении V1 поля означает, что это поле относится к первому операнду и т.д. Длина операнда регистра совпадает с длиной самого регистра, которая составляет, например, 128 разрядов.

В одном из примеров в команде типа векторный регистр-и-индекс-сохранение для образования адреса второго операнда содержимое регистров общего назначения, указываемых полями Х2 и В2, объединяется с содержимым поля D2. В одном из примеров смещение D2 для команды векторного типа для загрузки до границы блока обрабатывается как 12-разрядное беззнаковое целое число.

В одном из вариантов осуществления поле М3 содержит код, который используется для информирования ЦПУ о границе (т.е. размере) загружаемого блока. Если указано зарезервированное значение, то возникает программное исключение (ошибка) спецификации. Примеры кодов и соответствующие значения границы:

При выполнении одного из вариантов осуществления команды векторного типа для загрузки до границы блока в направлении слева направо байты из второго операнда загружаются в первый операнд (он располагается в регистре, на который указывает поле V1 совместно с разрядом поля расширения). Загрузка ведется начиная с элемента, содержащего байт с индексом ноль. Второй операнд располагается в области запоминающего устройства, определяемой адресом второго операнда (также используется термин начальный адрес). Загрузка начинается с этой ячейки памяти и продолжается до конечного адреса, вычисляемого командой (либо процессором), как будет описано далее. Если при загрузке возникает граничное условие, то дальнейшие действия с оставшейся частью первого операнда зависят от используемой модели. Есл