Способ цикловой синхронизации с динамической адресацией получателя

Иллюстрации

Показать всеИзобретение относится к системам телекоммуникаций и вычислительной технике и может найти применение в устройствах приема информации из канала передачи или воспроизведения информации с высоким уровнем ошибок. Технический результат изобретения заключается в снижении времени адресации и синхронизации адреса получателя путем осуществления одновременной синхронизации и адресации. Технический результат достигается за счет способа цикловой синхронизации с динамической адресацией получателя, при котором на передающей стороне формируют превдослучайную кодовую последовательность максимальной длины, задавая закон формирования и начальную фазу этой последовательности, при этом на передающей стороне псевдослучайную кодовую последовательность формируют из двух последовательных участков таким образом, что начальная фаза первого участка соответствует первой половине адреса получателя, а фаза второго участка скачкообразно сдвинута на величину, соответствующую второй половине адреса получателя, а на приемной стороне формируют адресную последовательность путем поиска начальной фазы псевдослучайной последовательности максимальной длины по «зачетному участку» методом двойственного базиса. 1 з.п. ф-лы, 5 ил.

Реферат

Изобретение относится к системам телекоммуникаций и вычислительной технике и может найти применение в устройствах приема информации из канала передачи или воспроизведения информации с высоким уровнем ошибок.

В настоящее время на практике применяются методы цикловой синхронизации (фазирования), в которых в качестве синхронизирующих (фазирующих) комбинаций применяются псевдослучайные последовательности максимального периода (М-последовательности), для определения которых, как правило, используется выделение по зачетному участку.

Известно устройство синхронизации псевдослучайной последовательности с функцией исправления ошибок [см. 1. Патент на изобретение РФ №2486682, МПК H04L 7/02, H04W 8/20, опубл. 27.06.2013], которое реализует метод синхронизации псевдослучайной последовательности максимального периода по сравнению с принятой из канала связи ПСП с местной ПСП, сформированной на основе принятой из канала связи ПСП. Устройство содержит первую одноканальную линию задержки (ОЛЗ) на один бит, управляемый инвертор, первый ключ, линейный рекуррентный регистр (ЛРР), блок сравнения, вторую ОЛЗ на один бит, второй ключ, дешифратор, детектор качества канала связи, блок сложения, счетчик ошибок, счетчик нулей на с совпадений, третий ключ, инвертор «1», счетчик нулей на (m-c) совпадений, запоминающее устройство выбора количества исправляемых ошибок. К выходу из канала связи подключены последовательно подключенные первая ОЛЗ, управляемый инвертор, первый ключ, ЛРР с обратными связями, блок сравнения, а также последовательно включенные вторая ОЛЗ на один бит и второй ключ, выход ключа и вход второй ОЛЗ на один бит соединены соответственно с входом и выходом ЛРР с обратными связями, другой выход ЛРР с обратными связями подключен к входу дешифратора, при этом на вход первой ОЛЗ на один бит, на другой вход блока сравнения и детектор качества канала связи подан входной сигнал, причем выход детектора качества канала связи подключен к входу блока сложения, выходы которого соответственно подключены к информационному входу счетчика ошибок, входу счетчика «0» на с совпадений, информационному входу третьего ключа и входу инвертора «1». Управляющий вход счетчика ошибок подключен к выходу счетчика «0» на с совпадений, а выход соединен с входами сброса счетчиков нулей на с и (m-c) совпадений. Выход счетчика «0» на с совпадений подключен к входу сброса счетчика ошибок, входу включения инвертора «1» и управляющему входу третьего ключа. Выход третьего ключа подключен к управляющему входу управляемого инвертора. Информационный вход счетчика «0» на (m-c) совпадений подключен к инвертору «1», а выход соединен с управляющими входами первого ключа и второго ключа. Выход устройства выбора количества исправляемых ошибок подключен к управляющему входу счетчика ошибок.

Способ синхронизации, реализуемый в данном устройстве, заключается в следующем. Формирование местной ПСП на основе принятой осуществляется при помощи пропускания ПСП из канала связи через первый ключ в ЛРР с обратными связями, где формируется местная ПСП, которая затем поступает в блок сравнения. Одновременно на другой вход блока сравнения поступает ПСП из канала связи. В блоке сравнения происходит сравнение принимаемой и местной ПСП и при их совпадении выдаются нули на блок сложения, где производится операция логического сложения результатов предыдущего сравнения с сигналами от детектора качества канала связи. Если сигналы детектора качества канала связи отсутствуют, нули от блока сравнения через блок сложения поступают на счетчик «0» на с совпадений и после с совпадений в блоке сравнения сигнал счетчика «0» на с совпадений обнуляет счетчик ошибок, включает в работу инвертор «1» и замыкает третий ключ, после чего происходит заполнение счетчика «0» на (m-c) совпадений. Когда счетчик заполнится, он подает управляющий сигнал на первый и второй ключи, которые соответственно отключают ЛРР с обратными связями от канала и переводят формирование местной ПСП в автономный режим. Переход в режим автономного формирования местной ПСП влечет за собой выполнение операции выделения сигнала фазового пуска в дешифраторе, на который ПСП поступает параллельным кодом из ЛРР с обратными связями. При этом выделение сигналов фазового пуска на приеме и передаче происходит синхронно. Таким образом, с совпадений в блоке сравнения означает условное безыскаженное заполнение ЛРР с обратными связями, контролируемое детектором качества канала связи, а при заполнении счетчика «0» на (m-c) совпадений безусловную синхронизацию ЛРР с обратными связями. Если на входы блока сложения поступают сигналы «1» с детектора качества канала связи и блока сравнения, то ошибка фиксируется счетчиком ошибок, а сигнал «1» с блока сложения поступает на управляющий вход управляемого инвертора, который исправляет ошибку, находящуюся в этот момент во второй ОЛЗ на один бит.В инверторе «1» сигнал «1» преобразуется в «0» и подается на счетчик «0» на (m-c) совпадений, который обеспечивает после поступления (m-c) нулей выдачу сигнала на первый и второй ключи и переводит формирование местной ПСП в автономный режим. Если количество обнаруженных и исправленных ошибок, установленных в устройстве выбора количества исправляемых ошибок, превышает допустимый порог М, то счетчик ошибок формирует управляющий сигнал «Сброс» для счетчиков нулей на с совпадений и (m-c) совпадений и перехода ЛРР с обратными связями в автономный режим работы не происходит. Таким образом, операция формирования местной ПСП в автономном режиме выполняется в зависимости от сигналов, поступающих как от блока сравнения, так и от детектора качества канала связи, тем самым обеспечивается возможность выполнения этой операции при наличии ошибок на участке ЗОТ в принимаемой ПСП за счет их исправления при условии, что их количество не превышает заданного порогового значения М. Если на входы блока сложения с детектора качества канала связи и блока сравнения поступают сигналы противоположных значений, то это приводит к запрету работы устройства синхронизации ПСП и указывает на неисправность элементов устройства.

Реализуемый в данном устройстве способ используется только для синхронизации и не позволяет применять псевдослучайные последовательности максимального периода для адресации устройств.

Известны также способ динамической адресации корреспондентов мобильной радиосети и устройство для его реализации [см. 2. Патент на изобретение РФ №2557451, МПК H03D 7/00, Н04В 1/10, H04J 13/10, H04W 12/06, опубл. 20.07.2015 г. ], в котором организовано совмещение функций кодового разделения каналов, адресации, синхронизации, модуляции и демодуляции радиочастотного сигнала, а также аутентификации (адресации) абонентских устройств и кодирования речевой информации непосредственно в радиоканале (на физическом и канальном уровнях радиосети).

Данный способ заключается в том, что любой корреспондент на начальном этапе установления связи загружает генератор псевдослучайной кодовой последовательности своего приемника стартовым кодом, соответствующим его собственному номеру (адресу) или сформированным по определенному (известному всем абонентам) закону на основании этого собственного номера (адреса) и запускает процедуру самосинхронизации с корреспондентами, осуществляющими в данный момент его вызов, передатчики которых генерируют циклические кодовые последовательности ограниченной длины, формируемые на основе стартового кода, который соответствует номеру (адресу) данного вызываемого корреспондента, т.е. генерацию именно того кода, который в данный момент ожидает приемник вызываемого корреспондента. После завершения процедуры самосинхронизации вызывающего и вызываемого корреспондентов вызывающий корреспондент по образовавшемуся виртуальному радиоканалу получает возможность передать вызываемому корреспонденту свой собственный номер (адрес), а вызываемый корреспондент получает возможность сформировать и загрузить в генератор псевдослучайных последовательностей своего передатчика в качестве стартового адреса некий новый код, состоящий из (или сформированный на основе) кодов адресов вызывающего и вызываемого корреспондентов, после чего запустить генерацию циклических ограниченных псевдослучайных кодовых последовательностей, стартующих с этого кода, в то время, как вызывающий корреспондент, для которого этот код априори является известным, поскольку он формируется по вполне определенным правилам на основе известных вызывающему корреспонденту кодов (адресов), запускает стартующий с этого кода процесс самосинхронизации своего приемника. По завершении процедуры самосинхронизации вызываемый корреспондент получает возможность передачи по образовавшемуся новому (обратному) виртуальному радиоканалу любых данных и команд (в т.ч. цифрового речевого потока) вызывающему корреспонденту. В дальнейшем для определенности регистры передатчика и приемника, в которых формируются и хранятся в процессе установления соединения стартовые адреса (коды), которыми загружаются и на основании которых генераторами псевдослучайных кодовых последовательностей формируются псевдослучайные кодовые последовательности, необходимые для формирования радиосигнала в передатчике и обработки его в приемнике, будем называть регистрами динамической адресации.

Основными частями устройства, реализующего описанный способ, являются подсистемы адресации и синхронизации. Результатом работы подсистем адресации и синхронизации является формирование соответствующих псевдослучайных кодовых последовательностей, необходимых для работы модулятора передатчика и демодулятора приемника в процессе установления соединения и осуществления передачи информации.

Для обеспечения синхронизации необходимо, чтобы передающий абонент многократно (циклически) передавал, а принимающий был готов к приему (обработке) одной и той же многократно (циклически) повторяющейся кодовой последовательности, т.е. стартовой псевдослучайной кодовой последовательности, формируемой передатчиком и обрабатываемой приемником при помощи идентичных генераторов (с одинаковыми законами формирования) с полностью идентичными параметрами (стартовыми адресами). В простейшем случае псевдослучайные кодовые последовательности могут быть сформированы при помощи сдвиговых регистров с линейными и нелинейными обратными связями. Перед началом работы сам закон формирования псевдослучайной кодовой последовательности определяется аппаратными методами (при помощи введения соответствующих обратных связей такого «регистра»), а «начальную фазу» генерируемой псевдослучайной кодовой последовательности можно задать (определить) той или иной конкретной стартовой кодовой комбинацией (стартовым адресом), загружаемым в регистры стартового адреса генераторов псевдослучайных кодовых последовательностей соответственно передатчика и приемника абонентского комплекта. Если стартовая комбинация и закон формирования псевдослучайных кодовых последовательностей у передающего и принимающего абонентов будут совпадать, основанная на принципе корреляционного сравнения сигналов система синхронизации, описанная ранее, в течение некоторого промежутка времени, называемого временем синхронизации, обеспечит вхождение абонента-приемника в связь с абонентом-передатчиком (будет образован виртуальный радиоканал), а следовательно, будет возможен последующий прием по этому виртуальному радиоканалу цифровой информации, на основе которой, в свою очередь, будут возможны прием кодов (адресов и команд) и последующее управление как самим абонентом-приемником, так и управление собственно процессом приемопередачи посредством этих специальных команд, передаваемых по образовавшемуся радиоканалу.

Таким образом, подсистема синхронизации абонентов должна обеспечить вхождение в связь тех абонентов, в регистры стартового адреса генераторов псевдослучайных кодовых последовательностей передатчика и приемника которых «загружен» один и тот же цифровой код. Подсистема адресации абонентов должна обеспечивать «загрузку» в нужные моменты времени требуемых кодов в регистры стартовых адресов циклических псевдослучайных кодовых последовательностей комплементарных - принимающего и передающего - абонентских устройств в процессе их вхождения в связь (синхронизации) и во время последующей процедуры установления соединения (каналообразования), передачи и обработки команд управления каналом (по прямому и обратному радиоканалам), а также во время передачи цифровой речевой информации.

Данный способ наиболее близок по технической сущности к заявляемому изобретению и выбран в качестве прототипа.

Однако в данном способе функции адресации и синхронизации разделены, что приводит к увеличению времени их реализации. Кроме того, в прототипе многие адресаты смогут определить конец общей для них фазирующей последовательности и начать анализ поступающего кадра, выделяя в специальном поле адрес получателя, который часто передается в открытом виде, что в определенной мере снижает уровень защиты (конфиденциальности получателя).

Техническим результатом изобретения является снижение времени адресации и синхронизации и повышение уровня защиты адреса получателя путем осуществления одновременной синхронизации и адресации.

Указанный технический результат достигается в способе цикловой синхронизации с динамической адресацией получателя, при котором на передающей стороне формируют превдослучайную кодовую последовательность максимальной длины, задавая закон формирования и начальную фазу этой последовательности, отличающемся тем, что на передающей стороне псевдослучайную кодовую последовательность формируют из двух последовательных участков таким образом, что начальная фаза первого участка соответствует первой половине адреса получателя, а фаза второго участка скачкообразно сдвинута на величину, соответствующую второй половине адреса получателя, а на приемной стороне формируют адресную последовательность путем поиска начальной фазы псевдослучайной последовательности максимальной длины по «зачетному участку» методом двойственного базиса.

При этом длина каждого из двух последовательных участков псевдослучайной кодовой последовательности может быть равна периоду М-последовательности.

Достижение указанного технического результата в предлагаемом способе обеспечивается следующим образом.

Так как в предлагаемом способе решение о запуске может принять только тот получатель, которому адресовано сообщение, это обеспечивает повышенную защищенность запуска приемника. При этом одновременно с выделением конца фазирующей составной последовательности будет определен и адрес получателя, что позволит именно этому получателю произвести дальнейший прием и обработку кадра и совместить процесс синхронизации и адресации. В прототипе же многие адресаты смогут определить конец общей для них фазирующей последовательности и начать анализ поступающего кадра, выделяя в специальном поле адрес получателя, который часто передается в открытом виде, что в определенной мере снижает уровень защиты (конфиденциальности получателя), а также увеличивает время синхронизации и адресации.

Дополнительным преимуществом является то, что выделение «зачетных участков» на приеме в отличие от прототипа осуществляется методом двойственного базиса [Когновицкий О.С. Двойственный базис и его применение в телекоммуникациях. Линк, СПб, 2009]. Это означает, что для идентификации фазы в предлагаемом способе необходимо выделить только к элементов, тогда как в прототипе для идентификации рекуррентной принимаемой последовательности необходимо выделять как минимум (k+1) элемент. Это обеспечивает в предлагаемом способе дополнительный вклад в уменьшение времени синхронизации и адресации.

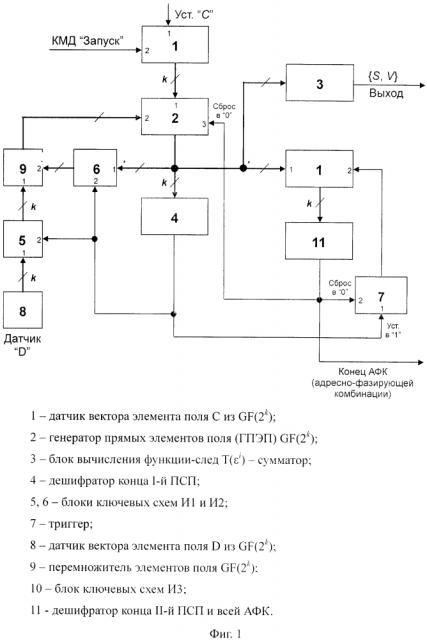

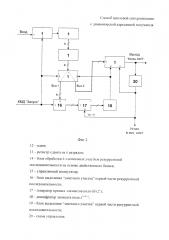

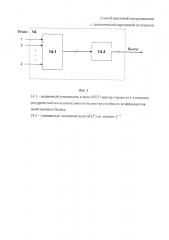

Предлагаемый способ поясняется чертежами, где на фиг. 1 и 2 приведены структурные схемы блоков передающей и приемной сторон устройства для реализации предлагаемого способа, на фиг. 3 приведена структура блока обработки k-элементных участков на основе двойственного базиса, на фиг. 4 приведена структура блока выделения «зачетного участка» первой части линейной рекуррентной последовательности адресно-фазирующей комбинации (АФК), на фиг. 5 - структура блока выделения «зачетного участка» второй части линейной рекуррентной последовательности АФК. Согласно фиг. 1 на передающей стороне имеются:

1 - датчик вектора элемента поля С из GF (2k);

2 - генератор прямых элементов поля (ГПЭП) GF(2k);

3 - блок вычисления функции-след Т(εi) - сумматор;

4 - дешифратор конца I-й ПСП;

5, 6 - блоки ключевых схем И1 и И2 соответственно;

7 - триггер;

8 - датчик вектора элемента поля D из GF(2k);

9 - перемножитель элементов поля GF(2k);

10 - блок ключевых схем И3;

11 - дешифратор конца II-й ПСП и всей АФК.

При этом на первый и второй входы датчика 1 вектора элемента поля С из GF(2k) подается сигнал установки элемента поля С и команда «Запуск» соответственно, а выход датчика 1 подключен к первому входу генератора 2 прямых элементов поля (ГПЭП) GF(2k), ко второму входу которого подключен выход перемножителя 9 элементов поля GF(2k), а к третьему входу генератора 2 подключены второй вход триггера 7 и выход дешифратора конца II-й ПСП и всей адресно-фазирующей комбинации (АФК), выход генератора 2 подключен к входам дешифратора 4 конца I-й ПСП, блока 6 ключевых схем И2, блока 10 ключевых схем И3 и блоку 3 вычисления функции - след Т(εi) (сумматору), выход которого является выходом передатчика, второй вход блока 6 ключевых схем И2 соединен со вторым входом блока 5 ключевых схем И1, выходом дешифратора 4 конца I-й ПСП и первым входом триггера 7, выход которого подключен ко второму входу блока ключевых схем И3, выход которого соединен с входом дешифратора 11 конца II-й ПСП и всей АФК, первый вход блока 5 ключевых схем И1 соединен с выходом датчика 8 вектора элемента поля D из GF(2k).

Согласно фиг. 2 на приемной стороне имеются:

12 - ключ;

13 - регистр сдвига на k разрядов;

14 - блок обработки k-элементных участков рекуррентной последовательности на основе двойственного базиса;

15 - управляемый коммутатор;

16 - блок выделения "зачетного участка" первой части рекуррентной последовательности;

17 - генератор прямых элементов поля GF(2k);

18 - дешифратор элемента поля εN-k+1;

19 - блок выделения "зачетного участка" второй части рекуррентной последовательности;

20 - схема управления.

При этом входом приемной части является первый вход ключа 12, на второй вход которого, а также на второй вход управляемого коммутатора 15 и первый вход блока 16 выделения «зачетного участка» первой части рекуррентной последовательности подан сигнал КМД «Запуск», выход ключа 12 соединен с входом регистра 13 сдвига на k разрядов, выход которого подключен к входу блока 14 обработки k-элементных участков рекуррентной последовательности на основе двойственного базиса, выход которого подключен к первому входу управляемого коммутатора 15, третий вход которого соединен со вторым входом блока 19 выделения "зачетного участка" первой части рекуррентной последовательности, и выходу дешифратора 18 элемента поля εN-k+1, третий вход блока 19 соединен со вторым входом установки «0» генератора 17 прямых элементов поля GF(2k) и с выходом схемы 20 управления, который является выходом установки в исходное состояние, первый вход генератора 17 соединен с выходом блока 16, второй вход которого соединен с первым выходом управляемого коммутатора 15, второй выход которого подключен к первому входу блока 19, выход которого, связанный с входом схемы 20 управления, является выходом «Конец АФК» приемной части.

Согласно фиг. 3 блок 14 обработки k-элементных участков рекуррентной последовательности на основе двойственного базиса содержит последовательно соединенные 14.1 - матричный умножитель в поле GF(2k) вектор-строки из k элементов рекуррентной последовательности на вектор-столбец из коэффициентов двойственного базиса и 14.2 - умножитель элементов поля GF(2k) на элемент С-1.

Согласно фиг. 4 блок 16 выделения «зачетного участка» первой части линейной рекуррентной последовательности АФК содержит:

16.1, 16.3 - устройства запоминания элементов поля GF(2k);

16.2 - умножитель на элемент поля ε ∈ GF(2k);

16.4 - компаратор;

16.5 - счетчик на L последовательных совпадений;

16.6 - ключевую схему.

При этом на вход устройства 16.1 запоминания элементов поля GF(2k) подан сигнал с первого выхода управляемого коммутатора 15, выход устройства 16.1 подключен к входу умножителя 16.2 на элемент поля ε ∈ GF(2k) и одному из входов компаратора 16.4, к другому входу которого подключены первый вход ключевой схемы 16.6 и выход устройства 16.3 запоминания элементов поля GF(2k), вход которого соединен с выходом умножителя 16.2, на первый выход компаратора 16.4 и первый вход счетчика 16.5 L-последовательных совпадений подан сигнал КМД «Запуск», а второй выход компаратора 16.4 соединен со вторым входом счетчика 16.5, выход которого подключен ко второму входу ключевой схемы 16.6, выход которой является выходом блока 16 выделения «зачетного участка» первой части линейной рекуррентной последовательности АФК.

Согласно фиг.5 блок 19 выделения «зачетного участка» второй части линейной рекуррентной последовательности АФК содержит:

19.1 - перемножитель элементов поля GF(2k);

19.2 - генератор обратных элементов поля GF(2k);

19.3 - дешифратор элемента поля D (второй половины адреса получателя);

19.4 - счетчик числа последовательных элементов D емкостью L;

19.5 - дешифратор элемента поля ε-(N-k);

19.6 - ключ.

При этом на вход 1 перемножителя элементов поля 19.1 через ключевую схему 15 поступают k-элементные комбинации в виде элементов поля GF(2k) с выхода блока 14 обработки k-элементных участков рекуррентной последовательности на основе двойственного базиса, а на вход 2 перемножителя 19.1 и на вход дешифратора 19.5 элемента поля ε-(N-k) поступают элементы с выхода генератора обратных элементов 19.2, в который при его запуске была установлена «1» сигналом с выхода дешифратора 18 элемента поля εN-k+1. Выход перемножителя 19.1 соединен с входом дешифратора 19.3 элемента поля D (второй половины адреса получателя), первый выход которого подключен к первому входу счетчика 19.4 числа последовательных элементов D емкостью L, второй выход дешифратора 19.3 подключен ко второму входу счетчика 19.4, выход которого подключен к первому входу ключа 19.6, второй вход которого соединен с выходом дешифратора 19.5, а выход ключа 19.6 является выходом сигнала «Конец АФК», при этом на второй вход генератора 19.2 подан сигнал Сброс в «0».

Предлагаемый способ осуществляется в данном устройстве следующим образом.

В передающей части (фиг. 1) для формирования и передачи адресно-фазирующей последовательности по команде «Запуск» производится запись из датчика 1 в генератор 2 начальной фазы первой части рекуррентной последовательности (М-последовательности) в виде элемента поля Галуа GF(2k), соответствующего первой половине адреса получателя С, и разрешается потактовая работа генератора 2 прямых элементов поля GF (2k) с начального элемента С, который принадлежит GF(2k), под управлением тактовых импульсов, поступающих из генератора тактовых импульсов (не показан на схемах). Поступление каждого тактового импульса последовательности формирует в генераторе 2 элементы поля С, Сε, Сε2, …, где ε - первообразный элемент поля (корень характеристического многочлена Р(х) рекуррентной последовательности (М-последовательности). Формируемые на выходе генератора 2 элементы поля GF(2k) в виде k-элементных параллельных двоичных комбинаций поступают на блок 3 вычисления функции-след Т(Сεi), i=0, 1, 2, …, от элементов поля С, Сε, Сε2, … Результаты вычисления в виде последовательных двоичных элементов si=Т(Сεi), представляющих собой рекуррентную последовательность (М-последовательность), поступают на «Выход» блока передачи. Параллельно k-элементные комбинации с выхода генератора 2 поступают на дешифратор 4 конца первой части рекуррентной последовательности и на блоки 6 и 10 ключевых схем, которые открываются сигналом с выхода дешифратора 4. При этом на первые входы перемножителя 9 элементов поля GF(2k) через ключевые схемы 5 поступает k-элементная комбинация, соответствующая элементу поля GF(2k), представляющего собой вторую часть адреса D, а на вторые входы перемножителя 9 через ключевые схемы 6 с генератора 2 поступает элемент поля εi в виде параллельной k-элементной комбинации. Произведение этих элементов D⋅εi в виде параллельной k-элементной комбинации с выхода перемножителя 9 поступает на вторые (2) входы генератора 2, скачкообразно изменяя с этого момента фазу генерируемых элементов поля на величину D и, соответственно, смещая скачкообразно фазу формируемой на выходе блока 3 рекуррентной последовательности.

Таким образом, после срабатывания дешифратора 4 с выхода блока 3 начинается формирование второй части рекуррентной последовательности, смещенной по фазе относительно первой части рекуррентной последовательности на величину, соответствующую второй половине адреса получателя (С, D). Одновременно сигналом с выхода дешифратора 4 устанавливается в активное состояние (в «1») триггер 7, открывая по входу 2 блок ключевых схем 10 и пропуская тем самым k-элементные комбинации с выхода генератора 2 на вход дешифратора 11 конца второй части рекуррентной последовательности. Когда на выходе генератора 2 появится k-элементная комбинация, соответствующая концу второй части рекуррентной последовательности, сработает дешифратор 11, сигнал с выхода которого сбросит в нулевое состояние генератор 2 и триггер 7, а также будет выходным сигналом окончания адресно-фазирующей комбинации (АФК) и начала формирования остальных полей кадра канального уровня.

В приемной части (фиг. 2) по команде «Запуск» устанавливается в исходное состояние блок 16 выделения «зачетного участка» первой рекуррентной последовательности (М-последовательности) адресно-фазирующей комбинации (АФК), выход 1 коммутатора 15 соединяется с его входом 1 и замыкается ключ 12, подключая вход k-разрядного регистра 13 к каналу связи ("Вход"). Под действием тактовых импульсов, формируемых генератором тактовых импульсов (не показан на схеме блока приемника), содержимое ячеек регистра 13 с каждым тактом сдвигается вправо на один шаг и параллельно считывается на к выходных цепей ячеек регистра 13, поступая на к входных цепей блока 14 обработки k-элементных участков на основе двойственного базиса. При последовательном заполнении регистра сдвига 13 безошибочными k-элементными комбинациями блок 14 на основе двойственного базиса будет с каждым тактом формировать на своем выходе последовательно элементы поля 1, ε, ε2, ε3…, причем единичный элемент сформируется тогда, когда в ячейках регистра 13 будет находиться начальная k-элементная безошибочная комбинация первой части рекуррентной последовательности (s0, s1, …,sk-1), элемент ε - когда в ячейках регистра будет комбинация (s1, s2, …, sk) и т.д.

Сформированные таким образом элементы поля GF(2k) с выхода блока 14 через коммутатор 15 подаются на вход 2 блока 16 выделения безошибочного «зачетного участка» длиной m=k+L-1, где k - число ячеек регистра сдвига 13, L - емкость порогового счетчика в составе блока 16. При поступлении из канала связи m безошибочных двоичных элементов первой части рекуррентной последовательности, начиная, например, с элемента si, на выходе блока 14 появятся L последовательных элементов поля GF(2k) εi, εi+1, …, εi+L-1, вследствие чего пороговый счетчик на L в составе блока 16 сработает и обеспечит выдачу на выход блока 16 элемента поля εi+L-1, который запишется в генератор 17 прямых элементов поля GF(2k). Генератор 17 под действием тактовых импульсов начнет генерировать в автономном режиме последовательные элементы поля ε1+L-1, εi+L, εi+L+1, …, . Генерирование последовательных элементов поля будет продолжаться в автономном режиме до тех пор, пока в генераторе 17 не установится состояние εN-k+1. При этом сработает дешифратор 18, подключенный к выходу генератора 17 прямых элементов поля. Выходной сигнал дешифратора 18 поступает на вход 2 блока 19 выделения «зачетного участка» второй части рекуррентной последовательности, устанавливая «1» в ячейки генератора обратных элементов поля в составе блока 19 и параллельно на вход 3 коммутатора 15, соединяя тем самым вход 1 коммутатора 15 с его выходом 2. С этого момента под воздействием тактовых импульсов k-элементные комбинации в виде последовательных элементов поля GF(2k) с выхода блока 14 через коммутатор 15 поступают на вход 1 блока 19. В случае поступления на вход устройства безошибочных k-элементных участков второй части рекуррентной последовательности (vi, vi+1, …, vi+k-1), i=0, 1, 2…, в блоке 19 на основе двойственного базиса будет вычисляться элемент D, представляющий собой вторую половину адреса получателя (C, D). После выделения «зачетного участка», состоящего из L подряд выделенных элементов D, генератор 19.2 обратных элементов поля GF(2k) в составе блока 19 перейдет в автономный режим работы до тех пор, пока в генераторе обратных элементов поля не установится элемент ε-(N-k), где N - длина второй части рекуррентной последовательности. При этом на выходе блока 19 появится сигнал окончания адресно-фазирующей комбинации (АФК). Этот же сигнал параллельно поступит на вход схемы управления 20, которая сработает и ее выходной сигнал поступит на вход 2 генератора прямых элементов поля 17 и установит его в «0», одновременно этот же сигнал поступит на вход 3 блока 19 и сбросит в «0» генератор обратных элементов поля GF(2k) в составе блока 19. Тем самым блок приема будет приведен в исходное состояние.

В блоке 14 обработки k-элементных участков принимаемой рекуррентной последовательности (фиг. 3) на каждом такте работы приемной части устройства k-разрядная комбинация с выходов ячеек регистра сдвига 13 параллельным кодом поступает на вход матричного умножителя 14.1, в котором происходит умножение в расширенном поле GF(2k) вектор-строки [si, si+1, …, si+k-1] (или [vi, vi+1, …, vi+k-1]) на вектор-столбец из коэффициентов двойственного базиса

В результате перемножения на выходе блока 14.1 появится элемент поля в виде k-разрядного вектора, который поступит на вход блока 14.2 умножения поступившего элемента поля на постоянный множитель - коэффициент, представляющий собой элемент поля С-1, т.е. элемент поля, обратный элементу С. Результат перемножения поступит на выход блока 14 в виде k-разрядной комбинации элементов простого поля GF(2).

В блоке 16 выделения «зачетного участка» первой части рекуррентной последовательности (фиг. 4) с каждым тактом работы приемной части устройства k-разрядная комбинация, соответствующая определенному элементу εi поля GF (2k), с выхода блока 14 обработки k-элементных участков рекуррентной последовательности через коммутатор 15 поступает на вход устройства 16.1 запоминания k-элементной комбинации, которая далее поступает параллельно на вход умножителя 16.2 на элемент s поля GF(2k) и на вход 1 компаратора 16.4.

Результат умножения с выхода блока 16.2 в виде элемента εi+1 записывается в устройство запоминания 16.3. Со следующим тактом с устройства памяти 16.1 будет поступать элемент εi+1 на вход 1 компаратора 16.4, а на вход 2 компаратора 16.4 - элемент поля с выхода устройства памяти 16.3. Если значения элементов поля на входах 1 и 2 компаратора 16.4 совпадают, то на выходе 2 компаратора 16.4 появится сигнал +1, увеличивающий на единицу показания счетчика 16.5 на L последовательных совпадений. При несовпадении сравниваемых элементов появится сигнал на выходе 1 компаратора 16.4, который, как и команда «Запуск», установит счетчик 16.5 в состояние «1». Когда счетчик (пороговый элемент) 16.5 на L последовательных совпадений сработает, то на его выходе появится сигнал, который поступит на вход 2 ключевой схемы 16.6 и разрешит прохождение k-элементной комбинации в виде элемента поля εj на выход схемы 16.6, т.е. на выход блока 16.

В блоке 19 выделения «зачетного участка» второй части адресно-фазирующей рекуррентной последовательности (фиг.5) на вход 1 перемножителя элементов поля 19.1 через ключевую схему 15 поступают k-элементные комбинации в виде элементов поля GF(2k) с выхода блока 14 обработки k-элементных участков рекуррентной последовательности на основе двойственного базиса, а на вход 2 перемножителя 19.1 поступают элементы с выхода генератора обратных элементов 19.2, в который при его запуске была установлена «1» сигналом с выхода дешифратора 18 элемента поля ε-N-k+1. В случае безошибочного приема k-элементных участков второй части рекуррентной последовательности на выходе перемножителя 19.1 будет формироваться элемент D, соответствующий второй половине адреса получателя (C, D). Этот элемент D с выхода перемножителя 19.1 поступает на дешифратор 19.3 элемента D. В случае поступления на дешифратор 19.3 элемента D на его выходе 1 появится сигнал, поступающий на счетный вход 1 порогового счетчика 19.4, подсчитывающего L последовательных сигналов с выхода дешифратора 19.3.

При срабатывании дешифратора 19.3 L раз подряд счетчик 19.4 заполнится и выдаст на своем выходе постоянный сигнал, который будет удерживать ключ 19.6 в открытом состоянии до тех пор, пока не сработает дешифратор 19.5, настроенный на элемент поля ε-(N-k), поступающий на вход дешифратора 19.5 с выхода генератора обратных элементов поля 19.2. Сигнал с выхода дешифратора 19.5 поступает через открытый ключ 19.6 на выход устройства и будет являться сигналом «Конец адресно-фазирующей последовательности» и началом остальных полей кадра канального уровня.

Одновременно сигнал с выхода ключа 19.6 поступает на вход схемы 20 управления, которая сработает и сформирует управляющий сигнал на ее выходе, поступающий на вход 2 генератора 19.2 обратных элементов поля, устанавливая его в «0», и на вход 2 генератора 17 прямых элементов поля GF(2k), устанавливая его в «0».

Заметим, что в случае, когда на вход дешифратора 19.3 поступит элемент поля, отличный от D, а счетчик 19.4 еще не заполнился, то появится сигнал на выходе 2 дешифратора 19.3, который поступит на вход 2 счетчика 19.4 и обнулит его.

Элементы устройства для реализации предлагаемого способа могут быть выполнены либо на основе стандартных логических элементов (микросхемы К155, КР1554 и КР1561), либо на основе CPLD или FPGA ПЛИС (например, ПЛИС фирм Altera и Xilinx).

1. Способ цикловой синхронизации с динамической адресацией получателя, при котором на передающей стороне формируют превдослучайную кодовую последовательность максимальной длины, задавая закон формирования и начальную фазу этой последовательности, отличающийся тем, что на передающей стороне формируют псевдослучайную кодовую последовательность, состоящую из двух последовательных участков, таким образом, что начальная фаза первого участка соответствует первой половине адреса получателя, а фаза второго участка скачкообразно сдвинута на величину, соответствующую второй половине адреса получателя, а на приемной стороне формируют адресную последовательность путем поиска начальной фазы псевдослучайной последовательности максимальной длины по «зачетному участку» методом двойственного базиса.

2. Способ по п. 1, отличающийся тем, что длина каждого из двух последовательных участков псевдослучайной кодовой последовательности равна периоду М-последовательности.