Мультидифференциальный операционный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления сигналов. Технический результат - уменьшение напряжения смещения нуля, повышение стабильности при низких температурах и воздействии радиации. Мультидифференциальный операционный усилитель содержит первый входной биполярный транзистор, первый входной полевой транзистор с управляющим р-n переходом, первое токовое зеркало, источник питания, второй входной биполярный транзистор, второй входной полевой транзистор с управляющим р-n переходом, второе токовое зеркало, первое дополнительное токовое зеркало, второе дополнительное токовое зеркало. 10 ил.

Реферат

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления широкополосных сигналов.

В современной микроэлектронике находят применение так называемые мультидифференциальные операционные усилители (МОУ), обладающие (в сравнении с классическими ОУ) рядом неоспоримых преимуществ по схемам включения и их параметрам [1-17]. Сегодня МОУ реализуются на биполярных [1, 2] и полевых транзисторах [3-12], а также в виде гибридных схемотехнических решений, содержащих биполярные и полевые транзисторы с управляющим р-n переходом [13-16]. Последний подкласс МОУ при его реализации на основе технологии ОАО «Интеграл» (г. Минск) [17] отличается высокой радиационной стойкостью и, в этой связи, относится к достаточно перспективной элементной базе.

Однако для таких МОУ необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [17], которая обеспечивает радиационную стойкость микроэлектронных изделий до 1 Мрад и выдерживает поток нейтронов до 1013 н/см2.

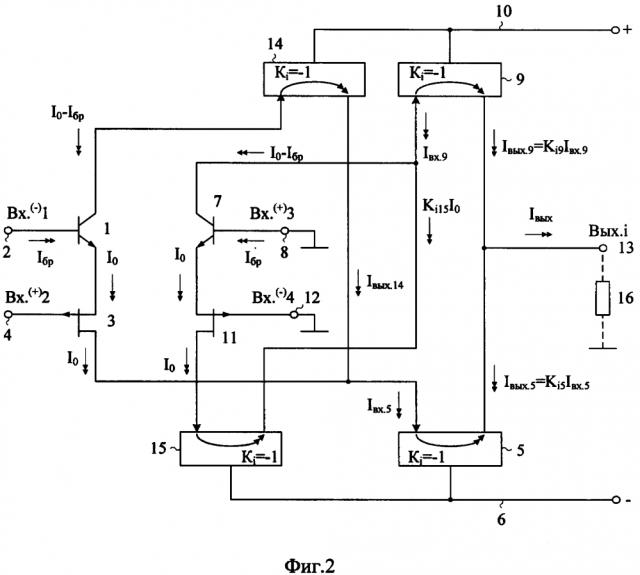

Ближайшим прототипом заявляемого устройства является МОУ по патенту RU 2523124, фиг. 2. Он содержит (фиг. 1) первый 1 входной биполярный транзистор, база которого соединена с первым 2 входом устройства, первый 3 входной полевой транзистор с управляющим p-n переходом, затвор которого соединен со вторым 4 входом устройства, исток связан с эмиттером первого 1 входного биполярного транзистора, а сток соединен со входом первого 5 токового зеркала, согласованного с первой 6 шиной источника питания, второй 7 входной биполярный транзистор, база которого соединена с третьим 8 входом устройства, а коллектор подключен к входу второго 9 токового зеркала, согласованного со второй 10 шиной источника питания, второй 11 входной полевой транзистор с управляющим р-n переходом, затвор которого соединен с четвертым 12 входом устройства, а исток связан с эмиттером второго 7 входного биполярного транзистора, причем токовые выходы первого 5 и второго 9 токовых зеркал подключены к токовому выходу устройства 13.

Существенный недостаток известного ОУ состоит в том, что из-за асимметрии, связанной с использованием полевых и биполярных транзисторов, в нем не обеспечивается высокая стабильность напряжения смещения нуля (Uсм) в диапазоне низких температур t°<-60°C, а также в условиях радиации. Данный эффект обусловлен резким (в 50÷100 раз) ухудшением β биполярных транзисторов при низких температурах, а также и при воздействии потока нейтронов (Fn).

Основная задача предлагаемого изобретения состоит в уменьшении нулевого уровня МОУ (напряжения смещения нуля, приведенного к входам МОУ) и повышении его стабильности при низких температурах и воздействии радиации.

Дополнительная задача - повышение быстродействия МОУ в схемах с отрицательной обратной связью - увеличение максимальной скорости нарастания выходного напряжения МОУ (ϑвых) при импульсном изменении входного напряжения.

Поставленные задачи достигаются тем, что в мультидифференциальном операционном усилителе фиг. 1, содержащем первый 1 входной биполярный транзистор, база которого соединена с первым 2 входом устройства, первый 3 входной полевой транзистор с управляющим р-n переходом, затвор которого соединен со вторым 4 входом устройства, исток связан с эмиттером первого 1 входного биполярного транзистора, а сток соединен со входом первого 5 токового зеркала, согласованного с первой 6 шиной источника питания, второй 7 входной биполярный транзистор, база которого соединена с третьим 8 входом устройства, а коллектор подключен к входу второго 9 токового зеркала, согласованного со второй 10 шиной источника питания, второй 11 входной полевой транзистор с управляющим р-n переходом, затвор которого соединен с четвертым 12 входом устройства, а исток связан с эмиттером второго 7 входного биполярного транзистора, причем токовые выходы первого 5 и второго 9 токовых зеркал подключены к токовому выходу устройства 13, предусмотрены новые элементы и связи - коллектор первого 1 входного биполярного транзистора соединен со входом первого 14 дополнительного токового зеркала, согласованного со второй 10 шиной источника питания, выход которого подключен к входу первого 5 токового зеркала, а сток второго 11 входного полевого транзистора с управляющим p-n переходом соединен со входом второго 15 дополнительного токового зеркала, согласованного с первой 6 шиной источника питания, токовый выход которого соединен со входом второго 9 токового зеркала.

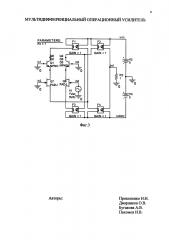

На фиг. 1 показана схема МОУ-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с формулой изобретения.

На фиг. 3 приведена схема заявляемого устройства фиг. 2 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск).

На фиг. 4 показаны зависимости выходного тока МОУ фиг. 3 от потока нейтронов (а) и температуры в диапазоне от минус 60°С до плюс 80°С (б).

На фиг. 5 приведена схема заявляемого устройства фиг. 2 в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_4 НПО «Интеграл» (г. Минск) для случая его инвертирующего включения в схеме с отрицательной обратной связью, которая вводится на базу транзистора Q1. При этом для уменьшения выходного сопротивления в схеме предусмотрен буферный усилитель (Gain=1). В схеме также используется традиционная цепь коррекции АЧХ (конденсатор С1). Резистор R2 моделирует эквивалентное сопротивление в высокоимпедансном узле МОУ.

На фиг. 6 показаны амплитудно-частотные характеристики операционного усилителя фиг. 5 без отрицательной обратной связи и с отрицательной обратной связью (ООС).

На фиг. 7 представлена схема заявляемого устройства фиг. 2 в режиме измерения зависимости выходного тока (тока в резисторе R2) от входных напряжений, подаваемых на различные входы МОУ (IN1, IN2, IN3, IN4).

Из графиков фиг. 8 схемы фиг. 7 следует, что предлагаемое устройство характеризуется широким диапазоном линейной работы, в пределах которого выходной ток МОУ пропорционален входным напряжениям МОУ. Это является одним из факторов, способствующих повышению максимальной скорости нарастания выходного напряжения МОУ.

На фиг. 9 представлена схема МОУ фиг. 2 со 100% отрицательной обратной связью в режиме измерения максимальной скорости нарастания выходного напряжения для случая, когда импульсное входное напряжение с амплитудой 1В подавалось на затвор транзистора Q8.

На фиг. 10 представлены графики изменения выходного напряжения МОУ при импульсном входном сигнале положительной (фиг. 10а) и отрицательной (фиг. 10б) полярностях. Из данных графиков следует, что максимальная скорость нарастания выходного напряжения ОУ фиг. 10а имеет повышенное значение ϑвых=251 В/мкс, а для отрицательного фронта составляет ϑвых=400 В/мкс. Данные значения ϑвых удовлетворяют многим применениям МОУ.

Мультидифференциальный операционный усилитель фиг. 2 содержит первый 1 входной биполярный транзистор, база которого соединена с первым 2 входом устройства, первый 3 входной полевой транзистор с управляющим р-n переходом, затвор которого соединен со вторым 4 входом устройства, исток связан с эмиттером первого 1 входного биполярного транзистора, а сток соединен со входом первого 5 токового зеркала, согласованного с первой 6 шиной источника питания, второй 7 входной биполярный транзистор, база которого соединена с третьим 8 входом устройства, а коллектор подключен к входу второго 9 токового зеркала, согласованного со второй 10 шиной источника питания, второй 11 входной полевой транзистор с управляющим р-n переходом (ПТ), затвор которого соединен с четвертым 12 входом устройства, а исток связан с эмиттером второго 7 входного биполярного транзистора, причем токовые выходы первого 5 и второго 9 токовых зеркал подключены к токовому выходу устройства 13. В схеме коллектор первого 1 входного биполярного транзистора соединен со входом первого 14 дополнительного токового зеркала, согласованного со второй 10 шиной источника питания, выход которого подключен к входу первого 5 токового зеркала, а сток второго 11 входного полевого транзистора с управляющим р-n переходом соединен со входом второго 15 дополнительного токового зеркала, согласованного с первой 6 шиной источника питания, токовый выход которого соединен со входом второго 9 токового зеркала.

В схеме фиг. 2 свойства нагрузки моделируются резистором 16. В частных случаях токовый выход устройства 13 может быть связан с дополнительным буферным усилителем, обеспечивающим низкое выходное сопротивление устройства (см. фиг. 5, Gain=1).

Рассмотрим работу МОУ-прототипа фиг. 1 в статическом режиме для случая, когда все входы МОУ связаны с общей шиной.

В этом случае эмиттерные токи первого 1 и второго 7 входных биполярных транзисторов определяются геометрией первого 3 и второго 11 входных полевых транзисторов и зависят от величины тока истока ПТ 3 и 11 Iси=I0, который определяется при Uзи=Uэб≈0,7 В. При этом коллекторные токи входных биполярных транзисторов 1 и 7 отличаются от I0 на величину тока базы Iбр

где Iбр - ток базы входных биполярных транзисторов 1 и 7.

Причем

где β - коэффициент усиления по току базы входных биполярных транзисторов 1 и 7.

Если считать, что коэффициенты передачи по току всех токовых зеркал (5 и 9) равны единице (Ki=1), то на основе первого закона Кирхгофа можно найти выходной статический ток ОУ, который является током ошибки

Таким образом, напряжение смещения нуля МОУ, приведенное к его входам:

где SДК - крутизна преобразования входного напряжения МОУ в его выходной ток Iвых.

Таким образом, в связи с малым значением SДК дифференциального каскада на полевых транзисторах, известная схема МОУ-прототипа фиг. 1 характеризуется повышенным значением Uсм и высокой нестабильностью нулевого уровня (ΔUсм).

В заявленном МОУ фиг. 2 выходной статический ток ошибки в аналогичном режиме включения входов МОУ определяется выражением

Для того, чтобы нестабильность I0 не влияла на Iвых. необходимо, чтобы коэффициенты передачи токовых зеркал МОУ удовлетворяли условиям

или

При Ki9=Ki5=Ki14=Ki15 условие (7) выполняется.

Аналогично, чтобы ток базы Iбр, существенно возрастающий при низких температурах и воздействии радиации (абсолютное уменьшение β до 2-3 единиц при Т=-190°C), не влиял на Iвых.0, необходимо выполнение следующего условия

Если Ki5=Ki9=Ki14, то данная составляющая выходного тока ошибки будет близка к нулю.

Таким образом, в заявленной схеме обеспечивается близкая к нулю статическая ошибка выходного тока (Iвых.0≈0). Как следствие, напряжение смещения нуля МОУ (Uсм) (4) также близко к нулю. Данные выводы подтверждаются результатами компьютерного моделирования (фиг. 4).

Кроме этого, предлагаемый МОУ имеет достаточно высокое усиление по напряжению (фиг. 6) - около 100 дБ.

При импульсных изменениях входного напряжения в схеме фиг. 5 заявляемое устройство имеет относительно высокую скорость нарастания выходного напряжения [18]. Это связано с тем, что входной каскад МОУ характеризуется высокой линейностью проходной характеристики (фиг. 7, имеет широкий диапазон активной работы, измеряемый напряжением ограничения), что положительно влияет на ϑвых [18].

Таким образом, предлагаемое устройство имеет существенные преимущества в сравнении с известными и может найти широкое применение в системах обработки радиотехнических сигналов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент WO 03/04328, fig. 6.

2. Патентная заявка US 2008/0186091, fig. 4.

3. Патент US 6.469.576, fig. 2.

4. Патент US 7.205.799, fig. 4, fig. 5.

5. A.c. СССР 537435, фиг. 1.

6. Патент US 6.388.519, fig. 36.

7. Патентная заявка US 2003/0006841, fig. 1.

8. Патентная заявка US 2013/0099782, fig. 2.

9. Патент US 6.255.807, fig. 5.

10. Патент US 6.400.225, fig. 3.

11. Патентная заявка US 2003/0132803, fig. 7.

12. Патент US 6.977.526, fig. 1.

13. Патент RU 2517699, фиг. 3.

14. The main connection circuits of the radiation-hardened differential difference amplifier based on the bipolar and field effect technological process / N.N. Prokopenko, O.V. Dvornikov, N.V. Butyrlagin, A.V. Bugakova // 2014 12th International conference on actual problems of electronic instrument engineering (APEIE - 2014) proceedings in 7 Volumes; Novosibirsk, October 2-4, 2014. - Novosibirsk State Technical University. - Vol. 1. - P. 29-34 DOI: 10.1109/APEIE.2014.7040870 (fig. 2).

15. Крутчинский, С.Г. Входные каскады дифференциальных и мультидифференциальных операционных усилителей с высоким ослаблением синфазного напряжения [Текст] / С.Г. Крутчинский, А.Е. Титов, М.С. Цыбин // Проблемы разработки перспективных микро- и наноэлектронных систем: Сборник трудов. - М.: ИППМ РАН, 2010. - С. 537-542. - ISSN 2078-7707.

16. Прокопенко Н.Н., Дифференциальные и мультидифференциальные усилители в элементном базисе радиационно-стойкого техпроцесса АБМК_1.5 [Текст] / Прокопенко Н.Н., Серебряков А.И., Бутырлагин Н.В. // Известия ЮФУ. Технические науки. Тематический выпуск «Проблемы управления в топливно-энергетических комплексах и энергосберегающие технологии». 2014. - №5 (154). - С. 58-66.

17. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

18. Операционные усилители с непосредственной связью каскадов / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: Энергия, 1979. - 148 с.

Мультидифференциальный операционный усилитель, содержащий первый входной биполярный транзистор, база которого соединена с первым входом устройства, первый входной полевой транзистор с управляющим р-n переходом, затвор которого соединен со вторым входом устройства, исток связан с эмиттером первого входного биполярного транзистора, а сток соединен со входом первого токового зеркала, согласованного с первой шиной источника питания, второй входной биполярный транзистор, база которого соединена с третьим входом устройства, а коллектор подключен к входу второго токового зеркала, согласованного со второй шиной источника питания, второй входной полевой транзистор с управляющим р-n переходом, затвор которого соединен с четвертым входом устройства, а исток связан с эмиттером второго входного биполярного транзистора, причем токовые выходы первого и второго токовых зеркал подключены к токовому выходу устройства, отличающийся тем, что коллектор первого входного биполярного транзистора соединен со входом первого дополнительного токового зеркала, согласованного со второй шиной источника питания, выход которого подключен к входу первого токового зеркала, а сток второго входного полевого транзистора с управляющим р-n переходом соединен со входом второго дополнительного токового зеркала, согласованного с первой шиной источника питания, токовый выход которого соединен со входом второго токового зеркала.