Стабилизированный электропривод

Иллюстрации

Показать всеИзобретение относится к области электротехники и может быть использовано в высокоточных электроприводах. Технический результат - улучшение динамических характеристик электропривода. Для этого предложен стабилизированный электропривод, который содержит электродвигатель, импульсный датчик скорости, частотно-фазовый дискриминатор, частотно-задающий блок, дифференцирующий элемент, управляемый ключ, сумматор, преобразователь, блок формирования управляющих сигналов, исключающее ИЛИ, три D-триггера, нелинейный элемент типа «Зона нечувствительности», элемент НЕ, два элемента И, частотный дискриминатор, мультиплексор. 3 ил.

Реферат

Изобретение относится к области электротехники и может быть использовано в высокоточных электроприводах.

Известен стабилизированный электропривод (АС №1302411 от 07.04.1987), содержащий электродвигатель, импульсный датчик частоты вращения, импульсный частотно-фазовый дискриминатор, корректирующее устройство, состоящее из фазового дискриминатора, бесконтактного ключа, блока измерения частоты и дифференцирующего блока, сумматор, частотно-задающий блок и силовой преобразователь, причем выход импульсного датчика частоты вращения подключен к первому входу импульсного частотно-фазового дискриминатора и первому входу фазового дискриминатора, второй вход импульсного частотно-фазового дискриминатора соединен с вторым входом фазового дискриминатора и выходом частотно-задающего блока, выход фазового дискриминатора соединен с входом бесконтактного ключа, управляющий вход которого соединен с выходом блока измерения частоты, а выход - с входом дифференцирующего блока, причем выход импульсного частотно-фазового дискриминатора соединен с входам блока измерения частоты и первым входом сумматора, выход дифференцирующего блока соединен с вторым входом сумматора, а выход сумматора подключен через силовой преобразователь к якорной обмотке электродвигателя.

Недостатком такого устройства является низкое быстродействие электропривода в режиме синхронизации.

Наиболее близким техническим решением к заявляемому устройству является стабилизированный электропривод (АС №1508334 от 15.09.1989), содержащий электродвигатель постоянного тока с установленным на его валу импульсным датчиком скорости, выход которого подключен к первым входам соответственно импульсного частотно-фазового и фазового дискриминаторов, вторые входы которых объединены и подключены к выходу частотно-задающего блока, первый выход импульсного частотно-фазового дискриминатора подключен к частотно-измерительному блоку и через последовательно соединенные сумматоры и преобразователь - к якорной цепи электродвигателя, выход дифференцирующего элемента через управляемый ключ соединен со вторым входом сумматора, кроме того, электропривод содержит сумматор-вычитатель и последовательно включенные элемент задержки и логический элемент ИЛИ, выход которого соединен с управляющим входом ключа, второй вход логического элемента ИЛИ подключен к выходу частотно-измерительного блока и входу элемента задержки, первый вход сумматора-вычитателя подключен к выходу фазового дискриминатора, второй и третий входы сумматора-вычитателя соединены соответственно со вторым и третьим выходами импульсного частотно-фазового дискриминатора, выход сумматора-вычитателя подключен к входу дифференцирующего элемента.

Недостатком такого устройства является низкое быстродействие электропривода в режиме синхронизации.

Техническим результатом полезной модели является улучшение динамических характеристик электропривода.

Данный технический результат достигается тем, что в стабилизированный электропривод, содержащий электродвигатель постоянного тока с установленным на его валу импульсным датчиком скорости, выход которого подключен к первому входу импульсного частотно-фазового дискриминатора, второй вход которого подключен к выходу частотно-задающего блока, дифференцирующий элемент, выход которого через управляемый ключ соединен со вторым входом сумматора, выход сумматора подключен к входу преобразователя, выход которого подключен к якорной цепи электродвигателя, согласно заявляемому техническому решению введены блок формирования управляющих сигналов, исключающее ИЛИ, три D-триггера, нелинейный элемент типа «Зона нечувствительности», элемент НЕ, два элемента И, частотный дискриминатор, мультиплексор, первый выход импульсного частотно-фазового дискриминатора подключен к первому входу блока формирования управляющих сигналов и входу дифференцирующего элемента, первый выход блока формирования управляющих сигналов подключен к первому входу элемента «Исключающее ИЛИ» и к второму информационному входу мультиплексора, второй выход блока формирования управляющих сигналов подключен к второму входу элемента «Исключающее ИЛИ», выход которого подключен к тактовому входу первого D-триггера, выход первого D-триггера подключен к второму входу второго элемента И, выход дифференцирующего элемента подключен к входу нелинейного элемента типа «Зона нечувствительности», выход которого подключен к входу элемента НЕ, выход элемента НЕ подключен к первым входам первого и второго элементов И, выход первого элемента И подключен к второму входу блока формирования управляющих сигналов и к тактовому входу второго D-триггера, первый вход частотного дискриминатора подключен к выходу импульсного датчика скорости, второй вход частотного дискриминатора подключен к выходу частотно-задающего блока, выход частотного дискриминатора подключен к тактовому входу третьего D-триггера, выход которого подключен к второму входу первого элемента И, второй выход импульсного частотно-фазового дискриминатора подключен к первому информационному входу мультиплексора, выход которого подключен к первому входу сумматора, выход второго элемента И подключен к третьему входу импульсного частотно-фазового дискриминатора и к входам сброса первого, второго и третьего D-триггеров, выход второго D-триггера подключен к адресному входу мультиплексора, информационные входы первого, второго и третьего D-триггеров подключены к источнику сигнала логической «1», третий выход импульсного частотно-фазового дискриминатора 3 подключен к второму входу управляемого ключа 6, кроме того, блок формирования управляющих сигналов состоит из делителя на два, запоминающего устройства, элемента сравнения и компаратора, вход делителя на два является первым входом блока формирования управляющих сигналов и подключен ко второму входу элемента сравнения и входу компаратора, выход делителя на два подключен к первому входу запоминающего устройства, второй вход которого является вторым входом блока формирования управляющих сигналов, выход запоминающего устройства подключен к первому входу элемента сравнения, выходы элемента сравнения и компаратора являются соответственно первым и втором выходами блока формирования управляющих сигналов.

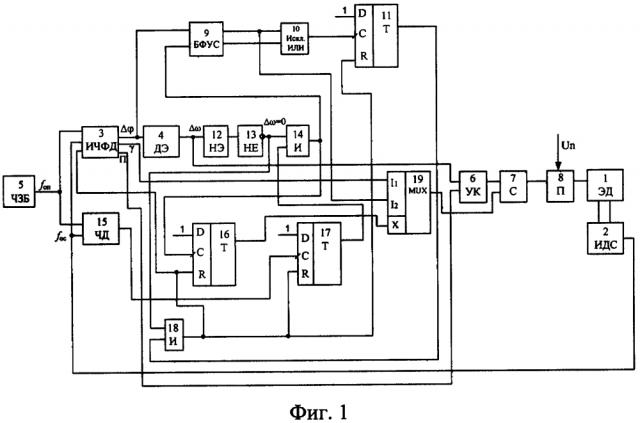

Сущность технического решения пояснена чертежами, где на фиг. 1 приведена функциональная электрическая схема предлагаемого устройства; на фиг. 2 приведен функциональная схема блока формирования управляющих сигналов; на фиг. 3 приведен фазовый портрет работы стабилизированного электропривода.

Стабилизированный электропривод содержит электродвигатель постоянного тока 1, импульсный датчик скорости 2, импульсный частотно-фазовый дискриминатор 3, дифференцирующий элемент 4, частотно-задающий блок 5, управляемый ключ 6, сумматор 7, преобразователь 8, блок формирования управляющих сигналов 9, элемент «исключающее ИЛИ» 10, первый, второй, третий D-триггеры 11, 16, 17, нелинейный элемент типа «Зона нечувствительности» 12, элемент НЕ 13, два элемента И 14, И 18, частотный дискриминатор 15, мультиплексор 19. БФУС содержит делитель напряжения 20 на два, запоминающее устройство 21, элемент сравнения 22 и компаратор 23.

На валу электродвигателя 1 установлен импульсный датчик скорости 2, выход которого подключен к первому входу импульсного частотно-фазового дискриминатора 3, второй вход которого подключен к выходу частотно-задающего блока 5, первый выход импульсного частотно-фазового дискриминатора 3 подключен к первому входу дифференцирующего элемента 4 и первому входу блока формирования управляющих сигналов 9, первый выход блока формирования управляющих сигналов 9 подключен к первому входу элемента «Исключающее ИЛИ» 10 и к второму информационному входу мультиплексора 19, второй выход блока формирования управляющих сигналов 9 подключен к второму входу элемента «Исключающее ИЛИ» 10, выход которого подключен к тактовому входу первого D-триггера 11, выход первого D-триггера подключен к второму входу второго элемента И 18, выход дифференцирующего элемента 4 подключен к информационному (первому) входу управляемого ключа 6 и к входу нелинейного элемента типа «Зона нечувствительности» 12, выход которого подключен к входу элемента НЕ 13, выход элемента НЕ подключен к первым входам элементов первого И 14 и второго И 18, выход первого элемента И подключен к второму входу блока формирования управляющих сигналов 9 и к тактовому входу второго D-триггера 16, первый вход частотного дискриминатора 15 подключен к выходу импульсного датчика скорости 2, второй вход частотного дискриминатора 15 подключен к выходу частотно-задающего блока 5, выход частотного дискриминатора 15 подключен к тактовому входу третьего D-триггера 17, выход которого подключен к второму входу первого элемента И 14, второй выход импульсного частотно-фазового дискриминатора 3 подключен к первому информационному входу мультиплексора 19, выход которого подключен к первому входу сумматора 7, выход второго элемента И 18 подключен к третьему входу импульсного частотно-фазового дискриминатора 3 и к входам сброса первого, второго и третьего D-триггеров 11, 16, 17, выход второго D-триггера подключен к адресному входу мультиплексора, информационные входы первого, второго и третьего D-триггеров подключены к источнику сигнала логической «1», третий выход импульсного частотно-фазового дискриминатора 3 подключен к второму входу управляемого ключа 6, выход управляемый ключа 6 подключен к второму входу сумматора 7, выход сумматора 7 подключен к входу преобразователя 8, выход которого подключен к якорной цепи электродвигателя, кроме того, блок формирования управляющих сигналов состоит из делителя на два 20, запоминающего устройства 21, элемента сравнения 22 и компаратора 23, вход делителя на два 20 является первым входом блока формирования управляющих сигналов 9 и подключен ко второму входу элемента сравнения 22 и входу компаратора 23, выход делителя на два 20 подключен к первому входу запоминающего устройства 21, второй вход которого является вторым входом блока формирования управляющих сигналов 9, выход запоминающего устройства 21 подключен к первому входу элемента сравнения 22, выходы элемента сравнения 22 и компаратора 23 являются соответственно первым и втором выходами блока формирования управляющих сигналов 9.

Стабилизированный электропривод работает следующим образом.

Электродвигатель 1 служит основой для построения электропривода.

Импульсный датчик скорости 2 закрепляется на валу электродвигателя 1 и реализуется на основе фотоэлектрического преобразователя угла, формирующего z импульсов за оборот вала электродвигателя 1.

Импульсный частотно-фазовый дискриминатор 3 предназначен для сравнения частот и фаз входных частотных сигналов: опорной частоты ƒоп, формируемой на выходе частотно-задающего блока 5, и частоты в канале обратной связи ƒос, формируемой на выходе импульсного датчика скорости 2.

Импульсный частотно-фазовый дискриминатор 3 может находиться в трех режимах работы: режим насыщения при разгоне, режим насыщения при торможении и режим фазового сравнения. В режимах насыщения импульсного частотно-фазового дискриминатора 3 на его выходе формируется сигнал γ, равный логической «1» (для разгона) или логическому «0» (при торможении). В режиме фазового сравнения выходной сигнал представляет собой последовательность импульсов, период следования которых равен периоду опорной частоты, а длительность пропорциональна фазовому сдвигу импульсов Δϕ и соответственно пропорциональна угловой ошибке электропривода, что позволяет реализовать в режиме синхронизации электропривода замкнутую систему управления. Изменение режима работы импульсного частотно-фазового дискриминатора 3 происходит в моменты времени, когда два импульса одной из сравниваемых частот проходят между двумя соседними импульсами другой частоты; на фазовом портрете (Фиг. 3) этим моментам времени соответствуют линии переключения, описываемые выражениями Δα=ϕ0/2±nϕ0, где ϕ0=2π/z, n=0, 1 … z/2. Импульсный частотно-фазовый дискриминатор 3 имеет два дополнительных выхода: формирования сигнала фазовой ошибки Δϕ без блокировки в режимах насыщения и индикации режима фазового сравнения П импульсного частотно-фазового дискриминатора 3. Такая реализация может быть осуществлена по известной функциональной схеме, приведенной в монографии Бубнова А.В. Вопросы теории и проектирования прецизионных синхронно-синфазных электроприводов постоянного тока. - Омск: Редакция журнала «Омский научный вестник», 2005. - 190 с. (Рис. 8.6 на стр. 147).

Частотно-задающий блок 5 формирует импульсы опорной частоты ƒоп, определяющей угловую скорость электропривода ω.

Дифференцирующий элемент 4 предназначен для дифференцирования выходного сигнала импульсного частотно-фазового дискриминатора 3, пропорционального фазовому рассогласованию сравниваемых частотных сигналов и соответственно угловой ошибке электропривода. В результате на его выходе формируется сигнал, пропорциональный ошибке по угловой скорости электропривода.

Управляемый ключ 6 предназначен для подключения сигнала ошибки по угловой скорости, формируемого на выходе дифференцирующего элемента 4, на вход сумматора 7 в режиме фазового сравнения импульсного частотно-фазового дискриминатора 3.

Сумматор 7 предназначен для суммирования в режиме фазового сравнения импульсного частотно-фазового дискриминатора 3 сигнала ошибки по угловой скорости и, в зависимости от режима работы системы управления, выходного сигнала импульсного частотно-фазового дискриминатора 3 γ или сигнала квазиоптимального по быстродействию управления Ф, формируемого системой управления электропривода.

Преобразователь 8 предназначен для формирования токов в обмотках электродвигателя 1 на основе управляющего сигнала с выхода сумматора 7.

Блок формирования управляющих сигналов 9 формирует сигнал Ф для организации квазиоптимального по быстродействию управления электроприводом в режиме синхронизации и сигнал, определяющий знак фазовой ошибки. Блок формирования управляющих сигналов 9 выполнен по схеме, представленной на Фиг. 2, и содержит делитель 20 напряжения на 2, запоминающее устройство 21, элемент сравнения 22 и компаратор 23. Делитель 20 напряжения на 2 используется для определения половины значения сигнала фазовой ошибки Δϕ, поступающего на первый вход блока формирования управляющих сигналов 9, с целью последующего запоминания полученного значения в запоминающем устройстве 21 в момент времени, соответствующий началу квазиоптимального по быстродействию режима синхронизации электропривода. Запоминание величины аналогового сигнала Δϕ/2, поступающего на информационный вход запоминающего устройства 21, осуществляется в момент подачи на вход записи импульса, поступающего на второй вход блока формирования управляющих сигналов 9. Элемент сравнения 22 осуществляет сравнение текущего значения фазовой ошибки Δϕ и запомненного значения Δϕn/2 в запоминающем устройстве 21. Компаратор 23 определяет знак входного сигнала, при положительном значении на выходе формирует сигнал логической «1», а при отрицательном - логического «0».

Логический элемент «Исключающее ИЛИ» 10 осуществляет сложение по модулю 2 входных логических сигналов, формирует сигнал логической «1» на временном интервале t3-t4 (t3'-t4') и предназначен для разрешения формирования сигнала завершения квазиоптимального по быстродействию регулирования в режиме синхронизации электропривода.

D-триггеры 11, 16, 17 предназначены для задания требуемых временных интервалов для организации управления в режиме синхронизации. Начало интервала формируется в момент прихода импульса на тактовый вход С D-триггеров 11, 16, 17 и записи в них логической «1» с информационного входа D. Сброс D-триггеров 11, 16, 17 в исходное состояние логического «0» осуществляется в момент прихода импульса на R-вход.

Нелинейный элемент типа «Зона нечувствительности» 12 предназначен для определения значения ошибки по угловой скорости Δω, близкого к нулю.

Логический элемент НЕ 13 осуществляет инверсию входного сигнала.

Логические элементы И 14, 18 осуществляют операцию логического умножения входных сигналов.

Частотный дискриминатор 15 предназначен для определения значения величины ошибки по угловой скорости Δω, соответствующей попаданию изображающей точки на линии переключения на фазовом портрете работы электропривода в диапазон значений Δω, соответствующий началу режима синхронизации. Реализация частотного дискриминатора 15 может быть осуществлена по известной функциональной схеме, приведенной в патенте на полезную модель 134375 РФ, МПК H03D 13/00. Частотно-фазовый дискриминатор.

Мультиплексор 19 в зависимости от значения адресного сигнала X подключает к выходу первый I1 или второй I2 информационные входы, обеспечивая подачу на первый вход сумматора 7 сигнала γ с второго выхода импульсного частотно-фазового дискриминатора 3 или сигнал Ф с первого выхода блока формирования управляющих сигналов 9.

При включении питания электродвигатель 1 разгоняется до частоты вращения, при которой частоты частотно-задающего блока 5 и импульсного датчика 2 скорости равны. При этом импульсный частотно-фазовый дискриминатор 3 находится в режиме насыщения, на его втором выходе формируется сигнал γ=1, который через открытый первый вход мультиплексора 19 (на адресный вход X подается сигнал логического «0») и первый вход сумматора 7 поступает на преобразователь 8, обеспечивая разгон электродвигателя 1 с постоянным ускорением.

В момент времени t1 (t1' для других начальных условий процесса синхронизации), соответствующий попаданию изображающей точки на фазовом портрете (Фиг. 3) на линию переключения, соответствующую выражению Δα=-ϕ0/2, в область значений Δω, при которых возможна синхронизация электропривода (Δω<Δωmax). На выходе частотного дискриминатора 15, осуществляющего сравнение частот входных сигналов ƒоп и ƒос, формируется сигнал логической «1», по которому происходит установка третьего D-триггера 17 в состояние логической «1», открывающей цифровой ключ, выполненный на элементе И 14 для прохождения сигнала с инвертора НЕ 13. Режим разгона электродвигателя 1 продолжается до тех пор, пока значение Δω не станет близким к нулю (момент времени t2 или t2'). Данное значение Δω определяется с помощью нелинейного элемента типа «Зона нечувствительности» 12, подключенного к выходу дифференцирующего элемента 4, на выходе которого формируется сигнал Δω путем дифференцирования сигнала фазовой ошибки Δϕ с первого выхода импульсного частотно-фазового дискриминатора 3. При попадании изображающей точки на фазовом портрете в область Δω≈0 на выходе нелинейного элемента 12 формируется сигнал логического «0», который через инвертор НЕ 13 и открытый цифровой ключ И14 поступает на тактовый вход второго D-триггера 16, устанавливая D-триггер 16 в состояние логической «1», что соответствует началу квазиоптимального по быстродействию режима синхронизации электропривода (оптимальный режим в дискретной системе управления электроприводом не может быть реализован). Выходной сигнал с D-триггера 16 поступает на адресный вход X мультиплексора 19, разрешая прохождение на его выход сигнала управления Ф квазиоптимальным по быстродействию режимом синхронизации электропривода.

Одновременно выходной сигнал цифрового ключа И 14 поступает на второй вход блок формирования управляющих сигналов 9, связанный со входом записи запоминающего устройства 21. На информационный вход запоминающего устройства 21 поступает сигнал Δϕ/2 с делителя напряжения 20 на два, на вход которого, являющийся первым входом блока формирования управляющих сигналов 9, подается с первого выхода импульсного частотно-фазового дискриминатора 3 сигнал Δϕ, не имеющий блокировки при больших частотных рассогласованиях входных сигналов импульсного частотно-фазового дискриминатора 3. В момент времени t2 (t2') происходит запоминание в запоминающем устройстве 21 текущего значения Δϕн/2 (начального значения для режима синхронизации) и формирование сигнала управления Ф квазиоптимальным по быстродействию режимом синхронизации электропривода с помощью элемента сравнения 22. При положительном значении фазовой ошибки на выходе элемента сравнения 22 формируется сигнал логической «1», что обеспечивает продолжение режима разгона электродвигателя 1, при отрицательном значении фазовой ошибки на выходе элемента сравнения 22 формируется сигнал логической «0», что обеспечивает переключение электропривода в режим торможения электродвигателя 1.

В момент времени t3 (t3'), соответствующий отработке половины значения начальной фазовой ошибки Δϕн, происходит изменение управляющего сигнала Ф на противоположное значение, что соответствует изменению режима разгона на режим торможения электропривода, или наоборот. В результате осуществляется отработка второй половины начального фазового рассогласования Δϕн с ускорением противоположного знака, что соответствует отработке начальной фазовой ошибки Δϕн электропривода в режиме, близком к оптимальному по быстродействию (квазиоптимальное по быстродействию управление).

Компаратор 23 позволяет сформировать сигнал знака фазовой ошибки, который, поступая на второй вход логического элемента «Исключающее ИЛИ» 10, изменяет форму сигнала Ф, поступающего на первый вход логического элемента «Исключающее ИЛИ» 10, таким образом, чтобы в момент времени t3 (t3') на выходе логического элемента «Исключающее ИЛИ» 10 формировался передний фронт импульса, используемый для установки первого D-триггера 11 в состояние логической «1».

Отработка начальной фазовой ошибки в режиме квазиоптимального по быстродействию управления заканчивается в момент времени t4 (t4') при попадании изображающей точки на фазовом портрете (Фиг. 3) в область Δω≈0, определяемую с помощью нелинейного элемента типа «Зона нечувствительности» 12. В этот момент времени сигнал с выхода нелинейного элемента 12 через инвертор 13 поступает на информационный вход цифрового ключа И 18, выполненного на логическом элементе И (логическое умножение). На управляющий вход цифрового ключа И 18 поступает сигнал логической «1» с выхода первого D-триггера 11, в результате сигнал с информационного входа цифрового ключа И 18 проходит на его выход и далее на R-входы первого, второго и третьего D-триггеров 11, 16, 17, сбрасывая D-триггеры 11, 16, 17 в состояние логического «0», и на третий вход (принудительной установки) импульсного частотно-фазового дискриминатора 3, обеспечивая его принудительный перевод в режим фазового сравнения. Выходной сигнал второго D-триггера 16 принимает значение логического «0» и, поступая на адресный вход X мультиплексора 19, подключает сигнал у со второго выхода импульсного частотно-фазового дискриминатора 3 через первый информационный вход мультиплексора 19 к первому входу сумматора 7. На третьем выходе импульсного частотно-фазового дискриминатора 3 формируется сигнал П=1, соответствующий режиму фазового сравнения, который, поступая на управляющий вход аналогового управляемого ключа 6, открывает его, пропуская через информационный вход выходной сигнал дифференцирующего элемента 4, пропорциональный ошибке по угловой скорости Δω, на второй вход сумматора 7. В результате на выходе сумматора 7 формируется управляющий сигнал, содержащий сигнал фазовой ошибки Δϕ и его производную Δω. Режим квазиоптимального по быстродействию регулирования заканчивается, и электропривод переходит в режим работы замкнутой по фазовой ошибке системы управления, что позволяет обеспечить устойчивую работу электропривода в режиме фазового сравнения импульсного частотно-фазового дискриминатора 3.

Таким образом, предлагаемое техническое решение позволяет повысить быстродействие стабилизированного электропривода за счет организации квазиоптимального по быстродействию управления в режиме синхронизации электропривода.

Стабилизированный электропривод, содержащий электродвигатель постоянного тока с установленным на его валу импульсным датчиком скорости, выход которого подключен к первому входу импульсного частотно-фазового дискриминатора, второй вход которого подключен к выходу частотно-задающего блока, дифференцирующий элемент, выход которого через управляемый ключ соединен со вторым входом сумматора, выход сумматора подключен к входу преобразователя, выход которого подключен к якорной цепи электродвигателя, отличающийся тем, что в него введены блок формирования управляющих сигналов, исключающее ИЛИ, три D-триггера, нелинейный элемент типа «Зона нечувствительности», элемент НЕ, два элемента И, частотный дискриминатор, мультиплексор, первый выход импульсного частотно-фазового дискриминатора подключен к первому входу блока формирования управляющих сигналов и входу дифференцирующего элемента, первый выход блока формирования управляющих сигналов подключен к первому входу элемента «Исключающее ИЛИ» и к второму информационному входу мультиплексора, второй выход блока формирования управляющих сигналов подключен к второму входу элемента «Исключающее ИЛИ», выход которого подключен к тактовому входу первого D-триггера, выход первого D-триггера подключен к второму входу второго элемента И, выход дифференцирующего элемента подключен к входу нелинейного элемента типа «Зона нечувствительности», выход которого подключен к входу элемента НЕ, выход элемента НЕ подключен к первым входам первого и второго элементов И, выход первого элемента И подключен к второму входу блока формирования управляющих сигналов и к тактовому входу второго D-триггера, первый вход частотного дискриминатора подключен к выходу импульсного датчика скорости, второй вход частотного дискриминатора подключен к выходу частотно-задающего блока, выход частотного дискриминатора подключен к тактовому входу третьего D-триггера, выход которого подключен к второму входу первого элемента И, второй выход импульсного частотно-фазового дискриминатора подключен к первому информационному входу мультиплексора, выход которого подключен к первому входу сумматора, выход второго элемента И подключен к третьему входу импульсного частотно-фазового дискриминатора и к входам сброса первого, второго и третьего D-триггеров, выход второго D-триггера подключен к адресному входу мультиплексора, информационные входы первого, второго и третьего D-триггеров подключены к источнику сигнала логической «1», третий выход импульсного частотно-фазового дискриминатора подключен к второму входу управляемого ключа, кроме того, блок формирования управляющих сигналов состоит из делителя на два, запоминающего устройства, элемента сравнения и компаратора, вход делителя на два является первым входом блока формирования управляющих сигналов и подключен ко второму входу элемента сравнения и входу компаратора, выход делителя на два подключен к первому входу запоминающего устройства, второй вход которого является вторым входом блока формирования управляющих сигналов, выход запоминающего устройства подключен к первому входу элемента сравнения, выходы элемента сравнения и компаратора являются соответственно первым и втором выходами блока формирования управляющих сигналов.