Подложка матрицы и жидкокристаллическая панель

Иллюстрации

Показать всеИзобретение относится к технологии изготовления дисплеев и, более конкретно, к подложке матрицы и жидкокристаллической панели. Каждый пиксель подложки матрицы включает первый электрод пикселя, второй электрод пикселя и третий электрод пикселя. Помимо этого, пиксель, кроме того, включает управляющую схему для действия на второй электрод пикселя, чтобы изменить напряжение второго электрода пикселя. Третий электрод пикселя соединяется с вторым электродом пикселя через третий транзистор. В режиме двухмерного отображения три электрода пикселя находятся в состоянии отображения соответствующих двухмерных изображений. В режиме трехмерного отображения третий электрод пикселя находится в состоянии отображения соответствующих черных изображений, и первый и второй электроды пикселя находятся в состоянии отображения соответствующих трехмерных изображений. Технический результат заключается в уменьшении искажения цвета в режимах двухмерного и трехмерного отображения. 3 н. и 17 з.п. ф-лы, 6 ил.

Реферат

ПРЕДПОСЫЛКИ ДЛЯ СОЗДАНИЯ ИЗОБРЕТЕНИЯ

ОБЛАСТЬ ТЕХНИКИ

[0001] Настоящее раскрытие относится к технологии изготовления дисплеев и, более конкретно, к подложке матрицы и жидкокристаллической панели.

ОПИСАНИЕ УРОВНЯ ТЕХНИКИ

[0002] ЖК-дисплеи с вертикальным выравниванием (VA) характеризуются признаками, включающими быстрое время отклика и высокую контрастность, что позволило им стать текущей тенденцией в области ЖК-дисплеев. Однако выравнивание и скорость отражения жидкого кристалла неодинаковые при разном угле обзора, и, таким образом, скорость передачи низкая при большом угле отклонения. Цвет, отображаемый при угле отклонения и виде по центру разный, особенно при широком угле обзора. Для того чтобы решить эту проблему, пиксель делят на основную область и субпиксельную область. Каждую из этих областей делят на четыре домена, и, таким образом, каждый из пикселей включает восемь доменов. При подаче разного напряжения на основную область и субпиксельную область выравнивание жидкого кристалла в двух областях будет разным, так что достигается эффект малого изменения цвета (LCS).

[0003] С развитием этой технологии большинство ЖК-дисплеев способны работать в двухмерном режиме и трехмерном режиме. Согласно технологии круговой поляризации экрана 3D-телевизора (FPR) пиксели, расположенные в двух соседних строках, соответствуют левому глазу и правому глазу, чтобы создавать сигналы изображения дли левого глаза и сигналы изображения для правого глаза. Глаза зрителя воспринимают изображение для левого глаза и изображение для правого глаза, и эти изображения затем объединяются в мозге зрителя, создавая эффект трехмерного изображения. Когда изображение для левого глаза и изображение для правого глаза воспринимаются левым глазом и правым глазом зрителя, возникает эффект перекрестных помех, при этом зритель может видеть перекрывание изображений. Для того чтобы уменьшить этот эффект перекрестных помех, применяют черную матрицу. Однако такое решение может приводить к уменьшению формата изображения и снижению яркости в режиме двухмерного отображения.

[0004] При применении конструкции с эффектом LCS вопрос формата изображения и вопрос перекрестных помех могут быть решены. То есть основная область и субпиксельная область отображают нормальные двухмерные изображения в режиме двухмерного отображения и в режиме трехмерного отображения, основная область отображает черное изображение, эквивалентное черной матрице, и субпиксельная область отображает нормальные трехмерные изображения, чтобы уменьшить перекрестные помехи. Однако, когда только субпиксельная область отображает трехмерное изображение в режиме трехмерного отображения, эффект LCS не может быть достигнут.

РАСКРЫТИЕ ИЗОБРЕТЕНИЯ

[0005] Цель изобретения заключается в том, чтобы предложить подложку матрицы и жидкокристаллическую панель, чтобы уменьшить разницу в цвете в режимах двухмерного и трехмерного отображения при большом угле обзора. Помимо этого такие подложка матрицы и жидкокристаллическая панель могут не только увеличить формат изображения в режиме двухмерного отображения, но и уменьшить влияние перекрестных помех в режиме трехмерного отображения.

[0006] В одном аспекте подложка матрицы включает: некоторое число первых линий сканирования, некоторое число вторых линий сканирования и некоторое число пикселей, расположенных в направлении строки, некоторое число линий данных и общий электрод для подвода общего напряжения, и каждый пиксель соответствует одной первой линии сканирования, одной второй линии сканирования и одной линии данных; каждый из пикселей включает первый электрод пикселя, второй электрод пикселя, третий электрод пикселя, первый транзистор, второй транзистор и третий транзистор, каждый из пикселей, кроме того, включает управляющую схему, первый электрод пикселя соединяется с соответствующей первой линией сканирования и соответствующей линией данных через первый транзистор, второй электрод пикселя соединяется с соответствующей первой линией сканирования и первым транзистором через второй транзистор, третий электрод пикселя соединяется с соответствующей второй линией сканирования и вторым электродом пикселя через третий транзистор, управляющая схема соединяется с соответствующими первыми линиями сканирования и соответствующим вторым электродом пикселя, управляющая схема действует на второй электрод пикселя, когда первые линии сканирования подводят сигналы сканирования, чтобы изменить напряжение второго электрода пикселя, и управляющая схема регулирует разницу напряжений между вторым электродом пикселя и общим электродом так, чтобы она не была равна нулю; в режиме двухмерного отображения первая линия сканирования подводит сигналы сканирования, чтобы включить первый транзистор и второй транзистор, на первый электрод пикселя поступают сигналы данных с линий данных через первый транзистор, чтобы находиться в состоянии отображения соответствующих двухмерных изображений, на второй электрод пикселя поступают сигналы данных с линий данных через первый транзистор и второй транзистор поочередно, чтобы быть в состоянии отображения соответствующих двухмерных изображений, управляющая схема действует на второй электрод пикселя, чтобы изменить напряжение второго электрода пикселя в первый раз, первые линии сканирования отключают первый транзистор и второй транзистор, вторые линии сканирования подводят сигналы сканирования, чтобы включить третий транзистор, так что второй электрод пикселя и третий электрод пикселя будут электрически соединены, на третий электрод пикселя поступают сигналы данных с второго электрода пикселя, чтобы быть в состоянии отображения соответствующих двухмерных изображений, так что напряжение второго электрода пикселя изменяется во второй раз третьим электродом пикселя, третий транзистор регулирует разницу напряжений между вторым электродом пикселя и третьим электродом пикселя, чтобы она не была равна нулю, когда третий транзистор включен, так что разница напряжений между любыми двумя из первого электрода пикселя, второго электрода пикселя и третьего электрода пикселя не равна нулю, при этом соответствующие первые линии сканирования текущей строки пикселей и соответствующие вторые линии сканирования предыдущей строки пикселей сканируются одновременно, и предыдущая строка пикселей расположена рядом с текущей строкой пикселей и сканировалась недавно; и в режиме трехмерного отображения вторые линии сканирования отключают третий транзистор, первая линия сканирования подводит сигналы сканирования, чтобы включить первый транзистор и второй транзистор, на первый электрод пикселя поступают сигналы данных с линий данных через первый транзистор, чтобы быть в состоянии отображения соответствующих трехмерных изображений, на второй электрод пикселя поступают сигналы данных с линий данных через первый транзистор и второй транзистор поочередно, чтобы быть в состоянии отображения соответствующих трехмерных изображений, управляющая схема действует на второй электрод пикселя, чтобы изменить напряжение второго электрода пикселя, так что разница напряжений между первым электродом пикселя и вторым электродом пикселя не равна нулю, и третий электрод пикселя находится в состоянии отображения соответствующих черных изображений, когда третий транзистор отключен.

[0007] При этом управляющая схема включает четвертый транзистор и конденсатор перераспределения заряда, четвертый транзистор включает управляющий вывод, первый вывод и второй вывод, управляющий вывод четвертого транзистора соединяется с соответствующими первыми линиями сканирования пикселя, первый вывод четвертого транзистора соединяется с соответствующим вторым электродом пикселя, второй вывод четвертого транзистора соединяется с одним выводом конденсатора перераспределения заряда, конденсатор перераспределения заряда соединяется с общим электродом, первые линии сканирования подводят сигналы сканирования, чтобы включить четвертый транзистор, так что второй электрод пикселя и конденсатор перераспределения заряда будут электрически соединены, напряжение второго электрода пикселя изменяется в первый раз конденсатором перераспределения заряда, и четвертый транзистор регулирует разницу напряжений между вторым электродом пикселя и общим электродом так, чтобы она не была равна нулю.

[0008] При этом четвертым транзистором является тонкопленочный транзистор (TFT), управляющий вывод четвертого транзистора соответствует затвору TFT, первый вывод четвертого транзистора соответствует истоку TFT, второй вывод четвертого транзистора соответствует стоку TFT, и отношение ширина/длина TFT меньше заданного значения, так что разница напряжений между вторым электродом пикселя и общим электродом не равна нулю.

[0009] При этом подложка матрицы, кроме того, включает блок коммутации, расположенный на периферии подложки матрицы, и одну закорачивающую линию, блок коммутации включает некоторое число управляемых транзисторов, управляемый транзистор включает управляющий вывод, входной вывод и выходной вывод, входной вывод каждого из управляемых транзисторов соединяются с соответствующими первыми линиями сканирования строки пикселей, выходной вывод каждого из управляемых транзисторов соединяются с соответствующими вторыми линиями сканирования предыдущей строки пикселей, предыдущая строка пикселей расположена рядом с текущей строкой пикселей, и управляющие выводы управляемых транзисторов соединяются с закорачивающей линией; и в режиме двухмерного отображения закорачивающая линия подводит управляющие сигналы, чтобы включить все управляемые транзисторы, когда соответствующие первые линии сканирования одной строки пикселей подводят сигналы сканирования, эти сигналы сканирования одновременно подаются на вторые линии сканирования, соединенные с выходным выводом управляемого транзистора через управляемый транзистор, чтобы включить третий транзистор в режиме трехмерного отображения, и закорачивающая линия подводит управляющие сигналы, чтобы отключить все управляемые транзисторы для того, чтобы отключить все третьи транзисторы.

[0010] В еще одном аспекте подложка матрицы включает: некоторое число первых линий сканирования, некоторое число вторых линий сканирования, некоторое число линий данных, некоторое число пикселей и общий электрод для подвода общего напряжения, и каждый пиксель соответствует одной первой линии сканирования, одной второй линии сканирования и одной линии данных; каждый из пикселей включает первый электрод пикселя, второй электрод пикселя, третий электрод пикселя, первый транзистор, второй транзистор и третий транзистор, каждый из пикселей, кроме того, включает управляющую схему, первый электрод пикселя соединяется с соответствующей первой линией сканирования и соответствующей линией данных через первый транзистор, второй электрод пикселя соединяется с соответствующей первой линией сканирования и первым транзистором через второй транзистор, третий электрод пикселя соединяется с соответствующей второй линией сканирования и вторым электродом пикселя через третий транзистор, управляющая схема соединяется с соответствующими первыми линиями сканирования и соответствующим вторым электродом пикселя, управляющая схема действует на второй электрод пикселя, когда первые линии сканирования подводят сигналы сканирования, чтобы изменить напряжение второго электрода пикселя, и управляющая схема регулирует разницу напряжений между вторым электродом пикселя и общим электродом так, чтобы она не была равна нулю; в режиме двухмерного отображения первая линия сканирования подводит сигналы сканирования, чтобы включить первый транзистор и второй транзистор, на первый электрод пикселя поступают сигналы данных с линий данных через первый транзистор, чтобы находиться в состоянии отображения соответствующих двухмерных изображений, на второй электрод пикселя поступают сигналы данных с линий данных через первый транзистор и второй транзистор поочередно, чтобы быть в состоянии отображения соответствующих двухмерных изображений, управляющая схема действует на второй электрод пикселя, чтобы изменить напряжение второго электрода пикселя в первый раз, первые линии сканирования отключают первый транзистор и второй транзистор, вторые линии сканирования подводят сигналы сканирования, чтобы включить третий транзистор, так что второй электрод пикселя и третий электрод пикселя будут электрически соединены, на третий электрод пикселя поступают сигналы данных с второго электрода пикселя, чтобы быть в состоянии отображения соответствующих двухмерных изображений, так что напряжение второго электрода пикселя изменяется во второй раз третьим электродом пикселя, разница напряжений между любыми двумя из первого электрода пикселя, второго электрода пикселя и третьего электрода пикселя не равна нулю; и в режиме трехмерного отображения вторые линии сканирования отключают третий транзистор, первая линия сканирования подводит сигналы сканирования, чтобы включить первый транзистор и второй транзистор, на первый электрод пикселя поступают сигналы данных с линий данных через первый транзистор, чтобы быть в состоянии отображения соответствующих трехмерных изображений, на второй электрод пикселя поступают сигналы данных с линий данных через первый транзистор и второй транзистор поочередно, чтобы быть в состоянии отображения соответствующих трехмерных изображений, управляющая схема действует на второй электрод пикселя, чтобы изменить напряжение второго электрода пикселя, так что разница напряжений между первым электродом пикселя и вторым электродом пикселя не равна нулю, и третий электрод пикселя находится в состоянии отображения соответствующих черных изображений, когда третий транзистор отключен.

[0011] При этом управляющая схема включает четвертый транзистор и конденсатор перераспределения заряда, четвертый транзистор включает управляющий вывод, первый вывод и второй вывод, управляющий вывод четвертого транзистора соединяется с соответствующими первыми линиями сканирования пикселя, первый вывод четвертого транзистора соединяется с соответствующим вторым электродом пикселя, второй вывод четвертого транзистора соединяется с одним выводом конденсатора перераспределения заряда, конденсатор перераспределения заряда соединяется с общим электродом, первые линии сканирования подводят сигналы сканирования, чтобы включить четвертый транзистор, так что второй электрод пикселя и конденсатор перераспределения заряда будут электрически соединены, напряжение второго электрода пикселя изменяется в первый раз конденсатором перераспределения заряда, и четвертый транзистор регулирует разницу напряжений между вторым электродом пикселя и общим электродом так, чтобы она не была равна нулю.

[0012] При этом четвертым транзистором является тонкопленочный транзистор (TFT), управляющий вывод четвертого транзистора соответствует затвору TFT, первый вывод четвертого транзистора соответствует истоку TFT, второй вывод четвертого транзистора соответствует стоку TFT, и отношение ширина/длина TFT меньше заданного значения, так что разница напряжений между вторым электродом пикселя и общим электродом не равна нулю.

[0013] При этом некоторое число пикселей, некоторое число первых линий сканирования и некоторое число вторых линий сканирования расположены в направлении строки, в режиме двухмерного отображения соответствующие первые линии сканирования текущей строки пикселей и соответствующие вторые линии сканирования предыдущей строки пикселей сканируются одновременно, и предыдущая строка пикселей расположена рядом с текущей строкой пикселей и сканировалась недавно.

[0014] При этом подложка матрицы, кроме того, включает блок коммутации, расположенный на периферии подложки матрицы, и одну закорачивающую линию, блок коммутации включает некоторое число управляемых транзисторов, управляемый транзистор включает управляющий вывод, входной вывод и выходной вывод, входной вывод каждого из управляемых транзисторов соединяется с соответствующими первыми линиями сканирования строки пикселей, выходной вывод каждого из управляемых транзисторов соединяется с соответствующими вторыми линиями сканирования предыдущей строки пикселей, предыдущая строка пикселей расположена рядом с текущей строкой пикселей, и управляющие выводы управляемых транзисторов соединяются с закорачивающей линией; и в режиме двухмерного отображения закорачивающая линия подводит управляющие сигналы, чтобы включить все управляемые транзисторы, когда соответствующие первые линии сканирования одной строки пикселей подводят сигналы сканирования, эти сигналы сканирования одновременно подаются на вторые линии сканирования, соединенные с выходным выводом управляемого транзистора через управляемый транзистор, чтобы включить третий транзистор в режиме трехмерного отображения, и закорачивающая линия подводит управляющие сигналы, чтобы отключить все управляемые транзисторы для того, чтобы отключить все третьи транзисторы.

[0015] При этом размер области, в которой расположен третий электрод пикселя, меньше, чем размер областей, в которых расположены первый электрод пикселя и второй электрод пикселя.

[0016] При этом, когда вторые линии сканирования подводят сигналы сканирования, чтобы включить третий транзистор, третий транзистор регулирует разницу напряжений между вторым электродом пикселя и третьим электродом пикселя, чтобы она не была равна нулю когда третий транзистор включен, так что разница напряжений между любыми двумя из первого электрода пикселя, второго электрода пикселя и третьего электрода пикселя не равна нулю.

[0017] При этом третьим транзистором является TFT, затвор TFT соединяется с вторыми линиями сканирования, исток TFT соединяется с вторым электродом пикселя, сток TFT соединяется с третьим электродом пикселя, ширина/длина TFT меньше, чем второе заданное значение, так что разница напряжений между вторым электродом пикселя и третьим электродом пикселя не была равна нулю, когда третий транзистор включен.

[0018] В еще одном аспекте жидкокристаллическая панель включает: подложку матрицы, подложку фильтрации цвета и слой жидкого кристалла между подложкой матрицы и подложкой фильтрации цвета, подложка матрицы включает: некоторое число первых линий сканирования, некоторое число вторых линий сканирования, некоторое число линий данных, некоторое число пикселей и общий электрод для подвода общего напряжения, и каждый пиксель соответствует одной первой линии сканирования, одной второй линии сканирования и одной линии данных; каждый из пикселей включает первый электрод пикселя, второй электрод пикселя, третий электрод пикселя, первый транзистор, второй транзистор и третий транзистор, каждый из пикселей, кроме того, включает управляющую схему, первый электрод пикселя соединяется с соответствующей первой линией сканирования и соответствующей линией данных через первый транзистор, второй электрод пикселя соединяется с соответствующей первой линией сканирования и первым транзистором через второй транзистор, третий электрод пикселя соединяется с соответствующей второй линией сканирования и вторым электродом пикселя через третий транзистор, управляющая схема соединяется с соответствующими первыми линиями сканирования и соответствующим вторым электродом пикселя, управляющая схема действует на второй электрод пикселя, когда первые линии сканирования подводят сигналы сканирования, чтобы изменить напряжение второго электрода пикселя, и управляющая схема регулирует разницу напряжений между вторым электродом пикселя и общим электродом так, чтобы она не была равна нулю; в режиме двухмерного отображения первая линия сканирования подводит сигналы сканирования, чтобы включить первый транзистор и второй транзистор, на первый электрод пикселя поступают сигналы данных с линий данных через первый транзистор, чтобы находиться в состоянии отображения соответствующих двухмерных изображений, на второй электрод пикселя поступают сигналы данных с линий данных соответственно через первый транзистор и второй транзистор, чтобы быть в состоянии отображения соответствующих двухмерных изображений, управляющая схема действует на второй электрод пикселя, чтобы изменить напряжение второго электрода пикселя в первый раз, первые линии сканирования отключают первый транзистор и второй транзистор, вторые линии сканирования подводят сигналы сканирования, чтобы включить третий транзистор, так что второй электрод пикселя и третий электрод пикселя будут электрически соединены, на третий электрод пикселя поступают сигналы данных с второго электрода пикселя, чтобы быть в состоянии отображения соответствующих двухмерных изображений, так что напряжение второго электрода пикселя изменяется во второй раз третьим электродом пикселя, разница напряжений между любыми двумя из первого электрода пикселя, второго электрода пикселя и третьего электрода пикселя не равна нулю; и в режиме трехмерного отображения вторые линии сканирования отключают третий транзистор, первая линия сканирования подводит сигналы сканирования, чтобы включить первый транзистор и второй транзистор, на первый электрод пикселя поступают сигналы данных с линий данных через первый транзистор, чтобы быть в состоянии отображения соответствующих трехмерных изображений, на второй электрод пикселя поступают сигналы данных с линий данных через первый транзистор и второй транзистор поочередно, чтобы быть в состоянии отображения соответствующих трехмерных изображений, управляющая схема действует на второй электрод пикселя, чтобы изменить напряжение второго электрода пикселя, так что разница напряжений между первым электродом пикселя и вторым электродом пикселя не равна нулю, и третий электрод пикселя находится в состоянии отображения соответствующих черных изображений, когда третий транзистор отключен.

[0019] При этом управляющая схема включает четвертый транзистор и конденсатор перераспределения заряда, четвертый транзистор включает управляющий вывод, первый вывод и второй вывод, управляющий вывод четвертого транзистора соединяется с соответствующими первыми линиями сканирования пикселя, первый вывод четвертого транзистора соединяется с соответствующим вторым электродом пикселя, второй вывод четвертого транзистора соединяется с одним выводом конденсатора перераспределения заряда, конденсатор перераспределения заряда соединяется с общим электродом, первые линии сканирования подводят сигналы сканирования, чтобы включить четвертый транзистор, так что второй электрод пикселя и конденсатор перераспределения заряда будут электрически соединены, напряжение второго электрода пикселя изменяется в первый раз конденсатором перераспределения заряда, и четвертый транзистор регулирует разницу напряжений между вторым электродом пикселя и общим электродом так, чтобы она не была равна нулю.

[0020] При этом четвертым транзистором является тонкопленочный транзистор (TFT), управляющий вывод четвертого транзистора соответствует затвору TFT, первый вывод четвертого транзистора соответствует истоку TFT, второй вывод четвертого транзистора соответствует стоку TFT, отношение ширина/длина TFT меньше заданного значения, так что разница напряжений между вторым электродом пикселя и общим электродом не равна нулю.

[0021] При этом некоторое число пикселей, некоторое число первых линий сканирования и некоторое число вторых линий сканирования расположены в направлении строки, в режиме двухмерного отображения соответствующие первые линии сканирования текущей строки пикселей и соответствующие вторые линии сканирования предыдущей строки пикселей сканируются одновременно, и предыдущая строка пикселей расположена рядом с текущей строкой пикселей и сканировалась недавно.

[0022] При этом подложка матрицы, кроме того, включает блок коммутации, расположенный на периферии подложки матрицы, и одну закорачивающую линию, блок коммутации включает некоторое число управляемых транзисторов, управляемый транзистор включает управляющий вывод, входной вывод и выходной вывод, входной вывод каждого из управляемых транзисторов соединяется с соответствующими первыми линиями сканирования строки пикселей, выходной вывод каждого из управляемых транзисторов соединяется с соответствующими вторыми линиями сканирования предыдущей строки пикселей, предыдущая строка пикселей расположена рядом с текущей строкой пикселей, и управляющие выводы управляемых транзисторов соединяются с закорачивающей линией; в режиме двухмерного отображения закорачивающая линия подводит управляющие сигналы, чтобы включить все управляемые транзисторы, когда соответствующие первые линии сканирования одной строки пикселей подводят сигналы сканирования, эти сигналы сканирования одновременно подаются на вторые линии сканирования, соединенные с выходным выводом управляемого транзистора через управляемый транзистор, чтобы включить третий транзистор, в режиме трехмерного отображения закорачивающая линия подводит управляющие сигналы, чтобы отключить все управляемые транзисторы для того, чтобы отключить все третьи транзисторы.

[0023] При этом размер области, в которой расположен третий электрод пикселя меньше, чем размер областей, в которых расположены первый электрод пикселя и второй электрод пикселя.

[0024] При этом, когда вторые линии сканирования подводят сигналы сканирования, чтобы включить третий транзистор, третий транзистор регулирует разницу напряжений между вторым электродом пикселя и третьим электродом пикселя, чтобы она не была равна нулю, когда третий транзистор включен, так что разница напряжений между любыми двумя из первого электрода пикселя, второго электрода пикселя и третьего электрода пикселя не равна нулю.

[0025] При этом третьим транзистором является TFT, затвор TFT соединяется с вторыми линиями сканирования, исток TFT соединяется с вторым электродом пикселя, сток TFT соединяется с третьим электродом пикселя, ширина/длина TFT меньше, чем второе заданное значение, так что разница напряжений между вторым электродом пикселя и третьим электродом пикселя не равна нулю, когда третий транзистор включен.

[0026] В связи с вышеизложенным, каждый пиксель подложки матрицы включает первый электрод пикселя, второй электрод пикселя и третий электрод пикселя. Управляющая схема действует на второй электрод пикселя. Третий электрод пикселя соединяется с вторым электродом пикселя через третий транзистор. В режиме двухмерного отображения, когда первые линии сканирования подводят сигналы сканирования, на первый электрод пикселя поступают сигналы данных с линии данных через первый транзистор. На второй электрод пикселя поступают сигналы данных с линии данных через первый транзистор и второй транзистор поочередно, чтобы быть в состоянии отображения соответствующих двухмерных изображений. Управляющая схема действует на второй электрод пикселя, чтобы изменить напряжение второго электрода пикселя в первый раз, так что напряжение первого электрода пикселя отличается от напряжения второго электрода пикселя. Таким образом уменьшается искажение цвета при широком угле обзора. Когда первые линии сканирования прекращают подводить сигналы сканирования, третий транзистор включается, так что второй электрод пикселя и третий электрод пикселя будут электрически соединены. На третий электрод пикселя поступают сигналы данных с второго электрода пикселя, чтобы быть в состоянии отображения соответствующих двухмерных изображений. Как таковые, в режиме двухмерного отображения первый, второй и третий электрод пикселя находятся в состоянии отображения соответствующих двухмерных изображений. Таким образом увеличивается формат изображения. Помимо этого напряжение второго электрода пикселя изменяется во второй раз третьим электродом пикселя, так что напряжение любых двух из трех электродов пикселя разное. В то же время, разница напряжений между вторым электродом пикселя и первым электродом пикселя увеличивается, что далее уменьшает искажение цвета при широком угле обзора. В режиме трехмерного отображения на первый электрод пикселя поступают сигналы данных с линий данных через первый транзистор. На второй электрод пикселя поступают сигналы данных с линий данных через первый и второй транзистор поочередно, чтобы быть в состоянии отображения соответствующих трехмерных изображений. Управляющая схема действует на второй электрод пикселя, чтобы изменить напряжение второго электрода пикселя, так что напряжение первого электрода пикселя отличается от напряжения второго электрода пикселя, чтобы уменьшить искажение цвета при широком угле обзора. Помимо этого в режиме трехмерного отображения третий электрод пикселя является управляемым, чтобы быть в состоянии отображения соответствующих черных изображений, чтобы уменьшить эффект перекрестных помех.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

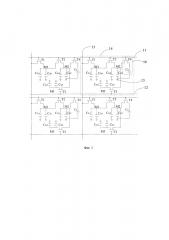

[0027] Фиг. 1 - схематический вид подложки матрицы в соответствии с одним вариантом осуществления.

[0028] Фиг. 2 - схематический вид, показывающий один пиксель с Фиг. 1

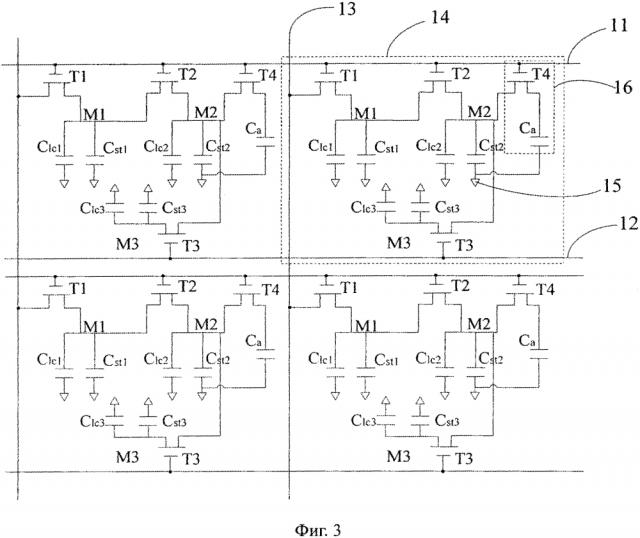

[0029] Фиг. 3 - эквивалентная схема пикселя с Фиг. 1

[0030] Фиг. 4 - схематический вид, показывающий действие третьего электрода пикселя с Фиг. 1 на изображение в режиме трехмерного отображения.

[0031] Фиг. 5 - эквивалентная схема пикселя в соответствии с еще одним вариантом осуществления.

[0032] Фиг. 6 - схематический вид жидкокристаллической панели в соответствии с одним вариантом осуществления.

ПОДРОБНОЕ ОПИСАНИЕ ВАРИАНТОВ ОСУЩЕСТВЛЕНИЯ

[0033] Варианты осуществления изобретения теперь будут описаны более подробно со ссылками на прилагаемые чертежи, на которых показаны эти варианты осуществления.

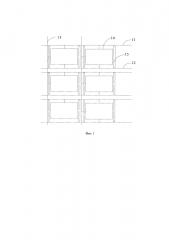

[0034] На Фиг. 1 показан схематический вид подложки матрицы в соответствии с одним вариантом осуществления. Подложка матрицы включает некоторое число первых линий 11 сканирования, некоторое число вторых линий 12 сканирования, некоторое число линий 13 данных, некоторое число пикселей 14 и общий электрод 15 для подвода общего напряжения. Пиксели 14 расположены в матрице. Каждый пиксель 14 соединяется с одной первой линией 11 сканирования, одной второй линией 12 сканирования и одной линией 13 данных.

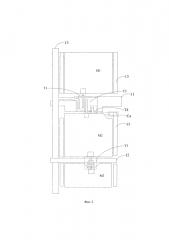

[0035] Со ссылкой на Фиг. 2 и 3, каждый из пикселей 14 включает первый электрод M1 пикселя, второй электрод М2 пикселя, третий электрод М3 пикселя, и первый транзистор Т1, второй транзистор Т2, третий транзистор Т3, соответствующие, соответственно, первому электроду М1 пикселя, второму электроду М2 пикселя и третьему электроду М3 пикселя. Каждый из транзисторов включает управляющий вывод, входной вывод и выходной вывод. Управляющие выводы первого транзистора Т1 и второго транзистора Т2 электрически соединяются с соответствующей первой линией сканирования 11 пикселя 14. Входной вывод первого транзистора Т1 электрически соединяется с соответствующей линией 13 данных пикселя 14. Выходной вывод первого транзистора Т1 электрически соединяется с первым электродом M1 пикселя. Входной вывод второго транзистора Т2 электрически соединяется с первым электродом M1 пикселя. Входной вывод второго транзистора Т2 электрически соединяется с выходным выводом первого транзистора Т1. Выходной вывод второго транзистора Т2 электрически соединяется с вторым электродом пикселя М2. Управляющий вывод третьего транзистора Т3 электрически соединяется с соответствующей второй линией 12 сканирования пикселя 14. Входной вывод третьего транзистора Т3 электрически соединяется с вторым электродом пикселя М2. Выходной вывод третьего транзистора Т3 электрически соединяется с третьим электродом пикселя М3.

[0036] В одном варианте осуществления первым транзистором Т1, вторым транзистором Т2 и третьим транзистором Т3 являются тонкопленочные транзисторы (TFT). Управляющие выводы транзисторов T1, Т2, Т3 соответствуют затвору TFT. Входные выводы транзисторов T1, Т2, Т3 соответствуют истоку TFT. Выходные выводы транзисторов Т1, Т2, Т3 соответствуют стоку TFT. В других вариантах осуществления этими тремя транзисторами могут быть триоды или пары Дарлингтона.

[0037] Каждый пиксель 14 включает управляющую схему 16, соединяющуюся с соответствующей первой линией 11 сканирования и вторым электродом М2 пикселя 14. Когда первая линия 11 сканирования подводит сигналы сканирования, управляющая схема 16 изменяет напряжение второго электрода М2 пикселя и регулирует разницу напряжений между вторым электродом М2 пикселя и общим электродом 15 так, чтобы она не была равна нулю. Более конкретно, управляющая схема 16 включает четвертый транзистор Т4 и конденсатор перераспределения заряда Са. Четвертый транзистор Т4 включает управляющий вывод, входной вывод и выходной вывод. Управляющий вывод четвертого транзистора Т4 электрически соединяется с первой линией 11 сканирования. Первый вывод четвертого транзистора Т4 электрически соединяется с вторым электродом пикселя М2. Второй вывод четвертого транзистора Т4 электрически соединяется с одним выводом конденсатора перераспределения заряда Ca, и другой вывод конденсатора перераспределения заряда Ca электрически соединяется с общим электродом 15. Четвертым транзистором Т4 является TFT. Управляющий вывод четвертого транзистора Т4 соответствует затвору TFT. Первый вывод четвертого транзистора Т4 соответствует истоку TFT. Второй вывод четвертого транзистора Т4 соответствует стоку TFT. Когда четвертый транзистор Т4 отключается сигналами сканирования с первой линии 11 сканирования, второй электрод М2 пикселя и конденсатор перераспределения заряда Ca электрически соединяются. Напряжение второго электрода М2 пикселя изменяется потому, что заряды перераспределяются между вторым электродом М2 пикселя и конденсатором перераспределения заряда Ca. Помимо этого разница напряжений между вторым электродом М2 пикселя и общим электродом 15 не равна нулю, когда четвертый транзистор Т4 включен. Как таковой, второй электрод М2 пикселя находится в нормальном состоянии отображения изображений.

[0038] Подложка матрицы может уменьшать разницу в цвете в режимах двухмерного и трехмерного отображения, когда угол обзора большой. Помимо этого подложка матрицы не только может увеличивать формат изображения в режиме двухмерного отображения, но и может уменьшать влияние перекрестных помех в режиме трехмерного отображения.

[0039] Более конкретно, в режиме двухмерного отображения первые линии 11 сканирования и вторые линии 12 сканирования сканируются построчно. Общий электрод 15 подводит общее напряжение. При обращении положительной полярности, то есть, когда сигналы данных больше чем общее напряжение, первая линия 11 сканирования подводит сигналы сканирования высокого уровня, чтобы включить первый транзистор Т1 и второй транзистор Т2. Линия данных 13 подводит сигналы данных. На первый электрод M1 пикселя поступают сигналы данных с линии данных 13 через первый транзистор Т1, чтобы находиться в состоянии отображения соответствующих двухмерных изображений. На второй электрод М2 пикселя поступают сигналы данных через первый транзистор Т1 и второй транзистор Т2 поочередно, чтобы быть в состоянии отображения соответствующих двухмерных изображений. В этот момент напряжение второго электрода М2 пикселя немного ниже чем напряжение первого электрода пикселя M1 из-за сопротивления первого транзистора Т1 и второго транзистора Т2. Как таковое, напряжение первого электрода пикселя M1 отличается от напряжения второго электрода пикселя М2. Когда первая линия 11 сканирования подводит сигналы сканирования высокого уровня, четвертый транзистор Т4 включается в ответ на прием сигналов сканирования, так что второй электрод М2 пикселя и конденсатор перераспределения заряда Ca электрически соединяются. Напряжение второго электрода М2 пикселя изменяется в первый раз конденсатором перераспределения заряда Ca. То есть второй электрод М2 пикселя разряжается конденсатором перераспределения заряда Ca. Таким образом, напряжение второго электрода М2 пикселя снижается еще б