Стабилизатор постоянного тока

Иллюстрации

Показать всеРеферат

262I9I

ОПИСАНИЕ

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Республик

Зависимое от авт. свидетельства №

Заявлено 24.XI I.1968 (№ 1293279/26-9) с присоединением заявки №

Приоритет

Опубликовано 26.1.1970. Бюллетень № 6

Дата опубликования описания 21 V.1970

Кл. 21а4, 35/14

МПК H 02m

УДК 621.316.722,1(088.8) Комитет по делам изобретений и открытий при Совете Министров

СССР

Автор изобретения

А. И. Ямпольский

Заявитель

СТАБИЛИЗАТОР ПОСТОЯННОГО ТОКА

Изобретение относится к области источников питания для радиоаппаратуры, а именно к стабилизаторам постоянного тока.

Известные стабилизаторы постоянного тока, содержащие регулирующий каскад, схему сравнения и источник опорного напряжения, не позволяют получить достаточно высокого коэффициента стабилизации, а длительность переходного процесса в них велика.

Цель изобретения — разработка стабилизатора постоянного тока, обладающего высоким коэффициентом стабилизации и малой длительностью переходного процесса.

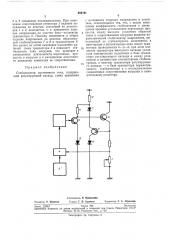

Для этого между выходом усилителя обратной связи стабилизатора и сопротивлением нагрузки включен дополнительный параметрический стабилизатор напряжения, выполненный на стабилитронах, включенных в эмиттерную и коллекторную цепи своего транзистора проводимости и — р — и, при этом коллектор транзистора выходного каскада усилителя одновременно подключен к базе транзистора регулирующего каскада и между резистором и упомянутым коллекторным стабилитроном, а эмиттер транзистора регулирующего каскада — к базе транзистора параметрического стабилизатора и к последовательно соединенным сопротивлению нагрузки и измерительному резистору, На чертеже дана схема предлагаемого стабилизатора постоянного тока.

Резистор 1 является сопротивлением нагрузки стабилизатора, содержащего измерительный резистор 2, источник 8 опорного напряжения, схему 4 сравнения т предварительный усилитель 5, Между выходом усилителя обратной связи, выполненным на транзисторе 6, и резистором

1р 1 включен параметрический стабилизатор напряжения, выполненный на стабилитронах 7 и 8, включенных в эмиттерную и коллекторную цепи транзистора 9 проводимости п — р — n.

Коллектор транзистора 6 электрически связан

15 с базой транзистора 10 регулирующего каскада и с резисторами 11 и 12, точка соединения которых подключена к стабилитрону 7. Эмиттер транзистора 10 соединен с базой транзистора 9 и резисторами 1 и 2, а эмиттер тран2р зистора 6 подключен к стабилитрону 18.

Стабилизатор работает следующим образом.

Ток основной цепи, протекающий через резистор 1, создает на резисторе 2 падение напряжения, пропорциональное величине тока.

Это напряжение схемой 4 сравнивается с напряжением источника 8, и разностный сигнал, усиленный уси: телем б и транзистором 6, подается на транзистор 10. Для увеличения

30 стабильности тока в цепи нагрузки резисторы

26219i

Предмет изобретения

Составитель 9. Фрндолин»

Редактор Т. Иванова Техред Т. П. Курнлко Корректор T А. Абрамова

Заказ 1269(7 Тираж 500 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, Ж-35, Раушская наб., д. 4/5

Типография, пр. Сапунова, 2

1 и 2 соединены последовательно. При изменении сопротивления резистора 1 падение напряжения на цепочке, состоящей из резисторов 1 и 2, изменяется, т. е. изменяется падение напряжения на участке база †коллект транзистора 9. Поэтому изменяется и общее падение напряжения на цепочке, образованной стабилитронами 7 и 8 и транзистором 9.

Это влечет за собой изменение положения рабочей точки транзистора 6 и повышает стабильность тока нагрузки, что приводит к уменьшению длительности переходных процессов в нагрузке и к расширению допустимого диапазона изменения ее сопротивления.

Стабилизатор постоянного тока, содержащий регулирующий каскад, схему сравнения с источником опорного напряжения и усилитель, отличающийся тем, что, с целью повышения коэффициента стабилизации и умень щения времени установления переходных процессов, между выходом усилителя обратной связи и сопротивлением нагрузки включен параметрический стабилизатор напряжения, выполненный на стабилитронах, включенных в эмиттерную и коллекторную цепи своего транзистора проводимости п — р — и, при этом коллектор транзистора выходного каскада усилителя одновременно подключен к базе транзистора регулирующего каскада и между резистором и упомянутым коллекторным стабилитроном, а эмиттер транзистора регулирующего каскада — к базе транзистора параметрического стабилизатора и к последовательно соединенным сопротивлению нагрузки и измерительному резистору.