Распределитель импульсов

Иллюстрации

Показать всеРеферат

ОП ИСАНИЕ

ИЗОБРЕТЕН ИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Свез Соевтскиз

Социалистическиз

Республик

Зависимое от авт. свидетельства №

Заявлено 12.V11.1968 (¹ 1255195/18-24) с присоединением заявки ¹

П риоритет

Опубликовано 26.1.1970, Бюллетень № 6

Дата опубликования описания 8Х.1970

Кл. 42mа 1104

Хомитвт по делам изобретений и открытий при Совета Министров

СССР

МПК G 061

УДК 681.325.67(088.8) - - ;1

1

Б. М. Власов, Л. Л. Телепнев, В. В. Маслов и Л. В. Епифанова -. ",,-.Л

Авторы изобретения

Заявитель

РАСПРЕДЕЛИТЕЛЬ ИМПУЛЬСОВ

Изобретение относится к области вычислительной техники.

Распределители импульсов, содержащие регистры сдвига на потенциальных триггерах, коммутирующие и вспомогательные триггеры и логические элементы «И», известны.

Предложенный распределитель отличается от из,вестных тем, что в нем,пер вый канал так1овой частоты подключен к входам элементов

«И», управляющих выработкой нечетных импульсов распределителя, а второй канал тактовой частоты соединен с входами элементов

«И», управляющих .выработкой четных импульсов. При этом вторые входы элементов

«И» соединены с нулевым и единичным входами коммутирующего триггера соответственно, а выходная шина i-ого импульса раопределителя подключена к единичному входу триггера старшего разряда и к нулевому входу триггера младшего разряда.

Это упрощает схему распределителя импульсов.

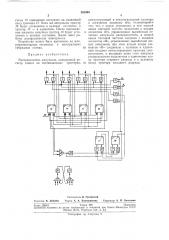

Функциональная схема описываемого ра"пределителя,приведена на чертеже. Схема содержит логические элементы «И» 1 — 12, статические триггеры 18 — 18, логические элементы 19 — 22 «И», логические элементы 23 — 25

«НЕ» и логические элементы 2б — 28 «ИЛИ» (схемы сборки). Соединение элементов 24, 25, 37 и 28 образует схему триггера.

В исходном состоянии все триггеры распределителя установлены в нулевое состояние.

Перед началом работы по шине 29 на единичный вход триггера 18 поступает импульс запуска распределителя импульсов. Им пульс запуска синхронизируется по времени канала тактовой частоты. Импульс тактовой частоты первого канала через открытые схемы 9 и 1 совпадения поступает в шину, первого импуль10 са распределителя и устанавливает триггер 14 (триггер старшего разряда) в единичное состояние. Импульс тактовой частоты второго канала через открытые схемы 10 и 8 совпадения поступит в выходную шину второго импульса распределителя и одновременно установит в единичное состояние триггер 15, а триггер 18 — в нулевое состояние. Аналогично вырабатываются третий и четвертый импульсы. Импульс с выхода схемы 7 совпадения установит триггер 15 в нулевое состояние, а триггеры 18 .и 17 — в единичное состояние.

После истечения времени, равного длительности импульса с выхода схемы 7 совпадения, триггер 18 также будет установлен в единичное состояние. Схемы 9 и 10 совпадения будут закрыты, а 11 и 12 — открыты. Получение следу.ющих импульсов производится аналогично рассмотренному.

Восьмой импульс, распределителя с выхода

Зо схемы 8 совпадения через схему 2б сборки и

262490

Предмет изобретения

Составитель Д. Гречинский

Редактор В. Дибобес Техред А. А. Камышникова Корректор А. П, Васильева

Заказ 1064/4 Тираж 500 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва К-35, Раушская наб., д. 4 5

Типография, пр. Сапунова, 2 схему 19 совпадения поступает на единичный вход триггера 17. Этим же импульсом триггер

15 будет установлен в нулевое состояние, а триггер 18 — в единичное. После прохождения восьмого импульса триггер 18 будет установлен в нулевое состояние. Далее цикл работы распределителя повторяется.

Устройство может быть выполнено на микромиHHBTIojpHbIx элементах и интегральных гибридных схемах.

Распределитель импульсов, содер>кащий регистр сдвига на потенциальных триггерах, коммутирующий и вспомогательный триггеры и логические элементы «И», отличающийся тем, что, с целью у прощения, в нем первый канал тактовой частоты подключен к входам

5 элементов «И», управляющих выработкой нечетных импульсов распределителя, а второй канал тактовой частоты соединен с входами элементов «И», управляющих выработкой четных импульсов, при этом вторые входы эле10 ментов «И» соединены с нулевым и единичным входами коммутирующего триггера соответственно, а выходная шина 1-ого импульса раопределителя подключена к единичному âõîду триггера старшего разряда и к нулевому

15 входу тр ипге р а младшего р аз ряда.