Преобразовате.ль интервалов времени в цифровой код•'*'/baf;; t, '~'-'~f>&- '^- j •.:•••; *.х5таг.^^

Иллюстрации

Показать всеРеферат

О П И С А Н И Е 2625I4

ИЗОБРЕТЕНИЯ

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Союз Советских

Социалистических

Реслублик

Зависимое от авт. свидетельства ч0

Заявлено 01.Ч11.1968 (№ 1254931/18-24) Кл. 42m«, 3/00 с присоединением заявки №

MHK G 06j / омитет AO делам

Приоритет

Опубликовано 26.1.1970. Бюллетень ¹ 6

Дата опубликования описания 2,XI.1970 изобретений и открытий лри Совете Министров

СССР

УД К 681.355 (088.8) . «

В. М. Беляков, Ю. Б. Блинков, Е. А. Ломтев и В. M. Шлянд

Авторы изобретения

С "«Г",, «

П,-- т т - - т «-т

Пензенский политехнический институт

Заявитель йк«".т/1.« :, «и

ПРЕОБРАЗОВАТЕЛЬ ИНТЕРВАЛОВ ВРЕМЕНИ

В ЦИФРОВОЙ КОД

Изобретение относится к области преобразования и кодирования информации.

Известны преобразователи интервалов времени в цифровой код, содержащие формирующие триггеры, схему сборки, регистры памяти разрядов и линию задержки с отводами, причем выходы линий задержки подключены ко входам схемы сборки, выход схемы сборки соединен с первым входом формирующего триггера, второй вход которого соединен с последним выходом линии задержки, входы регистров памяти разрядов подключены к выходам линий задержки.

В известных преобразователях количество оборудования зависит от числа разрядов.

Предложенный преобразователь интервалов времени в цифровой код отличается тем, что, с целью упрощения, он содержит схемы совпадений, расширитель импульсов, сдвигающий регистр, причем вход .пинии задержки соединен со входом сдвигающего регистра и с выходом схемы совпадений, вход схемы совпадений подключен к выходу формирутощего триггера, один вход которого соединен с клеммой «сброс», а другой со входом линии задержки, разрешающие входы регистров памяти разрядов соединены с первыми входами схем совпадения разрядов, выходы схемы совпадений разрядов соединены с выходом формирующего триггера схемы сборки, вторые входы схем совпадений разрядов соединены с выходами сдвигающего регистра, а вход формирующего триггера схемы сборки соединен сА входом расширителя импульсов, выход которого подключен к первому входу схемы совпадений, второй вход схемы совпадений соединен с последним выходом сдвигающего регистра, выход схемы совпадентгй подключен ко входу линии задержки. Это упрощает преобт0 разователь, так как количество оборудования с ростом числа разрядов увеличивается незначительно.

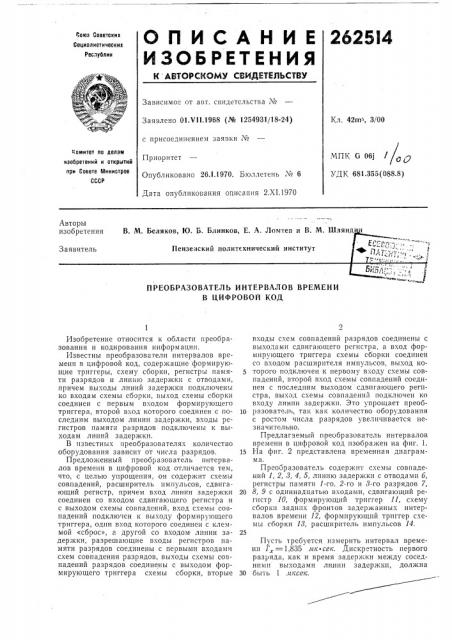

Предлагаемый преобразователь интервалов времени в цифровой код изображен на фиг. 1.

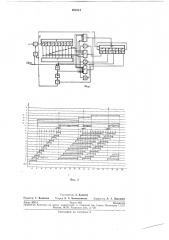

15 На фиг. 2 представлена временная диаграмма.

Преобразователь содержит схемы совпадений 1, 2, 8, 4, 5, линию задержки с отводамп б, регистры памяти 1-го, 2-го и 3-ro разрядов 7, 20 8, 9 с одиннадцатью входами, сдвигающий регистр 10, формирующий триггер 11, схему сборки задних фронпов задержанных интервалов времени 12, формирующий триггер схемы сборки 18, расширитель импульсов 14.

Пусть требуется измерить интервал времени Т =1,835 як сек. Дискретность первого разряда, как и время задержки между соседними выходами линии задержки, должна

30 быть 1 иксек.

262514

Перед измерением схема возвращается в исходное состояние импульсом «сброс». Регистр 10 на фпг. 1 находится в исходном состоянии.

Так как схема совпадений 1 открыта после

«сброса» триггером 11 по одному входу, то измеряемый интервал Т», приходя на второй вход схемы совпадений 1, поступает на вход регистра 10, на вход формирующего триггера

11 и на вход линии задержки. Сдвигающий регистр 10 устанавливается задним фронтом интервала Т„таким образом, что схемы совпадений 2 и 5 открываются по одному входу.

Формирующий триггер 11, запущенный задним фронтом интервала Т» по первому входу, закрывает схему совпадений 1 до следующего «сброса», так как время измерения преобразователя больше измеряемого интервала времени.

В линии задержки б интервал Т» многократно задерживается. Передним фронтом задержанного интервала Т» с последнего выхода линии задержки (0 на схеме) запускается формирующий триггер схемы сборки 18, который возвращается в исходное состояние следующим непосредственно за ним задним фронтом со схемы сборки. Очевидно, что в данном случае триггер 11 будет возвращен в исходное состояние задним фронтом, пришедшим на схему сборки с выхода 1 . Число, которое должно быть записано в данном разряде отсчета, должно соответствовать номеру выхода линии задержки, с которого приходит задний фронт, возвращающий в исходное состояние триггер 18 через схему сборки. В данном случае в регистр памяти первого разряда

7 должна быть записана 1. Это получается так: интервал At<, формируемый на выходе триггера 18, подается на входы схем совпадения 2, 3, 4 и через них на разрешающие входы регистров памяти 7, 8, 9. Разрешение записи производится в момент заднего фронта интервала At>, который по времени совпадает с задним фронтом интервала, формирующего этот. задний фронт. Запись информации в регистр памяти производитсл задними фронтами задержанных интервалов. В нашем случае в первом разряде окажется записанной единица, так как с регистра 10 открыта по одному входу схема совпадений 2 и разрешающее напряжение поступит только на регистр памяти 7, а в момент подачи разрешающего напряжения на регистр памяти на первом входе его будет задний фронт задержанного интервала с выхода 1.

Интервал Л1,, выделенный на выходе триггера 13 равен: Ы,=҄— t i. где tg — дискрегность первого разряда, . р — число, записанное в первом разряде, At> — — 1,835 лксек—

1 лксек=0,835 мксек.

Интервал М для оценки второго разряда той же линией задержки растягивается расширителем импульсов 14 в десять раз, а интервал

10 М, через схему совпадений 5, уже открытую по одному входу с регистра 10, поступает на вход сдвигающего регистра 10, где единица из ячейки 1" переписывается в ячейку 2", закрывается сх ма совпадений 2 и открывается схема совпадений 8 попадает на вход линии задержки б, где происходят процессы, аналогичные процессам при оценке первого разряда, только информация заносится в регистр памяти второго разряда 8, а интервал

At>, выделенный на выходе триггера 13 и растянутый в десять раз, подается для оценки третьего разряда. Во втором разряде будет записано число 8, в третьем — число три.

После оценки трех разрядов интервал At>, растянутый в 10 раз, для измерения не используется, а его задний фронт переписывает единицу из ячейки 3" регистра в ячейку

4", что закрывает схему совпадений 5 и ripeкращает процессы выделения интервалов At, которые могут помешать при новом измерении.

Для увеличения разрешающей способности схемы триггер 13 имеет устройство, предотвращающее неправильное срабатывание его в случае одновременного прохождения импульсов на обеих входах.

Предмет изобретения

Преобразователь интервалов времени в цифровой код, содержащий формирующие триггеры, схему сборки, регистры памяти разрядов и линию задержки с отводами, причем выходы линий задержки подключены ко входам схемы сборки, выход схемы сборки соединен с первым входом формирующего триггера, второй вход которого соединен с последним выходом линии задержки, входы регистров памяти разрядов подключены к выходам линий задержки, отличсиощийся тем, что, с целью упрощения, он содержит схемы совпадений, расширитель импульсов, сдвигающий регистр, причем вход линии задержки соединен со входом сдвигающего регистра и с выходом схемы совпадений, вход схемы совпадений подключен к выходу формирующего триггера, один вход которого соединен с клеммой

«сброс», а другой — со входом линии задержки, разрешающие входы регистров памяти разрядов соединены с первыми входами схем совпадений разрядов, выходы схем совпадений разрядов соединены с выходом формирующего триггера схемы сборки, вторые входы схем совпадений разрядов соединены с выходами сдвигающего регистра, а вход формирующего триггера схемы сборки соединен со входом расширителя импульсов, выход которого подключен к первому входу схемы совпадений, второй вход схемы совпадений соединен с последним выходом сдвигающего регистра выход схемы совпадений подключен ко входу линии задержки.

262514 бба."с б г и б б п !2 i ж э гб гг г; гб 28 . д гг з jб зб

Фиг. 2

Составитель 3. Дунаева

Редактор f. Яковлева Текред А. А. Камьншникова Корректор Л. А. Царькова

Заказ 3091 4 Тирани 480 Подписное

ЦНИИПИ Комитета по делам изобретений и открьпий прп Совете Министров СССР

Москва, Ж-35, Раушская нао., д. 4/5

Типография, пр. Сапунова, 2