Демодулятор псевдослучайных сигналов с относительной фазовой модуляцией

Иллюстрации

Показать всеИзобретение относится к технике связи и может быть применено для приема дискретных сигналов с относительной фазовой модуляцией в системах с расширенным спектром, с псевдослучайными сигналами в условиях преднамеренных помех. Техническим результатом изобретения является повышение помехоустойчивости приема псевдослучайных сигналов в условиях преднамеренных помех. Демодулятор псевдослучайных сигналов с относительной фазовой модуляций содержит перемножитель, генератор псевдослучайной последовательности, блок синхронизации, фазовращатель, второй, третий, четвертый, пятый шестой, седьмой, восьмой перемножители, два интегратора, два суммирующих накопителя , четыре элемента задержки, автономный генератор, три инвертора, семь сумматоров, блок выбора максимального сигнала, решающий блок. 2 ил.

Реферат

Изобретение относится к технике связи и может быть применено для приема дискретных сигналов с относительной фазовой модуляцией в системах с расширенным спектром (с псевдослучайными сигналами) в условиях преднамеренных помех.

Известны демодулятор сигналов с фазовой модуляцией (А.С. 720782, МКИ H04L 27/22, 1980), демодулятор сигналов относительной фазовой модуляции (Патент 2037969, МКИ H04L 27/22, 1995), способ демодуляции сигналов с относительной фазовой модуляцией и устройство для его осуществления (Патент 2099892, МКИ H04L 27/22, 1997), способ демодуляции сигналов с относительной фазовой манипуляцией и устройство для его реализации (Патент 2168869, МКИ H04L 27/22, 2001), демодулятор сигналов с относительной фазовой модуляцией (Патент 2460225, МПК 27/22, 2012).

Данные технические решения, обладая определенной помехоустойчивостью в условиях естественных помех в канале связи, при воздействии преднамеренных помех, по структуре совпадающих со структурой сигнала, но по мощности его превосходящих, будут неработоспособны. Это следует, в частности, из положений, доказанных в работе Агафонова Α.Α., Ложкина К.Ю., Поддубного В.Н. Методология и результаты синтеза и оценки преднамеренных помех приемникам дискретных сигналов // Радиотехника и электроника. 2003. Т. 48. №8. С. 956-962. Здесь сказано, что оптимальная помеха приемникам фазоманипулированных сигналов представляет собой также фазоманипулированное колебание, несущая частота и длительность посылок которого совпадают с соответствующими параметрами сигнала. При этом совпадают тактовые моменты смены фаз и сигнала и помехи. Если сигнал и помеха окажутся в противофазе, то при воздействии более мощной помехи демодулятор (приемник) зарегистрирует ее вместо сигнала.

Для защиты от воздействия такого рода преднамеренных помех в технике связи применяют системы с расширенным спектром на основе псевдослучайных (шумоподобных) сигналов (см. Л.Е. Варакин. Системы с шумоподобными сигналами. - М: Радио и связь, 1985. - 384 с.; Б. Скляр. Цифровая связь. - М.: Издательский дом «Вильямс», 2007. - 1104 с.; В.П. Ипатов. Широкополосные системы и кодовое разделение сигналов. Принципы и приложения. - М.: Техносфера, 2007. - 488 с.; В.И. Борисов, В.М. Зинчук, А.Е. Лимарев, В.И. Шестопалов. Помехозащищенность систем радиосвязи с расширением спектра прямой модуляцией псевдослучайной последовательностью. Под ред. В.И. Борисова. Изд. 2-е перераб. и доп. - М.: Радио Софт, 2011. - 550 с.; А. Голдсмит. Беспроводные коммуникации. - М.: Техносфера, 2011. - 904 с.).

Обработка в демодуляторе (приемнике) смеси псевдослучайных сигналов и преднамеренной помехи приводит к «обелению» последней. Иными словами, помеха становится подобной естественному шуму, методы защиты от которого хорошо известны и весьма эффективны.

Наиболее близким по технической сущности к предлагаемому устройству является приемник (демодулятор) последовательного составного сигнала с однократной фазоразностной модуляцией - ФРМ (см. Ю.Б. Окунев, Л.А. Яковлев. Широкополосные системы связи с составными сигналами. - М.: «Связь», 1968, с. 68, рис. 3.17).

Данный приемник состоит из первого перемножителя с подключенным к нему генератором псевдослучайной последовательности (ПСП) с блоком синхронизации, двух параллельных ветвей (трактов) квадратурного приема с общим входом, содержащих последовательно соединенные вторые перемножители, интеграторы, третьи перемножители с подключенными к их вторым входам элементами задержки на длительность посылки сигнала, а также автономный генератор опорного сигнала, соединенный со вторым перемножителем одной из ветвей непосредственно, а со вторым перемножителем другой ветви - через фазовращатель на π/2.

Этот демодулятор (приемник) реализует обработку псевдослучайного сигнала с относительной фазовой модуляцией (ОФМ)

где γk=(0,1) - элементы ПСП, φс - случайная начальная фаза сигнала, Uc - амплитуда элемента сигнала, T0 - длительность элемента сигнала, n - число элементов составного псевдослучайного сигнала.

Сигнал S0(t) соответствует посылке «0», S1(t) - посылке «1». Представленные соотношения являются новой уточненной редакцией соотношения для составного сигнала с относительной фазовой модуляцией из книги Ю.Б. Окунева, Л.А. Яковлева, с. 15-16, упомянутой выше.

Процедура обработки и регистрации такого составного псевдослучайного сигнала осуществляется на основе сравнения двух его соседних посылок - текущей и предшествующей в соответствии с известным правилом относительной фазовой модуляции, изложенном в книге: Н.Т. Петрович. Передача дискретной информации в каналах с фазовой манипуляцией. - М.: Сов. Радио, 1965. - 262 с. Для этого в составе каждой из двух ветвей приемника имеются элементы задержки на время длительности одной посылки сигнала T=nT0.

Помехоустойчивость этого приемника оценивалась в работе: P.P. Биккенин, А.Л. Фролов. Оценка эффективности некогерентного приема шумоподобных сигналов в условиях помех // Радиоэлектроника и связь, 1992, №2-3. С. 24-29, при помощи соотношения для вероятности ошибочного приема

где - интеграл вероятностей, q=Pc/Pn - отношение мощности элемента сигнала к мощности преднамеренной помехи; n - число элементов псевдослучайного сигнала (база сигнала).

Такой приемник обладает определенной помехоустойчивостью в условиях преднамеренных помех. Однако, когда помеха превосходит сигнал по мощности q=Pс/Pn<1, помехоустойчивость приемника оказывается недостаточной.

Цель изобретения - повышение помехоустойчивости приема псевдослучайных сигналов в условиях преднамеренных помех.

Данная задача повышения помехоустойчивости может быть решена путем увеличения энергии, накопленной до момента регистрации сигнала. Это можно сделать, увеличив размерность обрабатываемого отрезка сигнала (удлинить интервал сигнала) с двух до трех его посылок, последовательно во времени поступающих в приемник (см. Divsalar D., Simon М.К. Multiple - simbol differential detection of MPSK // IEEE Trans. Commun., 1990, №3. C. 300-308).

Для достижения поставленной цели в известный приемник (демодулятор) составного сигнала с фазоразностной (относительной) фазовой модуляцией, состоящий из первого перемножителя с подключенным к нему генератором псевдослучайной последовательности с блоком синхронизации, двух параллельных ветвей квадратурного приема с общим входом, содержащих последовательно соединенные вторые перемножители, интеграторы, третьи перемножители с подключенными к их вторым входам элементами задержки на длительность посылки сигнала, а также автономный генератор опорного сигнала, соединенный со вторым перемножителем одной из ветвей непосредственно, а со вторым перемножителем другой ветви через фазовращатель на π/2, введены в каждую из квадратурных ветвей суммирующие накопители, включенные между выходами интеграторов и входами первых элементов задержки и соединенные по выходу с первыми входами третьих перемножителей, а также вторые элементы задержки и четвертые перемножители, причем вторые элементы задержки включены между выходами первых элементов задержки и вторыми входами четвертых перемножителей, первые входы которых подключены к выходам первых элементов задержки, а выходы, являющиеся вторыми выходами каждой из двух параллельных ветвей квадратурного приема, подключены к первому и второму входам второго сумматора, выход которого соединен с входами четвертого и шестого сумматоров непосредственно, а со вторыми входами пятого и седьмого сумматоров через второй инвертор, кроме того, соединенные с выходами суммирующих накопителей пятые перемножители, вторые входы которых подключены к выходам вторых элементов задержки, а выходы, являющиеся третьими выходами каждой из двух параллельных ветвей квадратурного приема, соединены с первым и вторым входами третьего сумматора, выход которого подключен к третьим входам четвертого и пятого сумматоров непосредственно, а к третьим входам шестого и седьмого сумматоров через третий инвертор, дополнительно выходы третьих перемножителей, являющиеся первыми выходами каждой из двух параллельных ветвей квадратурного приема, соединены с первыми и вторыми входами первого сумматора, выход которого подключен к первым входам четвертого и седьмого сумматоров непосредственно, а к первым входам пятого и шестого сумматоров через первый инвертор, при этом выходы четвертого, пятого, шестого и седьмого сумматоров соединены с блоком выбора максимального сигнала, выход которого подключен к входу решающего блока, выход которого является выходом устройства.

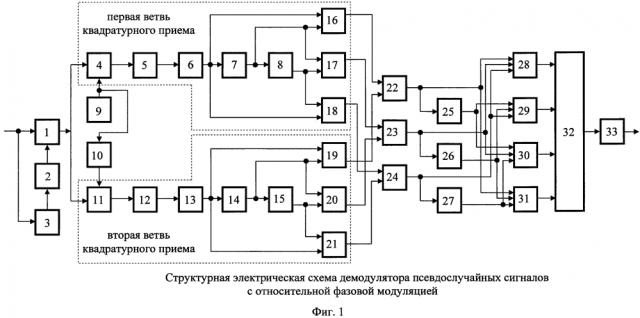

На фиг. 1 представлена структурная схема предлагаемого устройства, на фиг. 2 приведены результаты количественной оценки помехоустойчивости предлагаемого устройства.

Демодулятор псевдослучайных сигналов с относительной фазовой модуляцией состоит из первого перемножителя 1 с подключенным к нему генератором 2 псевдослучайной последовательности с блоком 3 синхронизации, двух параллельных ветвей квадратурного приема с общим входом, содержащих последовательно соединенные вторые перемножители 4 и 11, интеграторы 5 и 12, суммирующие накопители 6 и 13, третьи перемножители 16 и 19 с подключенными к их вторым входам первыми элементами задержки 7 и 14 на длительность посылки сигнала, а также подключенные к выходам первых элементов задержки 7 и 14 на длительность посылки сигнала последовательно соединенные вторые элементы задержки 8 и 15 на длительность посылки сигнала, четвертые перемножители 17 и 20, подключенные к первому и второму входам второго сумматора 23, выход которого соединен со вторыми входами четвертого 28 и шестого 30 сумматоров непосредственно, а со вторыми входами пятого 29 и седьмого 31 сумматоров через второй инвертор 26, кроме того, соединенные с выходами суммирующих накопителей 6 и 13 пятые перемножители 18 и 21, вторые входы которых подключены к выходам вторых элементов задержки на длительность посылки сигнала 8 и 15, а выходы соединены с первым и вторым входами третьего сумматора 24, выход которого соединен с третьими входами четвертого 28 и пятого 29 сумматоров непосредственно, а с третьими входами шестого 30 и седьмого 31 сумматоров через третий инвертор 27, кроме того третьи перемножители 16 и 19 параллельных ветвей квадратурного приема подключены к первому и второму входам первого сумматора 22, выход которого соединен с первыми входами четвертого 28 и седьмого 31 сумматоров непосредственно, а с первыми входами пятого 29 и шестого 30 сумматоров через первый инвертор 25, при этом выходы четвертого 28, пятого 29, шестого 30 и седьмого 31 сумматоров подключены к входу блока 32 выбора максимального сигнала, выход которого соединен с решающим блоком 33, выход которого является выходом устройства. При этом в состав первой и второй ветвей квадратурного приема входят соответственно последовательно соединенные вторые перемножители 4 и 11, интеграторы 5 и 12, суммирующие накопители 6 и 13, первые элементы задержки на длительность посылки сигнала 7 и 14, вторые элементы задержки на длительность посылки сигнала 8 и 15, четвертые перемножители 17 и 20, а также третьи перемножители 16 и 19, пятые перемножители 18 и 21. Кроме того, автономный генератор 9 опорного сигнала соединен со вторым перемножителем 4 одной из ветвей непосредственно, а со вторым перемножителем 11 другой ветви через фазовращатель 10 на π/2.

Блоки, входящие в состав предлагаемого устройства, можно реализовать на основе известных элементов схемотехники.

Перемножители 1, 4, 11, 16, 17, 18, 19, 20, 21 могут быть реализованы на основе микросхем 526ПС1 и 526 ПС2, описанных в книге: А.А. Сикарев, О.Н. Лебедев. Микроэлектронные устройства формирования и обработки сигналов. - М.: Радио и связь, 1983. с. 200-202.

Варианты реализации генератора 2 псевдослучайной последовательности описаны в книге: В.И. Коржик, В.П. Просихин. Основы криптографии. - СПб. Линк, 2008, с. 93-114.

Варианты реализации блока синхронизации 3 описаны в книге: В.И. Журавлев. Поиск и синхронизация в широкополосных системах. - М.: Радио и связь, 1986. - 240 с.

Интеграторы 5, 12, суммирующие накопители 6, 13, сумматоры 22, 23, 24, 28, 29, 30, 31 могут быть реализованы на основе схем с операционными усилителями, описанных в книгах: А.А. Сикарев, О.Н. Лебедев. Микроэлектронные устройства формирования и обработки сигналов. - М.: Радио и связь, 1983. С. 194-200; П. Хоровиц, У. Хилл. Искусство схемотехники. - М.: Мир, 1998. С. 237-238.

Блок 32 выбора максимального сигнала, в котором выполняется процедура сравнения и выбор наибольшего сигнала, может быть реализован на основе компараторов (сравнивающих устройств) - микросхем 597СА2, описанных в книгах: А.А. Сикарев, О.Н. Лебедев. Микроэлектронные устройства формирования и обработки сигналов. - М.: Радио и связь, 1983. С. 108-109, 203-205; Справочник разработчика и конструктора РЭА. Элементная база. Кн. 1. - М., 1993. Сост. Масленников М.Ю., Соболев Е.А. и др.; Горошков Б.И. Элементы радиоэлектронных устройств. Справочник. - М.: Радио и связь. С. 136-142. Блок 32 выбора максимального сигнала может быть также реализован программными средствами на микропроцессорах: В.Д. Бунтов, СБ. Макаров. Микропроцессорные системы. Часть I. Цифровые устройства. - СПб.: Издательство политехнического университета. 2008. С. 217-218.

Решающий блок 33 может быть реализован на основе D-триггера (микросхема 1564ТМ2), который описан в книге: Справочник разработчика и конструктора РЭА. Элементная база. Кн. 1. - М., 1993. Сост. Масленников М.Ю., Соболев Е.А. и др. Блок 33 формирует на выходе блока 32 выбора максимального сигнала логические значения элементов «единица» и «ноль», являющиеся результатом демодуляции.

Новая совокупность признаков, образованная за счет введения новых блоков и элементов, позволяет осуществлять обработку сигнала на удлиненном до трех посылок интервале и полнее использовать его энергетические параметры, что в итоге дает положительный эффект в виде повышения помехоустойчивости приема псевдослучайных сигналов в условиях преднамеренных помех.

Предлагаемое устройство работает следующим образом.

Принимаемый сигнал перемножается на псевдослучайную последовательность γ, формируемую местным генератором 2 псевдослучайной последовательности, который синхронизирован с сигналом при помощи блока 3 синхронизации. С выхода перемножителя 1 сигнал, с которого снята псевдослучайная последовательность, поступает по объединенному общему входу в квадратурные ветви на вторые перемножители 4 и 11. Одновременно с сигналом сюда же поступает преднамеренная помеха, которая с учетом псевдослучайного преобразования «обеляется», то есть становится случайным процессом, напоминающим естественный шум канала связи.

На вторые входы вторых перемножителей 4 и 11, являющиеся по сути фазовыми детекторами, поступает опорный сигнал от автономного генератора 9, причем на перемножитель 4 непосредственно, а на перемножитель 11 - через фазовращатель 10 на π/2, чтобы в одной из квадратурных ветвей реализовать корреляционную обработку косинусоидальной компоненты, а в другой - синусоидальной компоненты сигнала.

Продетектированные посылки сигнала проходят через интеграторы 5 и 12, которые выполняют функции фильтров нижних частот. Таким образом, на вход суммирующих накопителей 6 и 13 поступают элементы сигнала вида

где Z(t) - смесь сигнала с помехой, T0 - длительность элемента сигнала.

С выходов суммирующих накопителей 6 и 13 на первые элементы задержки 7 и 14 на длительность посылки сигнала, с которыми последовательно соединены вторые элементы задержки 8 и 15 на длительность посылки сигнала, поступают посылки сигнала и где m - номер текущей посылки, длительностью T=nT0, n - база составного сигнала. Здесь реализуется когерентное накопление элементов сигнала на длительности всей информационной посылки «0» или «1». Совокупность первых 7 и 14 и вторых 8 и 15 элементов задержки на длительность посылки сигнала формирует посылки сигнала вида

где (m-1) - задержка на длительность одной посылки, а (m-2) - задержка на длительность двух посылок составного сигнала.

Далее после прохождения соединенных в определенном порядке перемножителей 16, 17, 18, 19, 20, 21, сумматоров 22, 23, 24, инверторов 25, 26, 27 и еще одних сумматоров 28, 29, 30, 31 формируются следующие величины сигналов:

содержащие в себе накопленную энергию на длительности трех информационных посылок составного сигнала, в отличие от прототипа, где энергия накапливается только на двух посылках. При этом в двух из четырех величин сигнала с учетом правила относительной фазовой модуляции (m-1)-я и m-я посылки, то есть B, и C, определяют информационный символ «0», а две другие - информационный символ «1».

Совокупные величины сигналов Vi, поступают в блок 32 выбора максимального сигнала, который реализует посредством компараторов или на микропроцессоре известный алгоритм выбора максимальной величины. При этом если максимальным оказывается любой из вариантов сигналов в паре, соответствующей информационной посылке «0» при фактической передаче этой посылки, то это приведет к правильной регистрации сигнала. Аналогично будет и при передаче противоположной посылки сигнала, соответствующей символу «1».

Известно (см. Финк Л.М. Теоория передачи дискретных сообщений. М.: - Сов. Радио. 1970; Окунев Ю.Б. Цифровая передача информации фазомодулированными сигналами. М.: - Радио и связь. 1991), что при формировании сигналов с относительной фазовой модуляцией (ОФМ) на передаче производится перекодирование посылок сигнала так, чтобы информация вкладывалась в текущую посылку сигнала. Поэтому на приеме для принятия решения о передаче посылки сигнала соответствующей «0» или «1» необходимо осуществить обратное перекодирование. Такая операция осуществляется путем сравнения знаков полярностей посылок сигнала. При совпадении знаков предшествующей и текущей посылок сигнала регистрируется «0», при разночтении знаков - «1». С учетом этого видно, что в величине V1, являющейся совокупностью трех посылок сигнала, знак между слагаемыми не меняется, что позволяет регистрировать «0». То же самое справедливо и для величины V4, где два последних члена сохраняют свои знаки, что дает возможность также регистрировать «0». Поэтому, если максимальными оказываются величины V1 или V4, то выносится решение о приеме «нулевой» посылки сигнала. Если максимальными будут величины V2 или V3, где знак между предпоследним и последним членами в круглых скобках изменяется, то решение принимается в пользу «единичной» посылки сигнала. Такая процедура может быть реализована, как указано выше, с помощью компараторов на основе операционных усилителей либо посредством современных микропроцессорных схем. При этом, как уже отмечено, в процессе регистрации принимаемого сигнала участвуют три соседних посылки, что и способствует достижению цели - повышению помехоустойчивости приема сигналов.

Далее выбранный вариант максимального сигнала поступает в решающий блок 33, где выносится окончательное решение о регистрации посылки сигнала.

Для оценки помехоустойчивости предлагаемого устройства воспользуемся соотношением, позволяющим рассчитать вероятность ошибочного приема двоичной посылки сигнала. Данное соотношение получено в работе, упомянутой выше: P.P. Биккенин, А.Л. Фролов. Оценка эффективности некогерентного приема шумоподобных сигналов в условиях помех // Радиоэлектроника и связь, 1992, №2-3. С. 24-29, и имеет вид

где n - число элементов составного псевдослучайного сигнала; q - отношение мощностей элементов сигнала и преднамеренной помехи; F(x) - интеграл вероятностей.

Результаты расчетов по данному соотношению при обработке сигнала на интервале трех его посылок и по соотношению при обработке по двум посылкам сигнала (прототип) для различных значений n в виде графических зависимостей от отношения сигнал/помеха представлены на фиг. 2. Видно, что предлагаемое техническое решение позволяет повысить помехоустойчивость приема псевдослучайных составных сигналов в условиях организованных преднамеренных помех, мощность которых превосходит мощность передаваемых сигналов. При фиксированной величине вероятности ошибки, например при Pош=10-5, и базе составного сигнала n=100 энергетический выигрыш в предлагаемом устройстве по сравнению с прототипом составляет 1,2 дБ. Заметим, что, по отзывам иностранных специалистов, стоимость в США 1 дБ энергетического выигрыша в системе спутниковой связи составляет примерно $1000000. Причем тенденция стоимости энергетики не меняется.

Таким образом, использование новых элементов, указанных в отличительной части формулы изобретения, выгодно отличает предлагаемое техническое решение от прототипа и позволяет получить положительный эффект в виде повышения помехоустойчивости приема псевдослучайных сигналов с относительной фазовой модуляцией в условиях воздействия мощных преднамеренных помех.

Обозначение блоков

1. Перемножитель

2. Генератор ПСП

3. Блок синхронизации

4, 11. Вторые перемножители

5, 12. Интеграторы

6, 13. Суммирующие накопители

7, 14. Первые элементы задержки

8, 15. Вторые элементы задержки

9, Автономный генератор

10, Фазовращатель

16, 19. Третьи перемножители

17, 20. Четвертые перемножители

18, 21. Пятые перемножители

22. Первый сумматор

23. Второй сумматор

24. Третий сумматор

25. Первый инвертор

26. Второй инвертор

27. Третий инвертор

28. Четвертый сумматор

29. Пятой сумматор

30. Шестой сумматор

31. Седьмой сумматор

32. Блок выбора максимального сигнала

33. Решающий блок

Демодулятор псевдослучайных сигналов с относительной фазовой модуляцией, состоящий из первого перемножителя, первый вход которого является входом устройства, и подключен через последовательно соединенные блок синхронизации и генератор псевдослучайной последовательности к его второму входу, двух параллельных ветвей квадратурного приема, каждая из которых содержит последовательно соединенные вторые перемножители и интеграторы, кроме того, третьи перемножители с подключенными к их вторым входам выходов первых элементов задержки, причем первые входы вторых перемножителей соединены с выходом первого перемножителя, а также автономный генератор опорного сигнала, подключенный ко вторым входам вторых перемножителей в одной из параллельных ветвей квадратурного приема непосредственно, а ко второй - через фазовращатель на π/2, отличающийся тем, что введены в каждую из параллельных ветвей квадратурного приема суммирующие накопители, включенные между выходами интеграторов и входами первых элементов задержки и соединенные по выходу с первыми входами третьих перемножителей, а также вторые элементы задержки и четвертые перемножители, причем вторые элементы задержки включены между выходами первых элементов задержки и вторыми входами четвертых перемножителей, первые входы которых подключены к выходам первых элементов задержки, а выходы, являющиеся вторыми выходами каждой из двух параллельных ветвей квадратурного приема, подключены к первому и второму входам второго сумматора, выход которого соединен с входами четвертого и шестого сумматоров непосредственно, а со вторыми входами пятого и седьмого сумматоров через второй инвертор, кроме того, соединенные с выходами суммирующих накопителей пятые перемножители, вторые входы которых подключены к выходам вторых элементов задержки, а выходы, являющиеся третьими выходами каждой из двух параллельных ветвей квадратурного приема, соединены с первым и вторым входами третьего сумматора, выход которого подключен к третьим входам четвертого и пятого сумматоров непосредственно, а к третьим входам шестого и седьмого сумматоров через третий инвертор, дополнительно выходы третьих перемножителей, являющиеся первыми выходами каждой из двух параллельных ветвей квадратурного приема, соединены с первыми и вторыми входами первого сумматора, выход которого подключен к первым входам четвертого и седьмого сумматоров непосредственно, а к первым входам пятого и шестого сумматоров через первый инвертор, при этом выходы четвертого, пятого, шестого и седьмого сумматоров соединены с блоком выбора максимального сигнала, выход которого подключен к входу решающего блока, выход которого является выходом устройства.