Способ, система и устройство связи для оптической сетевой системы

Иллюстрации

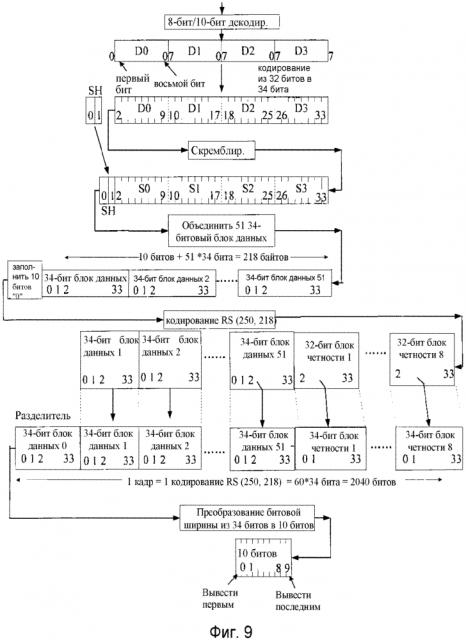

Показать всеИзобретение относится к передаче данных в оптической сетевой системе. Технический результат - экономия ресурса полосы пропускания линии и реализация контроля линии, не прерывая обслуживание. Для этого схема кодирования реализуется следующим образом: осуществляется кодирование из 32 битов в 34 бита применительно к потоку данных, подвергнутому 8-битовому/10-битовому декодированию, осуществляется кодирование с прямым исправлением ошибок применительно к потоку данных, подвергнутому кодированию из 32 битов в 34 бита, и отправляется кодированный поток данных; или осуществляется декодирование с прямым исправлением ошибок применительно к принятому потоку данных, и осуществляется декодирование из 32 битов в 34 бита применительно к потоку данных, подвергнутому декодированию с прямым исправлением ошибок. 5 н.п. и 15 з.п. ф-лы, 18 ил.

Реферат

Область техники, к которой относится изобретение

[0001] Настоящее изобретение относится к области технологий связи и, в частности, к способу, системе и устройству связи.

Уровень техники

[0002] Технология пассивной оптической сети (Passive Optical Network, PON) является одной из технологии "волокно до дома" (Fiber To The Home, FTTH), которые в настоящее время наиболее широко используются. Существующие PON можно подразделить на пассивную оптическую сеть с разделением мощности и пассивная оптическая сеть на основе мультиплексирования с разделением по длине волны (wavelength division multiplexing Passive Optical Network, WDMPON) в режиме распределения сигнала. Существующие широкополосная пассивная оптическая сеть (Broadband Passive Optical Network, BPON), гигабитная пассивная оптическая сеть (Gigabit-capable Passive Optical Network, GPON), пассивная оптическая сеть в формате Ethernet (Ethernet Passive Optical Network, EPON) и пр. являются пассивными оптическими сетями с разделением мощности. WDMPON на основе технологии мультиплексирования с разделением по длине волны реализует доступ по восходящей линии связи с использованием технологии мультиплексирования с разделением по длине волны, способна обеспечивать сравнительно высокую рабочую полосу пропускания, и реализует симметричный широкополосный доступ.

[0003] В различных системах PON, в основном, применяется схема кодирования 8b/10b; однако применение этой схемы кодирования имеет непроизводительное использование полосы пропускания до 25%, и применение этой схемы кодирования не позволяет реализовать функцию обнаружения линии для онлайновой услуги. Поэтому улучшение существующей схемы кодирования для снижения системных издержек и реализации функции обнаружения линии в системе PON становится насущной проблемой, подлежащей решению.

Сущность изобретения

[0004] В связи с этим, варианты осуществления настоящего изобретения предусматривают способ осуществления связи для оптической сетевой системы и оптическое сетевое устройство и систему для разрешения проблемы высоких системных издержек и невозможности обнаружения линии, обусловленной существующей схемой кодирования оптической сетевой системы. Применение новой схемы кодирования без изменения скорости линии (скорости передачи линии связи, линейной скорости передачи) снижает системные издержки и реализует обнаружение линии, что легко реализовать и позволяет значительно улучшить различные эксплуатационные показатели системы.

[0005] Согласно первому аспекту, настоящее изобретение предусматривает способ осуществления связи для оптической сетевой системы, причем способ осуществления связи включает в себя: прием потока данных из уровня присоединения физического носителя на скорости линии, где поток данных является потоком данных, подвергнутым 8-битовому/10-битовому кодированию; осуществление 8-битового/10-битового декодирования применительно к принятому потоку данных; осуществление кодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому 8-битовому/10-битовому декодированию; осуществление кодирования с прямым исправлением ошибок применительно к потоку данных, подвергнутому кодированию из 32 битов в 34 бита; осуществление преобразования битовой ширины 34 бита/10 битов применительно к потоку данных, подвергнутому кодированию с прямым исправлением ошибок; и отправку потока данных, подвергнутого преобразованию битовой ширины, в уровень, зависящий от физического носителя, на скорости линии.

[0006] В первом возможном варианте реализации первого аспекта, до этапа осуществления кодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому 8-битовому/10-битовому декодированию, способ осуществления связи дополнительно включает в себя:

последовательный и непрерывный прием потока данных, подвергнутого 8-битовому/10-битовому декодированию, для формирования четырех блоков данных, где любой из блоков данных является первым блоком символов управления или блоком символов данных, и любой первый блок символов управления или любой блок символов данных является 8-битовым двоичным кодом; и

определение, существует ли первый блок символов управления среди четырех блоков данных.

[0007] Согласно первому аспекту или первому возможному варианту реализации первого аспекта, во втором возможном варианте реализации, осуществление кодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому 8-битовому/10-битовому декодированию, в частности, включает в себя:

если среди четырех блоков данных не существует первых блоков символов управления, добавление первой синхронизирующей головной части в заголовок первого блока данных среди четырех блоков данных, и вывод блоков данных, в которые добавлена первая синхронизирующая головная часть, где первый блок данных является 8-битовым двоичным кодом, введенным первым, первая синхронизирующая головная часть включает в себя 2-битовый первый идентификатор, и первый идентификатор используется для идентификации, что все блоки данных являются блоками символов данных.

[0008] Согласно первому аспекту, первому возможному варианту реализации первого аспекта или второму возможному варианту реализации первого аспекта, в третьем возможном варианте реализации, способ осуществления связи дополнительно включает в себя:

осуществление кодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому 8-битовому/10-битовому декодированию, в частности, включает в себя:

если среди четырех блоков данных существует, по меньшей мере, один первый блок символов управления, добавление второй синхронизирующей головной части в заголовок первого блока данных среди четырех блоков данных, где первый блок данных является 8-битовым двоичным кодом, введенным первым, вторая синхронизирующая головная часть включает в себя 2-битовый второй идентификатор, и второй идентификатор используется для идентификации, что среди блоков данных существует, по меньшей мере, один первый блок символов управления;

генерацию, согласно количеству первых блоков символов управления среди четырех блоков данных и положению первого блока управления среди блоков данных, 4-битовый код отображения положения блока символов управления, и установление кода отображения положения блока символов управления, в положении после второй синхронизирующей головной части и в непосредственной близости ко второй синхронизирующей головной части;

соответственно, преобразование первого блока символов управления среди четырех блоков данных в 4-битовый второй блок символов управления; и

вывод обработанных блоков данных, где обработанные блоки данных включают в себя вторую синхронизирующую головную часть, код отображения положения блока символов управления и второй блок символов управления, полученный после преобразования, или обработанные блоки данных включают в себя вторую синхронизирующую головную часть, код отображения положения блока символов управления, второй блок символов управления, полученный после преобразования, и блок символов данных.

[0009] Согласно первому аспекту, первому возможному варианту реализации первого аспекта, второму возможному варианту реализации первого аспекта и третьему возможному варианту реализации первого аспекта, в четвертом возможном варианте реализации, вывод обработанных блоков данных, в частности, включает в себя:

если четыре блока данных дополнительно включают в себя, по меньшей мере, один блок символов данных, отказ от осуществления обработки на блоке символов данных среди четырех блоков данных, и оставляют блок символов данных среди блоков данных; и

вывод обработанных блоков данных, где обработанные блоки данных включают в себя вторую синхронизирующую головную часть, код отображения положения блока символов управления, второй блок символов управления, полученный после преобразования, и блок данных блока символов данных.

[0010] Согласно первому аспекту, первому возможному варианту реализации первого аспекта, второму возможному варианту реализации первого аспекта, третьему возможному варианту реализации первого аспекта и четвертому возможному варианту реализации первого аспекта, в пятом возможном варианте реализации, способ дополнительно включает в себя: определение, равно ли 34 количество битов, включенных в выходные обработанные блоки данных; и

если количество битов, включенных в выходные обработанные блоки данных, меньше 34, добавление случайного числа в хвостовую часть последнего блока данных среди выходных обработанных блоков данных, пока количество битов выходных обработанных блоков данных не достигнет 34, где случайное число является случайно генерируемым двоичным кодом.

[0011] Согласно первому аспекту, первому возможному варианту реализации первого аспекта, второму возможному варианту реализации первого аспекта, третьему возможному варианту реализации первого аспекта, четвертому возможному варианту реализации первого аспекта и пятому возможному варианту реализации первого аспекта, в шестом возможном варианте реализации, после этапа приема потока данных из уровня присоединения физического носителя на скорости линии, способ осуществления связи дополнительно включает в себя: синхронизацию потока данных, подвергнутого 8-битовому/10-битовому кодированию.

[0012] Согласно первому аспекту, первому возможному варианту реализации первого аспекта, второму возможному варианту реализации первого аспекта, третьему возможному варианту реализации первого аспекта, четвертому возможному варианту реализации первого аспекта, пятому возможному варианту реализации первого аспекта и шестому возможному варианту реализации первого аспекта, в седьмом возможном варианте реализации, после этапа осуществления кодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому 8-битовому/10-битовому декодированию, способ осуществления связи дополнительно включает в себя:

скремблирование потока данных за исключением первой синхронизирующей головной части или второй синхронизирующей [0010] Согласно первому аспекту, первому возможному варианту реализации первого аспекта, второму возможному варианту реализации первого аспекта, третьему возможному варианту реализации первого аспекта и четвертому возможному варианту реализации первого аспекта, в пятом возможном варианте реализации, определение, равно ли 34 количество битов, включенных в выходные обработанные блоки данных; и

если количество битов, включенных в выходные обработанные блоки данных, меньше 34, добавление случайного числа в хвостовую часть последнего блока данных среди выходных обработанных блоков данных, пока количество битов выходных обработанных блоков данных не достигнет 34, где случайное число является случайно генерируемым двоичным кодом.

[0011] Согласно первому аспекту, первому возможному варианту реализации первого аспекта, второму возможному варианту реализации первого аспекта, третьему возможному варианту реализации первого аспекта, четвертому возможному варианту реализации первого аспекта и пятому возможному варианту реализации первого аспекта, в шестом возможном варианте реализации, после этапа приема потока данных из уровня присоединения физического носителя на скорости линии, способ осуществления связи дополнительно включает в себя: синхронизацию потока данных, подвергнутого 8-битовому/10-битовому кодированию.

[0012] Согласно первому аспекту, первому возможному варианту реализации первого аспекта, второму возможному варианту реализации первого аспекта, третьему возможному варианту реализации первого аспекта, четвертому возможному варианту реализации первого аспекта, пятому возможному варианту реализации первого аспекта и шестому возможному варианту реализации первого аспекта, в седьмом возможном варианте реализации, после этапа осуществления кодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому 8-битовому/10-битовому декодированию, способ осуществления связи дополнительно включает в себя:

скремблирование потока данных за исключением первой синхронизирующей головной части или второй синхронизирующей головной части в потоке данных, подвергнутом кодированию из 32 битов в 34 бита.

[0013] Согласно второму аспекту, настоящее изобретение предусматривает способ осуществления связи для оптической сетевой системы, причем способ осуществления связи включает в себя: прием поток данных из уровня, зависящего от физического носителя, на скорости линии, где поток данных является потоком данных, подвергнутым кодированию из 32 битов в 34 бита;

осуществление преобразования битовой ширины 10 битов/34 битов применительно к принятому потоку данных;

осуществление декодирования с прямым исправлением ошибок применительно к потоку данных, подвергнутому преобразованию битовой ширины;

осуществление декодирования из 32 битов в 34 бита (то есть декодирование данных, закодированных с помощью кодирования из 32 битов в 34 бита) применительно к потоку данных, подвергнутому декодированию с прямым исправлением ошибок;

осуществление 8-битового/10-битового кодирования применительно к потоку данных, подвергнутому декодированию из 32 битов в 34 бита; и

отправку потока данных, подвергнутого 8-битовому/10-битовому кодированию, на уровень присоединения физического носителя.

[0014] Согласно второму аспекту, в первом возможном варианте реализации второго аспекта, до этапа осуществления декодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому декодированию с прямым исправлением ошибок, способ осуществления связи дополнительно включает в себя:

синтаксический анализ потока данных, подвергнутого декодированию с прямым исправлением ошибок, и вывод 51 блока данных, где любой из блоков данных является вторым блоком символов управления или блоком символов данных, любой второй блок символов управления является 4-битовым двоичным кодом, и любой блок символов данных является 8-битовым двоичным кодом;

синтаксический анализ любого из блоков данных и получение синхронизирующей головной части любого из блоков данных, где синхронизирующая головная часть включает в себя: первую синхронизирующую головную часть или вторую синхронизирующую головную часть, первая синхронизирующая головная часть включает в себя 2-битовый первый идентификатор, первый идентификатор используется для идентификации, что все блоки данных являются блоками символов данных, вторая синхронизирующая головная часть включает в себя 2-битовый второй идентификатор, и второй идентификатор используется для идентификации, что среди блоков данных существует, по меньшей мере, один второй блок символов управления; и

определение, является ли синхронизирующая головная часть любого из блоков данных первой синхронизирующей головной частью или второй синхронизирующей головной частью.

[0015] Согласно второму аспекту или первому возможному варианту реализации второго аспекта, во втором возможном варианте реализации, этап осуществления декодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому декодированию с прямым исправлением ошибок, в частности, включает в себя:

если синхронизирующая головная часть является первой синхронизирующей головной частью, удаление первой синхронизирующей головной части и вывод блоков данных, откуда удалена первая синхронизирующая головная часть.

[0016] Согласно второму аспекту, первому возможному варианту реализации второго аспекта или второму возможному варианту реализации второго аспекта, в третьем возможном варианте реализации, этап осуществления декодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому декодированию с прямым исправлением ошибок, в частности, включает в себя:

если синхронизирующая головная часть является второй синхронизирующей головной частью, синтаксический анализ блоков данных и получение 4-битового кода отображения положения блока символов управления;

получение количества вторых блоков символов управления среди блоков данных и положения второго блока символов управления среди блоков данных согласно коду отображения положения блока символов управления;

соответственно, преобразование второго блока символов управления среди блоков данных в 8-битовый первый блок символов управления согласно количеству вторых блоков символов управления и положению второго блока символов управления среди блоков данных;

удаление второй синхронизирующей головной части и кода отображения положения блока символов управления из блоков данных, где код отображения положения блока символов управления располагается после второй синхронизирующей головной части и в непосредственной близости ко второй синхронизирующей головной части; и

вывод обработанных блоков данных, где обработанные блоки данных включают в себя: первый блок символов управления и/или блок символов данных, и любой первый блок символов управления или любой блок символов данных является 8-битовым двоичным кодом.

[0017] Согласно второму аспекту, первому возможному варианту реализации второго аспекта, второму возможному варианту реализации второго аспекта или третьему возможному варианту реализации второго аспекта, в четвертом возможном варианте реализации, этап вывода обработанных блоков данных, в частности, включает в себя:

если блоки данных дополнительно включают в себя, по меньшей мере, один блок символов данных, не осуществляют обработку на блоке символов данных среди блоков данных, и оставляют блок символов данных; и

вывод обработанных блоков данных, где обработанные блоки данных включают в себя: первый символ управления и блок символов данных.

[0018] Согласно второму аспекту, первому возможному варианту реализации второго аспекта, второму возможному варианту реализации второго аспекта, третьему возможному варианту реализации второго аспекта или четвертому возможному варианту реализации второго аспекта, в пятом возможном варианте реализации, до этапа осуществления преобразования битовой ширины 10 битов/34 битов применительно к принятому потоку данных, способ осуществления связи дополнительно включает в себя: синхронизацию принятого потока данных.

[0019] Согласно второму аспекту, первому возможному варианту реализации второго аспекта, второму возможному варианту реализации второго аспекта, третьему возможному варианту реализации второго аспекта, четвертому возможному варианту реализации второго аспекта или пятому возможному варианту реализации второго аспекта, в шестом возможном варианте реализации, до этапа осуществления декодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому декодированию с прямым исправлением ошибок, способ осуществления связи дополнительно включает в себя:

дескремблирование потока данных за исключением первой синхронизирующей головной части или второй синхронизирующей головной части в потоке данных, подвергнутому декодированию с прямым исправлением ошибок.

[0020] Согласно третьему аспекту, настоящее изобретение предусматривает оптическое сетевое устройство, где оптическое сетевое устройство включает в себя:

первый модуль интерфейса, выполненный с возможностью приема потока данных из уровня присоединения физического носителя на скорости линии, где поток данных является потоком данных, подвергнутым 8-битовому/10-битовому кодированию, и осуществления последовательно-параллельного преобразования применительно к принятому потоку данных;

8-битовый/10-битовый декодер, выполненный с возможностью осуществления 8-битового/10-битового декодирования применительно к принятому потоку данных и вывода потока данных, подвергнутого 8-битовому/10-битовому декодированию;

кодер из 32 битов в 34 бита, выполненный с возможностью осуществления кодирования из 32 битов в 34 бита применительно к выходному потоку данных, подвергнутому 8-битовому/10-битовому декодированию, и вывода потока данных, подвергнутого кодированию из 32 битов в 34 бита;

кодер с прямым исправлением ошибок, выполненный с возможностью осуществления кодирования с прямым исправлением ошибок применительно к выходному потоку данных, подвергнутому кодированию из 32 битов в 34 бита, и вывода потока данных, подвергнутого кодированию с прямым исправлением ошибок;

первый преобразователь битовой ширины, выполненный с возможностью осуществления преобразования битовой ширины 34 бита/10 битов применительно к выходному потоку данных, подвергнутому кодированию с прямым исправлением ошибок; и

второй модуль интерфейса, выполненный с возможностью отправки потока данных, подвергнутого преобразованию битовой ширины, в уровень, зависящий от физического носителя, на скорости линии.

[0021] Согласно третьему аспекту, в первом возможном варианте реализации третьего аспекта, кодер из 32 битов в 34 бита дополнительно включает в себя:

первый модуль приема, выполненный с возможностью последовательно и непрерывно принимать поток данных, подвергнутый 8-битовому/10-битовому декодированию, для формирования четырех блоков данных, где любой из блоков данных является первым блоком символов управления или блоком символов данных, и любой первый блок символов управления или любой блок символов данных является 8-битовым двоичным кодом; и

первый модуль определения, выполненный с возможностью определения, существует ли первый блок символов управления среди четырех блоков данных.

[0022] Согласно третьему аспекту или первому возможному варианту реализации третьего аспекта, во втором возможном варианте реализации, кодер из 32 битов в 34 бита дополнительно включает в себя:

первый модуль обработки, выполненный с возможностью: если среди четырех блоков данных не существует первых блоков символов управления, добавлять первую синхронизирующую головную часть в заголовок первого блока данных среди четырех блоков данных, и выводить блоки данных, в которые добавлена первая синхронизирующая головная часть, где первый блок данных является 8-битовым двоичным кодом, введенным первым, первая синхронизирующая головная часть включает в себя 2-битовый первый идентификатор, и первый идентификатор используется для идентификации, что все блоки данных являются блоками символов данных.

[0023] Согласно третьему аспекту, первому возможному варианту реализации третьего аспекта или второму возможному варианту реализации третьего аспекта, в третьем возможном варианте реализации третьего аспекта, кодер из 32 битов в 34 бита дополнительно включает в себя второй модуль обработки, и второй модуль обработки в частности, включает в себя:

модуль генерации синхронизирующей головной части, выполненный с возможностью: если среди четырех блоков данных существует, по меньшей мере, один первый блок символов управления, добавлять вторую синхронизирующую головную часть в заголовок первого блока данных среди четырех блоков данных, где первый блок данных является 8-битовым двоичным кодом, введенным первым, вторая синхронизирующая головная часть включает в себя 2-битовый второй идентификатор, и второй идентификатор используется для идентификации, что среди блоков данных существует, по меньшей мере, один первый блок символов управления;

модуль генерации кода отображения, выполненный с возможностью генерации, согласно количеству первых блоков символов управления среди четырех блоков данных и положению первого блока управления среди блоков данных, 4-битового кода отображения положения блока символов управления, и установления кода отображения положения блока символов управления, в положении после второй синхронизирующей головной части и в непосредственной близости ко второй синхронизирующей головной части;

модуль преобразования первого блока символов управления, выполненный с возможностью, соответственно, преобразовывать первый блок символов управления среди четырех блоков данных в 4-битовый второй блок символов управления; и

первый модуль вывода, выполненный с возможностью вывода обработанных блоков данных, где обработанные блоки данных включают в себя вторую синхронизирующую головную часть, код отображения положения блока символов управления и второй блок символов управления, полученный после преобразования, или обработанные блоки данных включают в себя вторую синхронизирующую головную часть, код отображения положения блока символов управления, второй блок символов управления, полученный после преобразования, и блок символов данных.

[0024] Согласно третьему аспекту, первому возможному варианту реализации третьего аспекта, второму возможному варианту реализации третьего аспекта или третьему возможному варианту реализации третьего аспекта, в четвертом возможном варианте реализации третьего аспекта, первый модуль вывода в частности, выполнен с возможностью: если четыре блока данных дополнительно включают в себя, по меньшей мере, один блок символов данных, не осуществлять обработку на блоке символов данных среди четырех блоков данных, и оставлять блок символов данных среди блоков данных; и выводить обработанные блоки данных, где обработанные блоки данных включают в себя вторую синхронизирующую головную часть, код отображения положения блока символов управления, второй блок символов управления, полученный после преобразования, и блок данных блока символов данных.

[0025] Согласно третьему аспекту, первому возможному варианту реализации третьего аспекта, второму возможному варианту реализации третьего аспекта, третьему возможному варианту реализации третьего аспекта или четвертому возможному варианту реализации третьего аспекта, в пятом возможном варианте реализации третьего аспекта, первый модуль вывода дополнительно выполнен с возможностью определения, равно ли 34 количество битов, включенных в выходные обработанные блоки данных; и если количество битов, включенных в выходные обработанные блоки данных, меньше 34, добавления случайного числа в хвостовую часть выходных обработанных блоков данных, пока количество битов выходных обработанных блоков данных не достигнет 34, где случайное число является случайно генерируемым двоичным кодом.

[0026] Согласно третьему аспекту, первому возможному варианту реализации третьего аспекта, второму возможному варианту реализации третьего аспекта, третьему возможному варианту реализации третьего аспекта, четвертому возможному варианту реализации третьего аспекта или пятому возможному варианту реализации третьего аспекта, в шестом возможном варианте реализации третьего аспекта, оптическое сетевое устройство дополнительно включает в себя:

первый модуль синхронизации, выполненный с возможностью синхронизации потока данных, подвергнутого 8-битовому/10-битовому кодированию.

[0027] Согласно третьему аспекту, первому возможному варианту реализации третьего аспекта, второму возможному варианту реализации третьего аспекта, третьему возможному варианту реализации третьего аспекта, четвертому возможному варианту реализации третьего аспекта, пятому возможному варианту реализации третьего аспекта или шестому возможному варианту реализации третьего аспекта, в седьмом возможном варианте реализации третьего аспекта, оптическое сетевое устройство дополнительно включает в себя: скремблер, выполненный с возможностью скремблирования потока данных за исключением первой синхронизирующей головной части или второй синхронизирующей головной части в потоке данных, подвергнутом кодированию из 32 битов в 34 бита.

[0028] Согласно четвертому аспекту, настоящее изобретение предусматривает оптическое сетевое устройство, где оптическое сетевое устройство включает в себя:

третий модуль интерфейса, выполненный с возможностью приема поток данных из уровня, зависящего от физического носителя, на скорости линии, где поток данных является потоком данных, подвергнутым кодированию из 32 битов в 34 бита;

второй преобразователь битовой ширины, выполненный с возможностью осуществления преобразования битовой ширины 10 битов/34 битов применительно к принятому потоку данных;

декодер с прямым исправлением ошибок, выполненный с возможностью осуществления декодирования с прямым исправлением ошибок применительно к потоку данных, подвергнутому преобразованию битовой ширины;

декодер из 32 битов в 34 бита, выполненный с возможностью осуществления декодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому декодированию с прямым исправлением ошибок;

8-битовый/10-битовый кодер, выполненный с возможностью осуществления 8-битового/10-битового кодирования применительно к потоку данных, подвергнутому декодированию из 32 битов в 34 бита; и

четвертый модуль интерфейса, выполненный с возможностью отправки потока данных, подвергнутого 8-битовому/10-битовому кодированию, на уровень присоединения физического носителя.

[0029] Согласно четвертому аспекту, в первом возможном варианте реализации четвертого аспекта, декодер из 32 битов в 34 бита включает в себя:

первый модуль синтаксического анализа, выполненный с возможностью синтаксического анализа потока данных, подвергнутого декодированию с прямым исправлением ошибок, и вывода 51 блока данных, где любой из блоков данных является вторым блоком символов управления или блоком символов данных, любой второй блок символов управления является 4-битовым двоичным кодом, и любой блок символов данных является 8-битовым двоичным кодом;

второй модуль синтаксического анализа, выполненный с возможностью синтаксического анализа любого из блоков данных, и получения синхронизирующей головной части любого из блоков данных, где синхронизирующая головная часть включает в себя: первую синхронизирующую головную часть или вторую синхронизирующую головную часть, первая синхронизирующая головная часть включает в себя 2-битовый первый идентификатор, первый идентификатор используется для идентификации, что все блоки данных являются блоками символов данных, вторая синхронизирующая головная часть включает в себя 2-битовый второй идентификатор, и второй идентификатор используется для идентификации, что среди блоков данных существует, по меньшей мере, один второй блок символов управления; и

второй модуль определения, выполненный с возможностью определения, является ли синхронизирующая головная часть любого из блоков данных первой синхронизирующей головной частью или второй синхронизирующей головной частью.

[0030] Согласно четвертому аспекту или первому возможному варианту реализации четвертого аспекта, во втором возможном варианте реализации, декодер из 32 битов в 34 бита дополнительно включает в себя:

третий модуль обработки, выполненный с возможностью: если синхронизирующая головная часть является первой синхронизирующей головной частью, удаления первой синхронизирующей головной части, и вывода блоков данных, откуда удалена первая синхронизирующая головная часть.

[0031] Согласно четвертому аспекту, первому возможному варианту реализации четвертого аспекта или второму возможному варианту реализации четвертого аспекта, в третьем возможном варианте реализации четвертого аспекта, декодер из 32 битов в 34 бита дополнительно включает в себя четвертый модуль обработки, и четвертый модуль обработки в частности, включает в себя:

модуль синтаксического анализа кода отображения, выполненный с возможностью: если синхронизирующая головная часть является второй синхронизирующей головной частью, синтаксического анализа блоков данных, и получения 4-битового кода отображения положения блока символов управления;

модуль преобразования второго символа управления, выполненный с возможностью получения количества вторых блоков символов управления среди блоков данных и положения второго блока символов управления среди блоков данных согласно коду отображения положения блока символов управления; и, соответственно, преобразования второго блока символов управления среди блоков данных в 8-битовый первый блок символов управления согласно количеству вторых блоков символов управления и положению второго блока символов управления среди блоков данных;

модуль удаления синхронизирующей головной части, выполненный с возможностью удаления второй синхронизирующей головной части и кода отображения положения блока символов управления из блоков данных, где код отображения положения блока символов управления располагается после второй синхронизирующей головной части и в непосредственной близости ко второй синхронизирующей головной части; и

второй модуль вывода, выполненный с возможностью вывода обработанных блоков данных, где обработанные блоки данных включают в себя: первый блок символов управления и/или блок символов данных, и любой первый блок символов управления или любой блок символов данных является 8-битовым двоичным кодом.

[0032] Согласно четвертому аспекту, первому возможному варианту реализации четвертого аспекта, второму возможному варианту реализации четвертого аспекта или третьему возможному варианту реализации четвертого аспекта, в четвертом возможном варианте реализации четвертого аспекта, второй модуль вывода, в частности, выполнен с возможностью: если блоки данных дополнительно включают в себя, по меньшей мере, один блок символов данных, не осуществлять обработку на блоке символов данных среди блоков данных, и оставлять блок символов данных; и выводить обработанные блоки данных, где обработанные блоки данных включают в себя: первый символ управления и блок символов данных.

[0033] Согласно четвертому аспекту, первому возможному варианту реализации четвертого аспекта, второму возможному варианту реализации четвертого аспекта, третьему возможному варианту реализации четвертого аспекта или четвертому возможному варианту реализации четвертого аспекта, в пятом возможном варианте реализации четвертого аспекта, оптическое сетевое устройство дополнительно включает в себя:

второй модуль синхронизации, выполненный с возможностью синхронизации принятого потока данных.

[0034] Согласно четвертому аспекту, первому возможному варианту реализации четвертого аспекта, второму возможному варианту реализации четвертого аспекта, третьему возможному варианту реализации четвертого аспекта, четвертому возможному варианту реализации четвертого аспекта или пятому возможному варианту реализации четвертого аспекта, в шестом возможном варианте реализации четвертого аспекта, оптическое сетевое устройство дополнительно включает в себя:

дескремблер, выполненный с возможностью дексремблирования потока данных за исключением первой синхронизирующей головной части или второй синхронизирующей головной части в потоке данных, подвергнутому декодированию с прямым исправлением ошибок.

[0035] Согласно пятому аспекту, настоящее изобретение предусматривает оптическую сетевую систему, где оптическая сетевая система включает в себя: оптическое сетевое устройство согласно третьему аспекту и оптическое сетевое устройство согласно четвертому аспекту.

[0036] Согласно шестому аспекту, настоящее изобретение предусматривает оптическую сетевую систему, где оптическая сетевая система включает в себя, по меньшей мере: терминал оптической линии и оптический сетевой модуль, где терминал оптической линии включает в себя оптическое сетевое устройство согласно третьему аспекту, и оптический сетевой модуль включает в себя оптическое сетевое устройство согласно четвертому аспекту; или оптический сетевой модуль включает в себя оптическое сетевое устройство согласно третьему аспекту, и терминал оптической линии включает в себя оптическое сетевое устройство согласно четвертому аспекту.

[0037] Новая схема кодирования реализуется с использованием вышеописанных решений: осуществление кодирования из 32 битов в 34 бита применительно к потоку данных, подвергнутому 8-битовому/10-битовому декодированию, осуществление кодирования с прямым исправлением ошибок применительно к потоку данных, подвергнутому кодированию из 32 битов в 34 бита, и отправка кодированного потока данных; или осуществление декодирования с прямым исправлением ошибок применительно к принятому потоку данных, и осуществление декодирования из 32 би