Системы и способы проверки адреса возврата процедуры

Иллюстрации

Показать всеГруппа изобретений относится к компьютерной технике и может быть использована для проверки адреса возврата процедуры. Техническим результатом является предотвращение несанкционированной модификации стека. Устройство содержит указатель стека для указания на первый адрес возврата, хранящийся в стеке; указатель буфера адреса возврата для указания на второй адрес возврата, хранящийся в буфере адреса возврата; и логическое устройство проверки адреса возврата для сравнения первого адреса возврата со вторым адресом возврата в ответ на прием команды возврата и исполнения, в ответ на прием команды модификации буфера адреса возврата, по меньшей мере одного действия из: сохранения адреса возврата в буфере адреса возврата или удаления адреса возврата из буфера адреса возврата, причем команда модификации буфера адреса возврата является привилегированной командой. 3 н. и 14 з.п. ф-лы, 12 ил.

Реферат

Область техники, к которой относится изобретение

Настоящее изобретение в общем относится к компьютерным системам, в частности к системам и способам проверки адреса возврата процедуры.

Уровень техники

Вредоносное программное обеспечение может использовать разнообразные способы искажения адреса возврата для осуществления атаки посредством возвратно-ориентированного программирования (return-oriented programming (ROP)). Программирование ROP представляет собой способ захвата или перехвата потока выполнения текущего процесса посредством использования команды возврата, которая, во многих процессорных архитектурах, вызывает с вершины стека адрес следующей подлежащей выполнению команды, обычно представляющей собой команду, следующую за соответствующей командой вызова в вызывающей подпрограмме. Таким образом, посредством модификации адреса возврата в стеке атакующая сторона (далее - взломщик) может перенаправить поток выполнения текущего процесса в произвольную область памяти. Захватив поток выполнения, взломщик может, например, инициализировать аргументы и осуществить вызов библиотечной функции. Этот способ известен под названием «возврат в библиотеку» (“return-into-library”). В другом примере взломщик может находить в пределах сегмента кода последовательности из нескольких команд для выполнения. Этот подход известен под названием «способ заимствования кусков кода» (“borrowed code chunks technique”).

Взломщик может использовать разнообразные способы для первоначального повреждения стека, которое также именуется «подменой стека» или «поворотом стека» (“stack pivoting”). Например, способ переполнения буфера (buffer overflow) предусматривает передачу большего объема входных данных, чем ожидает принять подпрограмма, в предположении, что входной буфер расположен в стеке.

Краткое описание чертежей

Настоящее изобретение проиллюстрировано примерами, не служащими для ограничения, и может быть более полно понято с использованием последующего подробного описания, которое следует рассматривать вместе с чертежами, где:

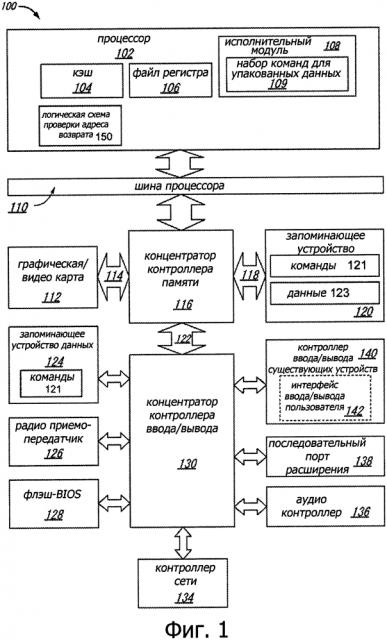

фиг. 1 представляет диаграмму компонентов высокого уровня, составляющих пример компьютерной системы, согласно одному или более аспектам настоящего изобретения;

фиг. 2 представляет блок-схему процессора согласно одному или более аспектам настоящего изобретения;

фиг. 3a-3b схематично иллюстрируют элементы микроархитектуры процессора согласно одному или более аспектам настоящего изобретения;

фиг. 4 схематично иллюстрирует некоторые аспекты примера процессора и других компонентов примера компьютерной системы 100, показанной на фиг. 1, согласно одному или более аспектам настоящего изобретения;

фиг. 5 упрощенно иллюстрирует один пример схемы распределения памяти в стеке компьютерной системы согласно одному или более аспектам настоящего изобретения;

фиг. 6 упрощенно иллюстрирует один пример схемы распределения памяти в буфере адреса возврата согласно одному или более аспектам настоящего изобретения;

фиг. 7 представляет логическую схему способа обнаружения несанкционированной подмены стека согласно одному или более аспектам настоящего изобретения;

фиг. 8 представляет блок-схему примера компьютерной системы согласно одному или более аспектам настоящего изобретения;

фиг. 9 представляет блок-схему примера системы на кристалле (system on a chip (SoC)), согласно одному или более аспектам настоящего изобретения;

фиг. 10 представляет блок-схему примера компьютерной системы согласно одному или более аспектам настоящего изобретения; и

фиг. 11 представляет блок-схему примера системы на кристалле (SoC), согласно одному или более аспектам настоящего изобретения.

Осуществление изобретения

Здесь предложены компьютерные системы и способы проверки адреса возврата процедуры. Несанкционированная модификация или подмена стека может быть использована потенциальным взломщиком в попытке осуществить атаку способом возвратно-ориентированного программирования (ROP). Такая атака может содержать несанкционированную модификацию адреса возврата процедуры, записанного в стеке, с целью перенаправить поток выполнения текущего процесса в произвольную область памяти. Взломщик может использовать разнообразные способы для несанкционированной модификации стека. Например, способ переполнения буфера использует передачу в буфер большего объема данных, чем подпрограмма ожидает принять, в предположении, что входной буфер расположен в рассматриваемом стеке.

Для предотвращения несанкционированной модификации стека компьютерная система может поддерживать буфер адреса возврата, предназначенный для резервного хранения, вместе со стеком компьютерной системы, адресов возврата процедур. В ответ на прием команды вызова процессор компьютерной системы может поместить адрес возврата и в стек, и в буфер адреса возврата. В ответ на прием команды возврата процессор может вызвать и сравнить адреса возврата из стека и из буфера адреса возврата. Если два адреса совпадут, процессор может продолжить выполнение команды возврата; в противном случае процессор может генерировать исключение, предотвращая тем самым захват потока выполнения текущего процесса потенциальным взломщиком. Разнообразные аспекты перечисленных выше способов и систем рассмотрены ниже подробно на примерах, а не посредством ограничений.

В последующем описании приведены многочисленные конкретные подробности, такие как примеры конкретных типов процессоров и конфигураций системы, конкретные структуры аппаратуры, конкретные подробности архитектуры и микроархитектуры, конкретные конфигурации регистров, конкретные типы команд, конкретные компоненты систем, конкретные размеры/высоты, конкретные ступени и операции процессорного конвейера с целью предоставления полного понимания настоящего изобретения. Специалисту в рассматриваемой области должно быть очевидно, однако, что все эти конкретные подробности не обязательно должны быть использованы в конкретной практической реализации описываемых здесь способов. В других случаях хорошо известные компоненты или способы, такие как конкретные и альтернативные архитектуры процессоров, конкретные логические схемы/коды для описываемых алгоритмов, конкретные коды встроенного программного обеспечения, конкретные соединительные операции, конкретные логические конфигурации, конкретные способы изготовления и материалы, конкретные реализации компиляторов, конкретные выражения алгоритмов в виде кода, конкретные способы/логические схемы выключения питания/стробирования и другие конкретные детали работы компьютерных систем здесь не были рассмотрены подробно, чтобы избежать ненужного «затемнения» предмета настоящего изобретения.

Хотя последующие варианты описаны здесь со ссылками на процессор, другие варианты могут быть применены к другим типам интегральных схем и логических устройств. Способы и принципы, аналогичные рассматриваемым здесь вариантам, могут быть применены к другим типам схем или полупроводниковых приборов, которые могут выиграть от более высокой пропускной способности систем конвейерного типа и повышенной производительности. Принципы рассматриваемых здесь вариантов применимы к любому процессору или машине, осуществляющим манипуляции с данными. Однако настоящее изобретение не ограничивается процессорами или машинами, осуществляющими операции с размерностью 512 разрядов, 256 разрядов, 128 разрядов, 64 разряда, 32 разряда или 16 разрядов над данными, и может быть применено к любому процессору и машине, в которых осуществляется манипуляция с данными или управление данными. Кроме того, последующее описание предлагает примеры, а прилагаемые чертежи показывают различные примеры с целью иллюстрации. Однако эти примеры не следует толковать в ограничительном смысле, поскольку они предназначены только служить примерами описываемых здесь вариантов, а не создать исчерпывающий перечень всех возможных реализаций описываемых здесь вариантов.

Хотя приведенные ниже примеры описывают обработку и распределение команд в контексте исполнительных модулей и логических схем, другие варианты систем и способов, описываемых здесь, могут быть реализованы с применением данных и команд, записанных на машиночитаемом материальном носителе, так что при выполнении этих команд машина осуществляет функции, соответствующие по меньшей мере одному из описываемых здесь вариантов. В одном из вариантов функции, ассоциированные с рассматриваемыми здесь вариантами, воплощены в исполняемых машиной командах. Выполняя указанные команды, процессор общего или специального назначения, запрограммированный этими командами, может осуществлять рассматриваемые здесь способы. Рассматриваемые здесь варианты могут быть реализованы в виде компьютерного программного продукта или программного обеспечения, которое может быть выполнено в виде машиночитаемого или читаемого компьютером носителя с записанными на нем командами, каковые могут быть использованы для программирования компьютера (или других электронных устройств) с целью осуществления одной или нескольких операций согласно рассматриваемым здесь вариантам. В качестве альтернативы, операции описываемых здесь вариантов могут быть выполнены специализированными компонентами аппаратуры, содержащими логические устройства с фиксированными функциями для осуществления этих операций, или посредством какого-либо сочетания программируемых компьютерных компонентов и компонентов аппаратуры с фиксированными функциями.

Команды, используемые для программирования логических устройств с целью осуществления описываемых здесь способов, могут быть сохранены в памяти системы, такой как динамическое запоминающее устройство с произвольной выборкой (динамическое ЗУПВ (DRAM)), кэш-память, флэш-память или другое запоминающее устройство. Более того, команды можно распределять через сеть связи или посредством какого-либо другого компьютерного носителя. Таким образом, машиночитаемый носитель может содержать какой-либо механизм для сохранения или передачи информации в форме, читаемой машиной (например, компьютером), не ограничиваясь прилагаемым перечнем, дискеты, оптические диски, постоянное запоминающее устройство на компакт-дисках (Compact Disc, Read-Only Memory (CD-ROM)), и магнитооптические диски, постоянные запоминающие устройства (ПЗУ (Read-Only Memory (ROM))), запоминающие устройства с произвольной выборкой (ЗУПВ (Random Access Memory (RAM))), стираемые программируемые постоянные запоминающие устройства (СППЗУ (Erasable Programmable Read-Only Memory (EPROM))), электрически стираемые и программируемые постоянные запоминающие устройства (ЭСППЗУ (Electrically Erasable Programmable Read-Only Memory (EEPROM))), магнитные или оптические карточки, флэш-память или какой-либо материальный машиночитаемый носитель, используемый при передаче информации через Интернет посредством распространяющихся сигналов в электрической, оптической, акустической или иной форме (например, волны несущих, инфракрасные сигналы, цифровые сигналы и т.п.). Соответственно, машиночитаемый носитель представляет собой материальный машиночитаемый носитель какого-либо типа, подходящий для хранения или передачи электронных команд или информации в форме, читаемой машиной (например, компьютером).

Термин «процессор» здесь будет обозначать устройство, способное выполнять команды, кодирующие арифметические и логические операции, а также операции ввода/вывода. В одном из иллюстративных примеров процессор может быть построен в соответствии с архитектурной моделью фон Неймана и может содержать арифметико-логическое устройство ((arithmetic logic unit (ALU)), модуль управления и несколько регистров. В следующем аспекте процессор может содержать одно или несколько процессорных ядер и, следовательно, представлять собой либо одноядерный процессор, обычно способный обрабатывать один конвейер команд, либо многоядерный процессор, который может обрабатывать одновременно множество конвейеров команд. В другом аспекте процессор может быть реализован в виде одной интегральной схемы, двух или более интегральных схем либо может быть компонентом многокристального модуля (например, модуля, в котором кристаллы индивидуальных микропроцессоров могут быть смонтированы в одном корпусе интегральной схемы и, следовательно, совместно использовать одно гнездо (сокет)).

На фиг. 1 представлена диаграмма компонентов высокого уровня, составляющих пример компьютерной системы, согласно одному или более аспектам настоящего изобретения. Компьютерная система 100 может содержать процессор 102 для использования исполнительных модулей, имеющих в составе логические устройства, для осуществления алгоритмов обработки данных в соответствии с рассматриваемыми здесь вариантами. Система 100 является представителем систем обработки данных на основе микропроцессоров типов PENTIUM III™, PENTIUM 4™, Xeon™ и/или Itanium, выпускаемых корпорацией «Интел» в г. Санта-Клара, Калифорния (Intel Corporation of Santa Clara, California), хотя могут быть также использованы и другие системы (включая персональные компьютеры на основе других микропроцессоров, инженерные рабочие станции, приставки и другие подобные устройства). В другом варианте система 100, служащая примером, исполняет версию операционной системы WINDOWS™, разработанной корпорацией «Майкрософт» из г. Редмонд, шт. Вашингтон (Microsoft Corporation of Redmond, Washington), хотя могут быть использованы и другие операционные системы (например, UNIX и Linux), встроенное программное обеспечение и/или графические интерфейсы пользователя. Таким образом, рассматриваемые здесь варианты не ограничиваются каким-либо конкретным сочетанием аппаратуры и программного обеспечения.

Варианты изобретения не ограничиваются компьютерными системами. Альтернативные варианты описываемых здесь систем и способов могут быть использованы в других устройствах, таких как ручные устройства и встроенные приложения. Среди некоторых примеров таких устройств можно указать сотовые телефоны, устройства Интернет-протокола, цифровые видео камеры, персональные цифровые помощники (PDA) и ручные персональные компьютеры. Встроенные приложения могут представлять собой микроконтроллер, цифровой процессор сигнала (digital signal processor (DSP)), систему на кристалле, сетевые компьютеры (network computers (NetPC)), приставки, сетевые концентраторы, коммутаторы глобальных сетей связи (wide area network (WAN)) или какие-либо другие системы, которые могут выполнять одну или несколько команд в соответствии по меньшей мере с одним из вариантов.

В этом иллюстрируемом варианте процессор 102 содержит один или более исполнительных модулей 108 для осуществления алгоритма, иными словами для выполнения по меньшей мере одной команды. Один из вариантов может быть рассмотрен в контексте однопроцессорного настольного компьютера или серверной системы, но альтернативные варианты могут входить в многопроцессорную систему. Система 100 является примером системной архитектуры «концентратора» (‘hub’). Компьютерная система 100 содержит процессор 102 для обработки сигналов данных. Этот процессор 102, в качестве одного иллюстративного примера может представлять собой микропроцессор компьютера с полным набором команд (complex instruction set computer (CISC)), микропроцессор компьютера с сокращенным набором команд (reduced instruction set computing (RISC)), микропроцессор с очень длинным командным словом (very long instruction word (VLIW)), процессор, реализующий сочетание наборов команд, или какое-либо другое процессорное устройство, такое как цифровой процессор сигнала, например. Процессор 102 соединен с шиной 110 процессора, осуществляющей передачу сигналов данных между этим процессором 102 и другими компонентами системы 100. Элементы системы 100 (например, графический ускоритель 112, концентратор 116 контроллера памяти, запоминающее устройство 120, концентратор 130 контроллера ввода/вывода, радио приемопередатчик 126, флэш-BIOS 128, контроллер 134 сети, аудио контроллер 136, последовательный порт 138 расширения, контроллер 140 ввода/вывода и т.д.) осуществляют свои обычные функции, хорошо известные всем, кто достаточно знаком с рассматриваемой областью.

В одном из вариантов процессор 102 содержит внутренний кэш 104 Уровня 1 (Level 1 (L1)). В зависимости от архитектуры процессор 102 может иметь один внутренний кэш или несколько уровней внутренних кэшей. Другие варианты содержат сочетание внутренних и внешних кэшей в зависимости от конкретной реализации потребностей. Регистровый файл 106 служит для хранения различных типов данных в разнообразных регистрах, включая целочисленные регистры, регистры с плавающей запятой, векторные регистры, банки регистров, теневые регистры, регистры контрольных точек, регистры состояния и регистр указателя команд.

Исполнительный модуль 108, содержащий логические устройства для осуществления целочисленных операций и операций с плавающей запятой, также располагается в процессоре 102. Этот процессор 102 в одном из вариантов содержит ПЗУ (ROM) микрокода (μcode) для сохранения микрокода, при выполнении которого происходит осуществление алгоритмов для некоторых макрокоманд или обработка сложных сценариев. Здесь микрокод является потенциально обновляемым для обработки логических ошибок/исправлений в процессоре 102. В одном из вариантов исполнительный модуль 108 содержит логические устройства для обработки набора 109 команд для упакованных данных. Включив набор 109 команд для обработки упакованных данных в набор команд процессора 102 общего назначения вместе с ассоциированной схемой для выполнения этих команд, можно операции, применяемые многими приложениями мультимедиа, выполнить с использованием упакованных данных в процессоре 102 общего назначения. Таким образом, происходит ускорение и более эффективное выполнение многих приложений мультимедиа с использованием полной ширины шины данных процессора для осуществления операций с упакованными данными. Это потенциально устраняет необходимость передавать блоки данных меньшего размера по шине данных процессора с целью выполнения одной или более операций, по одному элементу данных за один раз. Альтернативные варианты исполнительного модуля 108 могут быть также использованы в микроконтроллерах, встроенных процессорах, графических устройствах, процессорах DSP и логических схемах других типов.

В некоторых вариантах процессор 102 может дополнительно содержать нижний регистр 421 защиты памяти стека, верхний регистр 423 защиты памяти стека и логическую схему 150 проверки адреса возврата. В одном иллюстративном примере процессор 102 может иметь пару регистров защиты памяти стека для каждого из двух или более режимов работы, например режима 32-разрядного пользователя, режим 64-разрядного пользователя режим супервизора. Функционирование этого логического устройства 150 проверки адреса возврата подробно описано ниже.

Система 100 содержит запоминающее устройство 120. Это запоминающее устройство 120 может представлять собой динамическое запоминающее устройство с произвольной выборкой (DRAM), статическое запоминающее устройство с произвольной выборкой (SRAM), устройство флэш-памяти или другое запоминающее устройство. Запоминающее устройство 120 сохраняет команды 121 и/или данные 123, представленные сигналами данных, для выполнения процессором 102. В некоторых вариантах совокупность команд 121 может содержать команды, используемые логическим устройством 150 проверки адреса возврата для обнаружения попыток нарушить границы защиты стека, как более подробно описано ниже.

Кристалл 116 логической интегральной схемы системы соединен с шиной 110 процессора и запоминающим устройством 120. Этот кристалл 116 логической интегральной схемы системы в иллюстрируемом варианте представляет собой концентратор контроллера памяти (memory controller hub (МСН)). Процессор 102 может осуществлять связь с концентратором МСН 116 через шину 110 процессора. Концентратор МСН 116 создает тракт 118 обращения к памяти с очень широкой полосой пропускания к запоминающему устройству 120 для сохранения команд и данных и для сохранения графических команд, данных и текстур. Концентратор МСН 116 предназначен для передачи сигналов данных между процессором 102, запоминающим устройством 120 и другими компонентами системы 100 и для выполнения функций моста для передачи сигналов данных между шиной 110 процессора, запоминающим устройством 120 и модулем 122 ввода/вывода системы. В некоторых вариантах кристалл 116 логической интегральной схемы системы может создавать графический порт для соединения с графическим контроллером 112. Концентратор МСН 116 соединен с запоминающим устройством 120 через интерфейс 118 памяти. Графическая карта 112 соединена с концентратором МСН 116 через соединение 114 ускоренного графического порта (Accelerated Graphics Port (AGP)).

Система 100 использует собственную шину 122 интерфейса концентратора для соединения концентратора МСН 116 с концентратором 130 контроллера ввода/вывода (I/O controller hub (ICH)). Концентратор ICH 130 предоставляет прямые соединения для некоторых устройств ввода/вывода через локальную шину ввода/вывода. Эта локальная шина ввода/вывода представляет собой высокоскоростную шину ввода/вывода для соединения периферийных устройств с запоминающим устройством 120, чипсетом и процессором 102. К некоторым примерам относятся аудио контроллер, концентратор 128 с встроенным программным обеспечением (флэш-BIOS) 128, радио приемопередатчик 126, запоминающее устройство 124 данных, контроллер ввода/вывода известных устройств, содержащий интерфейсы ввода пользователя и клавиатуры, последовательный порт расширения, такой как (Universal Serial Bus (USB)), и контроллер 134 сети. Запоминающее устройство 124 данных может содержать накопитель на жестком диске, дисковод для дискет, устройство CD-ROM, устройство флэш-памяти или другое запоминающее устройство большой емкости. Запоминающее устройство 124 данных может сохранять исполняемые команды для выполнения процессором 102. В некоторых вариантах совокупность команд 121 может содержать команды, используемые логическим устройством 150 проверки адреса возврата для обнаружения попыток нарушить границы защиты стека, как более подробно описано ниже.

Для другого варианта системы команда согласно одному из вариантов может быть использована в системе на кристалле. Один из вариантов системы на кристалле содержит процессор и запоминающее устройство. Запоминающее устройство для одной такой системы представляет собой флэш-память. Эта флэш-память может располагаться на том же кристалле, где выполнены процессор и другие компоненты системы. Кроме того, в составе этой системы на кристалле могут находиться и другие логические блоки, такие как контроллер памяти или графический контроллер.

На фиг. 2 представлена блок-схема микроархитектуры процессора 200, содержащего логические схемы и устройства для выполнения команд согласно одному или более аспектам настоящего изобретения. В некоторых вариантах команда согласно одному из вариантов может быть реализована для оперирования с элементами данных, имеющими размер один байт, слово, двойное слово, счетверенное слово и т.д., равно как с различными типами данных, такими как целочисленные данные с обычной и с удвоенной точностью и данные с плавающей запятой, также с обычной и с удвоенной точностью. В одном из вариантов работающий по порядку команд входной блок 201 является частью процессора 200, которая осуществляет выборку команд для исполнения и подготовку этих команд к использованию в процессорном конвейере в дальнейшем. Этот входной блок 201 может содержать несколько модулей. В одном из вариантов блок 226 упреждающей выборки команд выбирает команды из запоминающего устройства и передает их в декодер 228 команд, который, в свою очередь, декодирует или интерпретирует эти команды. Например, в одном из вариантов этот декодер осуществляет декодирование полученной им команды и преобразует ее в одну или несколько операций, именуемых «микрокомандами» или «микрооперациями» (также обозначаемыми как μop), так что машина может выполнить эти микрооперации. В других вариантах декодер анализирует команду и разбивает ее на код операции (opcode) и соответствующие данные и поля управления, используемые микроархитектурой для выполнения операций в соответствии с одним из вариантов. В одном из вариантов трассовый кэш 230 принимает декодированные микрооперации и собирает из них упорядоченные программные последовательности или трассы в очереди 234 микроопераций для исполнения. Когда трассовый кэш 230 сталкивается с комплексной командой, ROM 232 микрокодов выдает микрооперации, необходимые для выполнения соответствующей операции.

Некоторые команды преобразуются в одну микрооперацию, тогда как другие нуждаются во множестве микроопераций для выполнения полной операции. В одном из вариантов, если для выполнения команды нужно больше четырех микроопераций, декодер 228 обращается в ROM 232 микрокодов, чтобы выполнить команду. В некоторых вариантах команда может быть декодирована и преобразована в небольшое число микроопераций для обработки в декодере 228 команд. В другом варианте, если для выполнения операции требуется целый ряд микроопераций, эта команда может быть сохранена в ROM 232 микрокодов. Трассовый кэш 230 обращается в точку входа программируемой логической матрицы (programmable logic array (PLA)) для определения правильного указателя микрокоманды с целью считывания из ROM 232 микрокодов последовательностей микрокодов для завершения выполнения одной или нескольких команд согласно одному из вариантов. После того как ROM 232 микрокодов завершит построение последовательности микроопераций для выполнения какой-либо команды, входной блок 201 машины возобновляет выборку микроопераций из трассового кэша 230.

Механизм 203 внеочередного выполнения команд представляет собой блок, в котором производится подготовка команд к выполнению. Логическая схема для выполнения команд не по порядку содержит ряд буферов для «сглаживания» и переупорядочения потока команд с целью оптимизации работы системы, когда эти команды проходят по конвейеру, и происходит их планирование для исполнения. Логическая схема распределителя назначает буферы и ресурсы машины, которые нужны каждой микрооперации для выполнения. Логическая схема совмещения регистров отображает логические регистры на входы в регистровый файл. Распределитель назначает также вход для каждой микрооперации в одну из двух очередей микроопераций, одну очередь для операций, требующих обращения к памяти, и одну очередь для операций, не требующих обращения к памяти, перед планировщиками команд: планировщиком памяти, быстрым планировщиком 202, планировщиком 204 для медленных/обычных операций с плавающей запятой и простым планировщиком 206 операций с плавающей запятой. Планировщики 202, 204, 206 микроопераций определяют, когда микрооперация готова к выполнению, на основе готовности зависимых регистровых источников входных операндов для этой микрооперации и доступности исполнительных ресурсов, которые нужны для выполнения соответствующих микроопераций. Быстрый планировщик 202 в одном из вариантов может планировать в каждой половине главного тактового периода, тогда как другие планировщики могут осуществлять планирование один раз в каждом главном тактовом периоде процессора. Эти планировщики принимают «арбитражное» решение относительно диспетчирования портов при планировании микроопераций для исполнения.

Между планировщиками 202, 204, 206 и исполнительными модулями 212, 214, 216, 218, 220, 222, 224 в исполнительном блоке 211 располагаются физические регистровые файлы 208, 210. Система имеет раздельные регистровые файлы 208, 210 для целочисленных операций и операций с плавающей запятой соответственно. Каждый регистровый файл 208, 210 в одном из вариантов содержит также схему обхода, направляющую только что полученные результаты, которые еще не были записаны в регистровый файл, к новым зависимым микрооперациям. Регистровый файл 208 для целочисленных операций и регистровый файл 210 для операций с плавающей запятой могут также передавать данные один другому. В одном из вариантов регистровый файл 208 для целочисленных операций разделен на два отдельных регистровых файла, один регистровый файл для 32 младших разрядов (битов) данных и второй регистровый файл для 32 старших разрядов (битов) данных. В одном из вариантов регистровый файл 210 для операций с плавающей запятой имеет входы шириной 128 бит, поскольку команды с плавающей запятой обычно имеют операнды шириной от 64 до 128 бит.

Исполнительный блок 211 содержит исполнительные модули 212, 214, 216, 218, 220, 222, 224, где реально происходит выполнение команд. Эта секция содержит регистровые файлы 208, 210, сохраняющие величины целочисленных операндов и операндов с плавающей запятой, которые нужны для выполнения микрокоманд. Процессор 200 в одном из вариантов содержит ряд исполнительных модулей: модуль генератора адреса (address generation unit (AGU)) 212, генератор AGU 214, быстрое ALU 216, быстрое ALU 218, медленное ALU 220, ALU 222 с плавающей запятой, модуль 224 перемещения плавающей запятой. В одном из вариантов исполнительные модули 222, 224 с плавающей запятой выполняют операции с плавающей запятой, операции мультимедийного расширения ММХ, операции в формате одна команда-множество данных (SIMD), операции с потоковыми SIMD-расширениями (SSE) или другие операции. ALU 222 с плавающей запятой в одном из вариантов содержит делитель с плавающей запятой 64-разрядного числа на 64-разрядное число для выполнения микроопераций деления, вычисления корня квадратного и определения остатка. Для описываемых здесь систем и способов обработку команд, содержащих величины с плавающей запятой, может осуществлять аппаратура для операций с плавающей запятой. В одном из вариантов операции ALU передают в исполнительные модули 216, 218 высокоскоростных ALU. Эти быстрые ALU 216, 218 в одном из вариантов могут выполнять быстрые операции с эффективной задержкой в половину тактового периода. В одном из вариантов более сложные целочисленные операции передают в медленное ALU 220, поскольку это медленное ALU 220 содержит аппаратуру для выполнения целочисленных операций, связанных с большой задержкой, таких как умножение, сдвиг, определение флага и ветвление. Операции загрузки/сохранения в памяти выполняются генераторами AGU 212, 214 адресов. В одном из вариантов целочисленные ALU 216, 218, 220 описаны в контексте выполнения целочисленных операций над 64-разрядными операндами данных. В альтернативных вариантах эти ALU 216, 218, 220 могут быть реализованы для поддержки различной разрядности данных, и в том числе 16 бит, 32, 128, 256 бит и т.д. Аналогично модули 222, 224 для операций с плавающей запятой могут быть реализованы для поддержки работы с операндами с различной разрядностью. В одном из вариантов модули 222, 224 для операций с плавающей запятой могут оперировать с упакованными операндами данных шириной 128 бит в сочетании с командами SIMD и мультимедийными командами.

В одном из вариантов планировщики 202, 204, 206 микроопераций распределяют (диспетчируют) зависимые операции прежде, чем будет закончено выполнение первичной («родительской») нагрузки. Поскольку планирование и выполнение микроопераций в процессоре 200 осуществляется на основе гипотез, этот процессор 200 содержит также логические схемы и устройства для обработки промахов в памяти. В случае промаха поиска нагрузки данных в кэше данных возможно наличие в конвейере зависимых операций в стадии выполнения, которые предоставили планировщику временно неправильные данные. Механизм повторного выполнения отслеживает и повторно выполняет команды, использовавшие неправильные данные. Зависимые операции должны быть выполнены повторно, а независимым операциям дают возможность завершиться. Планировщики и механизм повторного выполнения в одном из вариантов процессора рассчитаны также для «вылавливания» последовательностей команд для выполнения операций сравнения текстовых строк.

Термин «регистры» может относиться к расположенным в составе процессора областям памяти, используемым как часть команд для идентификации операндов. Другими словами, регистры могут быть используемыми извне процессора (с точки зрения программиста). Однако понятие регистров в каком-либо варианте не следует ограничивать каким-либо конкретным типом схем. Напротив, регистры в любом варианте способны сохранять и предоставлять данные и осуществлять описываемые здесь функции. Описываемые здесь регистры могут быть реализованы посредством схем внутри процессора с использованием различных способов, таких как выделенные физические регистры, динамически назначаемые физические регистры с использованием наложения регистров, сочетания выделенных и динамически назначаемых физических регистров и т.п. В одном из вариантов целочисленные регистры сохраняют 32-разрядные целочисленные данные. Регистровый файл в одном из вариантов содержит также восемь мультимедийных SIMD-регистров для упакованных данных. Для последующего обсуждения под регистрами понимают регистры данных, рассчитанные на хранение упакованных данных, такие как 64-разрядные ММХ-регистры (также называемые в некоторых случаях ‘mm’-регистрами) в микропроцессорах, поддерживающих технологию ММХ™, от корпорации «Интел» (Intel Corporation). Эти ММХ-регистры, доступные и в форме целочисленных регистров, и в форме регистров для чисел с плавающей запятой, могут работать с упакованными элементами данных, сопровождающими команды SIMD и SSE. Аналогично для хранения таких упакованных операндов данных могут быть использованы 128-разрядные ХММ-регистры, относящиеся к технологии SSE2, SSE3, SSE4 или выше (обобщенно именуемой “SSEx”). В одном из вариантов для хранения упакованных данных и целочисленных данных регистрам нет необходимости различать эти два типа данных. В одном из вариантов целочисленные данные и данные с плавающей запятой могут находиться в одном и том же регистровом файле или в разных регистровых файлах. Более того, в одном из вариантов данные с плавающей запятой и целочисленные данные могут находиться в разных регистрах или в одном и том же регистре.

На фиг. 3a-3b схематично показаны элементы микроархитектуры процессора согласно одному или более аспектам настоящего изобретения. Как показано на фиг. 3a, конвейер 400 процессора содержит ступень 402 выборки, ступень 404 декодирования длины, ступень 406 декодирования, ступень 408 распределения, ступень 410 переименования, ступень 412 планирования (также известная как ступень диспетчирования или выпуска), ступень 414 чтения регистров/чтения памяти, ступень 416 выполнения, ступень 418 обратной записи/записи в память, ступень 422 обработки исключений и ступень 424 завершения.

На фиг. 3b стрелками показаны связи между двумя или более модулями, а направление стрелок указывает направление потока данных между этими модулями. На фиг. 3b показано процессорное ядро 490, содержащее входной блок 430, соединенный с модулем 450 механизма выполнения, причем и входной блок, и модуль механизма исполнения связаны с модулем 470 памяти.

Ядро 490 может представлять собой ядро процессора с сокращенным набором команд (RISC), ядро процессора с полным набором команд (CISC), ядро процессора с очень длинным командным словом (VLIW) либо ядро гибридного или альтернативного типа. В качестве еще одной опции ядро 490 может представлять ядро специального назначения, такое как сетевое ядро или ядро связи, механизм сжатия данных, графическое ядро или другое подобное ядро.

Входной блок 430 содержит модуль 432 прогнозирования ветвления, соединенный с модулем 434 кэша команд, который связан с буфером 436 динамической трансляции (translation lookaside buffer (TLB)) команд. Этот буфер соединен с модулем 438 выборки команд, который соединен с модулем 440 декодера. Модуль декодера или декодер может декодировать команды и генерировать на выходе одну или несколько микроопераций, входных точек микрокода, микрокоманд, других команд или других сигналов управления, декодированных из исходных команд, или отражающих исходные команды другим способом, или полученных из исходных команд. Декодер может быть реализован с использованием разнообразных механизмов. К примерам таких разнообразных механизмов относятся, не ограничиваясь этим, преобразовательные таблицы, аппаратные схемы, программируемые логические матрицы (PLA), ROM микрокода и т.п. Модуль 434 кэша команд дополнительно соединен с модулем 476 кэша уровня 2 (L2) в составе модуля 470 памяти. Модуль 440 декодер