Микросхема goa для совместного возбуждения электрода затвора и общего электрода, схема возбуждения и матрица

Иллюстрации

Показать всеИзобретение предлагает микросхему GOA (gate driver on array) для совместного возбуждения электрода затвора и общего электрода дисплея с матрицей. Технический результат заключается в снижении проходного напряжения для повышения качества шкалы серого на дисплее. Микросхема включает пусковую схему, первую избирательную входную схему, вторую избирательную входную схему, которая используется для пропускания соответственно входного сигнала высокого уровня для общего электрода и входного сигнала высокого уровня для электрода затвора на выход синхронизации пусковой схемы в разные временные последовательности, чтобы поднять напряжение на выходном выводе пусковой схемы, третью избирательную входную схему, которая используется для выбора сигналов уровня или сигналов фронта на линии затворов n+1 и линии затворов n+4 в качестве сигнала на перезапуск пусковой схемы, четвертую избирательную входную схему, которая используется для того, чтобы понизить напряжение на ней, избирательную выходную схему, вход которой соединен с выходным выводом пусковой схемы, для избирательного вывода сигнала возбуждения электрода затвора или сигнала возбуждения общего электрода. 3 н. и 14 з.п. ф-лы, 7 ил.

Реферат

Область техники

Настоящее изобретение относится к технической области жидкокристаллических дисплеев и, в частности, к микросхеме GOA для совместного возбуждения электрода затвора и общего электрода, к схеме драйвера и к матрице.

Предпосылки для создания изобретения

Технология GOA, то есть "драйвера затворов на матрице", является технологией, согласно которой схемы драйверов затворов (ИС драйверов затворов) изготавливаются непосредственно на подложке матрицы (матрица), вместо того, чтобы монтировать на последней отдельную кремниевую пластину. В результате применения этой технологии схема драйвера затвора может быть изготовлена непосредственно на периферии панели, что уменьшает объем производственных операций и снижает себестоимость изделия. Помимо этого, еще больше повышается степень интеграции TFT-LCD панели, что еще больше уменьшает толщину панели.

Однако при двухуровневом возбуждении в разных проходных напряжениях преобладает проходное напряжение, генерируемое паразитной емкостью Cgd. Поэтому в случае двухуровневого возбуждения напряжение общего электрода необходимо регулировать, чтобы улучшить качество шкалы серого.

Когда общий электрод СОМ возбуждается постоянным током, проходное напряжение, подаваемое на Cgd, равно:

(Vg_high-Vg_low)*Cgd/(Cgd+Clc+Cs),

где Vg_high и Vg_low соответственно представляют напряжения для размыкания и замыкания металлических дорожек драйвера затвора, и Cgd, Clc и Cs соответственно являются паразитной емкостью тонкопленочного транзистора (ТПТ), емкостью жидкого кристалла и емкостью запоминающего конденсатора.

Поскольку проходное напряжение в основном вызвано снижением пиксельного напряжения при изменении напряжения затвора в случае замыкания ТПТ посредством паразитной емкости Cgd. Независимо от того, является ли пиксельное напряжение положительным или отрицательным, проходное напряжение всегда будет понижать пиксельное напряжение до отрицательного.

В известном уровне техники воздействие проходного напряжения можно уменьшить путем компенсации напряжения общего электрода. Но, поскольку емкость жидкого кристалла Clc не является фиксированным параметром, воздействие проходного напряжения нельзя устранить, регулируя напряжение возбуждения общего электрода, так что задачу улучшения качества изображения трудно выполнить.

В настоящее время есть необходимость предложить простую и осуществимую конструкцию микросхемы GOA для снижения и даже устранения проходного напряжения, чтобы повысить качество шкалы серого на дисплее.

Раскрытие изобретения

Для выполнения вышеуказанных технических задач настоящее изобретение предлагает микросхему GOA для совместного возбуждения электрода затвора и общего электрода, которая включает:

пусковую схему, включающую входной вывод, выход синхроимпульсов, выход сигналов на перезапуск, входной вывод сигналов низкого уровня и выходной вывод пусковой схемы;

первую избирательную входную схему, включающую два обратных отключающих диода, соединенных параллельно, при этом аноды этих диодов соответственно соединены с выходами линии затворов n-1 и линии затворов n+2, и катоды диодов используются в качестве выходов для соединения с входным выводом, чтобы выбирать сигналы уровня или сигналы фронта в линии затворов n-1 и линии затворов n+2 в качестве сигнала входного воздействия пусковой схемы;

вторую избирательную входную схему, выход которой соединен с выводом синхронизации, включающую четыре входа для синхроимпульсов, которые имеют один и тот же цикл, но работают асинхронно, вход высокого уровня для общего электрода и вход высокого уровня для электрода затвора, чтобы соответственно пропускать входной сигнал высокого уровня для общего электрода и входной сигнал высокого уровня для электрода затвора на выход синхроимпульсов пусковой схемы при разных временных последовательностях, чтобы поднять напряжение на выходном выводе пусковой схемы;

третью избирательную входную схему, включающую два обратных отключающих диода, соединенных параллельно, при этом аноды этих диодов соответственно соединены с выходами линии затворов n+1 и линии затворов n+4, и катоды диодов используются в качестве выходов для соединения с выходом перезапуска, чтобы выбирать сигналы уровня или сигналы фронта на линии затворов n+1 и линии затворов n+4 в качестве сигнала на перезапуск пусковой схемы;

четвертую избирательную входную схему, выход которой соединен с входным выводом низкого уровня, для пропускания соответственно входного сигнала низкого уровня для затвора или входного сигнала низкого уровня для общего электрода на входной вывод низкого уровня пусковой схемы под управлением сигналов на линии затворов n+1 и линии затворов n+4, чтобы понизить напряжение на ней;

избирательную выходную схему, вход которой соединен с выходным выводом пусковой схемы, для избирательного вывода сигнала возбуждения затвора или сигнала возбуждения общего электрода в двух из четырех последовательности синхроимпульсов, имеющих один и тот же цикл и работающих асинхронно. Эти две последовательности импульсов имеют разницу в 3/4 рабочего цикла.

Согласно одному варианту осуществления настоящего изобретения каждый обратный отключающий диод является схемой, эквивалентной диоду, состоящему из МОП-транзистора или ТПТ-транзистора, причем затвор МОП-транзистора или ТПТ-транзистора соединен с его истоком, чтобы служить в качестве анода, и сток используется в качестве катода.

Согласно одному варианту осуществления настоящего изобретения сигналы уровня или сигналы фронта в линии затворов n-1 и линии затворов n+2 являются сигналами низкого уровня или сигналами заднего фронта, и сигналы уровня или сигналы фронта на линии затворов n+1 и линии затворов n+4 являются сигналами высокого уровня или сигналами переднего фронта.

Согласно одному варианту осуществления настоящего изобретения четыре входа для синхроимпульсов, имеющие один и тот же цикл и работающие асинхронно, последовательно отличаются по фазе на 1/4 рабочего цикла.

Согласно одному варианту осуществления настоящего изобретения выходной возбуждающий сигнал для общего электрода микросхемы GOA синхронизируется с сигналом на линии затворов n+3.

Согласно одному варианту осуществления настоящего изобретения вторая избирательная входная схема включает четыре ТПТ-транзистора, у которых истоки и стоки двух ТПТ-транзисторов соединены, и два затвора работают под управлением соответственно второго входа для синхроимпульсов и третьего входа для синхроимпульсов для введения входного сигнала высокого уровня для электрода затвора;

истоки и стоки двух других ТПТ-транзисторов соединены, и два затвора работают под управлением соответственно первого входа для синхронизирующих импульсов и четвертого входа для синхроимпульсов, для введения входного сигнала высокого уровня для общего электрода.

Согласно одному варианту осуществления настоящего изобретения четвертая избирательная входная схема включает два ТПТ-транзистора, затворы которых соединены соответственно с выходами линий затворов n+1 и n+4, и истоки соединены соответственно с входным сигналом низкого уровня для затвора и входным сигналом низкого уровня для общего электрода.

Согласно одному варианту осуществления настоящего изобретения избирательная выходная схема включает два ТПТ-транзистора, два затвора которых работают под управлением соответственно третьего входа для синхроимпульсов и первого входа для синхроимпульсов, и два истока вместе соединены с выходным выводом пусковой схемы, чтобы соответственно выводить сигналы линии затворов n и линии общего электрода n+3 при разных временных последовательностях.

Согласно одному аспекту настоящего изобретения также предложена схема возбуждения для панели дисплея, включающая некоторое число любых из вышеописанных микросхем GOA, причем микросхемы GOA расположены каскадом в следующем порядке:

выходные сигналы линий затворов n-1 и n+2 используются соответственно в качестве сигналов для пусковой схемы для этого уровня микросхем GOA; выходные сигналы линий затворов n+1 и n+4 используются соответственно в качестве сигналов на перезапуск для этого уровня микросхем GOA; четыре линии синхронизации соединены соответственно с входами для синхронизирующих импульсов второй избирательной входной схемы для этого уровня микросхем GOA, чтобы подавать синхроимпульсы в одном цикле, но в разной фазе; и входной сигнал высокого уровня для электрода затвора и входной сигнал высокого уровня для общего электрода вводятся соответственно при разных синхроимпульсах, чтобы выводить разные повышающие напряжения;

причем выходные сигналы микросхем GOA этого уровня включают выходные сигналы линии затворов n и линии общего электрода n+3.

Согласно еще одному аспекту настоящего изобретения также предложена матрица с размещенной на ней схемой возбуждения, которая описана выше, причем матрица включает:

линии затворов и линию общего электрода, которые расположены параллельно в поперечном направлении; и

линию входных сигналов синхронизации, линию входных сигналов высокого и низкого уровней для затворов и линию входных сигналов высокого и низкого уровней для общего электрода, которые расположены параллельно в продольном направлении, причем соответствующие параллельные выходы линии затворов и линии общего электрода имеют разницу в имеют разницу в три уровня в каскадном расположении или в 3/4 рабочего цикла на временной последовательности.

Согласно настоящему изобретению, поскольку выходной сигнал напряжения СОМ (для общего электрода) синхронизируется с выходным сигналом GATE (для затворов), и изменение напряжения прямо противоположно напряжению затворов по направлению, происходит эффективное противодействие проходному напряжению, за счет чего улучшается качество шкалы серого дисплея.

Другие признаки и преимущества настоящего изобретения будут изложены ниже в описании и станут частично очевидными из описания или будут поняты при реализации настоящего изобретения. Цели и другие преимущества настоящего изобретения могут быть достигнуты и получены в конструкциях, конкретно указанных в описании, пунктах формулы изобретения и на прилагаемых чертежах.

Краткое описание чертежей

Прилагаемые чертежи предназначены для более глубокого понимания настоящего изобретения являются частью описания и служат для объяснения настоящего изобретения вместе с примерами осуществления настоящего изобретения, но не ограничивают настоящее изобретение. На прилагаемых чертежах:

Фиг. 1 - форма волны напряжения возбуждения общего электрода постоянным током из известного уровня техники, при этом запоминающая емкость Cs (Cs на Com) выполнена на общем электроде;

Фиг. 2 - принципиальная схема микросхемы GOA из известного уровня техники;

Фиг. 3 - схема каскадного расположения микросхем GOA для формирования двухуровневого возбуждения затворов из известного уровня техники;

Фиг. 4 - последовательность импульсов схемы драйвера затворов из известного уровня техники;

Фиг. 5 - формы волны напряжения, разрешающей схеме возбуждения общего электрода синхронизироваться со схемой возбуждения затворов согласно одному аспекту настоящего изобретения;

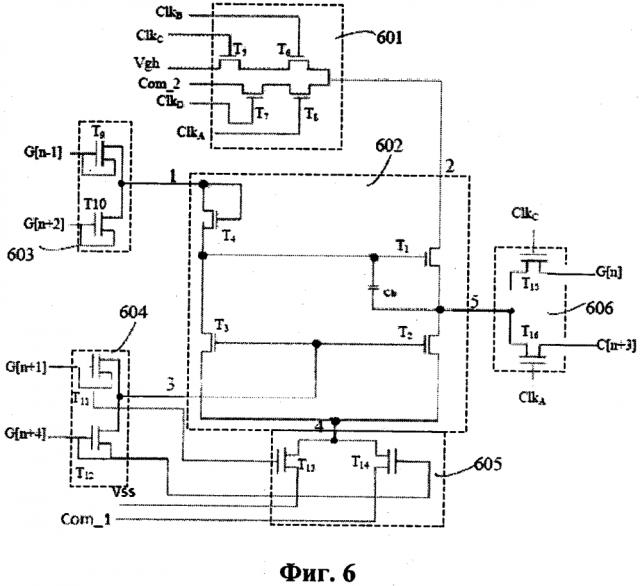

Фиг. 6 - принципиальная схема микросхемы GOA, интегрирующей выходной сигнал возбуждения общего электрода согласно одному варианту осуществления настоящего изобретения; и

Фиг. 7 - схема последовательности импульсов возбуждения, генерируемых каскадными схемами возбуждения согласно идее настоящего изобретения.

Подробное описание вариантов осуществления

Варианты осуществления настоящего изобретения будут подробно объяснены ниже в связи с прилагаемыми чертежами и примерами. Поэтому процесс использования технических средств настоящего изобретения для решения стоящих технических задач и достижения технического результата, может быть полностью понят и соответственно реализован. Следует сказать, что при отсутствии противоречия варианты осуществления настоящего изобретения и разные признаки из приведенных примеров могут быть объединены между собой, но полученные таким образом технические решения подпадают под объем охраны настоящего изобретения.

На Фиг. 1 - Фиг. 4 показана схема драйвера GOA из известного уровня техники и генерируемая ей последовательность импульсов. Можно видеть, что напряжение на общем электроде СОМ является напряжением постоянного тока. Импульсы напряжения на линиях затворов (Gate 1, Gate 2, Gate 3, …,) появляются последовательно под действием двух последовательностей синхроимпульсов в противофазе. Время сканирования всех линий затворов является длиной фрейма, который также является циклом импульсов на линиях затворов. Поскольку управление пусковой схемой реализуется двумя синхроимпульсами в противофазе, длительность положительного импульса на каждой линии затворов равна длительности синхроимпульса.

Также на Фиг. 1 показаны формы волны напряжения на каждой линии в один и тот же момент времени, где 101 - импульс напряжения возбуждения затвора, 102 - импульс напряжения возбуждения истока, 103 - напряжение на электроде пикселя и 104 - разница между напряжением истока и напряжением пикселя, причем эта разница равна проходному напряжению. Для того, чтобы устранить проходное напряжение, исходное напряжение СОМ 106 может быть скорректировано, и скорректированное напряжение СОМ обозначено числом 107. Эта коррекция равна значению проходного напряжения. Однако скорректировать исходное напряжение на общем электроде СОМ, который возбуждается постоянным током, трудно.

В известном уровне техники, как показано на Фиг. 3, схема возбуждения состоит их микросхем GOA, расположенных на одной стороне. Эти микросхемы GOA расположены каскадом, чтобы сформировать последовательность импульсов, которая показана на Фиг. 4, на их выходах. На Фиг. 2 также показана подробная принципиальная схема микросхемы GOA.

Как показано на Фиг. 2, микросхема GOA по существу является пусковой схемой. Она включает четыре переключающих ТПТ-транзистора (TFT) и один конденсатор, причем TFT1 является переключающим транзистором возбуждения, TFT2 и TFT3 - переключающими транзисторами перезапуска, и TFT4 - переключающим транзистором предварительной зарядки. Cb является конденсатором удержания напряжения TFT1, управляемым в основном транзистором TFT4. Традиционные возбуждающие микросхемы GOA должны иметь четыре управляющих сигнала, т.е., синхронизирующий сигнал Clk, входной сигнал, сигнал перезагрузки Reset и выходной сигнал низкого уровня Vss для затвора. Синхронизирующий сигнал является повышающим выходным сигналом с линии затворов.

На Фиг. 3 показана принципиальная схема микросхем GOA каскадного расположения для формирования одностороннего двухуровневого возбуждения затворов из известного уровня техники. Выходной сигнал предыдущей микросхемы GOA используется в качестве сигнала пусковой схемы для следующей микросхемы GOA, и выходной сигнал этой следующей микросхемы GOA используется в качестве сигнала перезапуска этой микросхемы GOA. Применяются два сигнала синхронизации (Vclk_A, Vclk_B), которые используются соответственно для микросхем GOA в нечетных рядах и микросхем GOA в четных рядах. Выходное напряжение на линии затворов Vss определяет высоту или амплитуду выходного импульса на линии затворов.

Как сказано выше, при этом напряжение общего электрода СОМ не регулируется, так что проходное напряжение не устраняется.

Ниже в настоящем описании изобретения будет объяснено, как регулировать напряжение СОМ в свете вышеупомянутого принципа. Как сказано выше, известно необходимое изменение напряжения СОМ, которое эквивалентно проходному напряжению. Поэтому получается временная последовательность, показанная на Фиг. 5. Подобно Фиг. 1, обозначение 501 представляет импульс напряжения возбуждения затвора, 502 - импульс напряжения возбуждения истока, 503 - напряжение на электроде пикселя, и 506 представляет сигнал возбуждения напряжения СОМ. На этой фигуре можно видеть, что в данном случае проходное напряжение теоретически полностью устраняется за счет изменения напряжения СОМ.

Согласно этой концепции может быть разработана схема возбуждения GOA. Основная микросхема GOA схемы возбуждения GOA показана на Фиг. 6.

Выходной сигнал микросхемы GOA используется для совместного возбуждения затвора и общего электрода. Схема состоит в основном из пусковой схемы 602 и некоторых периферических схем. Пусковая схема включает входной вывод 1, выход синхронизации 2, вывод перезапуска 3, входной вывод низкого уровня 4 и выходной вывод пусковой схемы 5.

Для того, чтобы разрешить пусковой схеме осуществлять совместное возбуждение общего электрода и возбуждение затвора, микросхема GOA также включает первую избирательную входную схему 603, которая включает два обратных отключающих диода, соединенных параллельно. Аноды диодов соединены соответственно с выходами G[n-1] и G[n+2] линий затворов n-1 и n+2, и катоды диодов используются в качестве выходов для соединения с входным выводом 1, чтобы выбирать сигналы уровня или сигналы фронта G[n-1] и G[n+2] с линий затворов n-1 и n+2 в качестве сигнала входного воздействия пусковой схемы 602.

Как показано на Фиг. 6, микросхема GOA также включает третью избирательную входную схему 604. Эта схема состоит из двух обратных отключающих диодов, также соединенных параллельно, при этом, подобно сказанному выше, аноды диодов соединены соответственно с выходами G[n+1] и G[n+4] линий затворов n+1 и n+4, и катоды диодов используются в качестве выходов для соединения с выходом перезапуска 3, чтобы выбирать сигналы уровня или сигналы фронта G[n+1] и G[n+4] с линий затворов n+1 и n+4 в качестве сигнала на перезапуск пусковой схемы 602.

В настоящем изобретении, как показано на Фиг. 6, сигналы уровня или сигналы фронта в линиях затворов n-1 и n+2, G[n-1] и G[n+2], являются сигналами низкого уровня или сигналами заднего фронта, и сигналы уровня или сигналы фронта на линиях затворов n+1 и n+4, G[n+1] и G[n+4], являются сигналами высокого уровня или сигналами переднего фронта.

На Фиг. 6 все диоды применяют эквивалентные схемы, состоящие из ТПТ-транзисторов, например, Т9-Т12, при этом затворы и истоки ТПТ-транзисторов соединены, чтобы служить в качестве анодов, и стоки используются в качестве катодов. Конечно, настоящее изобретение этим не ограничено, например, в эквивалентной схеме могут быть также применены МОП-транзисторы.

Микросхема GOA настоящего изобретения включает вторую избирательную входную схему 601. Выход второй избирательной входной схемы 601 соединен с выводом синхронизации 2 пусковой схемы, может включать четыре ввода синхроимпульсов ClkA, ClkB, ClkC, ClkD, имеющих один и тот же цикл и работающих асинхронно, вход высокого уровня Com_2 для общего электрода и вход высокого уровня Vgh для электрода затвора, и используется соответственно для пропускания входного сигнала высокого уровня для общего электрода Com_2 и входного сигнала высокого уровня Vgh для электрода затвора на выход синхронизации 2 пусковой схемы 602 при разных временных последовательностях, чтобы далее поднять напряжение на выходном выводе пусковой схемы 5, и сформировать выходной импульс высокого уровня для сканирования затворов на уровне n или импульс высокого уровня общего электрода на уровне n+3.

Более конкретно, вторая избирательная входная схема 601 в одном варианте осуществления может включать четыре ТПТ-транзистора, при этом истоки и стоки двух ТПТ-транзисторов Т5, Т6 соединены, и два затвора работают под управлением соответственно второго входа для синхроимпульса ClkB и третьего входа для синхроимпульса ClkC, чтобы получить доступ к входному сигналу высокого уровня для электрода затвора. Истоки и стоки двух других ТПТ-транзисторов Т7, Т8 соединены, и два затвора работают под управлением соответственно первого входа для синхроимпульса ClkA и четвертого входа для синхроимпульса ClkD, чтобы получить доступ к входному сигналу высокого уровня для общего электрода.

Предпочтительно четыре входа для синхронизирующих импульсов ClkA, ClkB, ClkC, ClkD, имеющие один и тот же цикл и работающие асинхронно, последовательно отличаются на 1/4 рабочего цикла по фазе. Таким образом, длительность выходного импульса линии затворов и длительность импульса линии общего электрода равны 1/2 длительности синхроимпульса.

Помимо этого, микросхема GOA также включает четвертую избирательную входную схему 605, выход которой соединен с входным выводом низкого уровня 4, для пропускания соответственно входного сигнала низкого уровня для затвора или входного сигнала низкого уровня для общего электрода на входной вывод низкого уровня 4 пусковой схемы 602 под управлением выходных сигналов G[n+1] и G[n+4] линий затворов n+1 и n+4, чтобы понизить напряжение на ней и сформировать низкий уровень выходного импульса сканирования затворов на уровне n или импульс низкого уровня общего электрода на уровне n+3.

В одном варианте осуществления четвертая избирательная входная схема 605 предпочтительно включает два ТПТ-транзистора Т13, Т14, причем их затворы соединены соответственно с выходами G[n+1] и G[n+4] линий затворов n+1 и n+4, и истоки соединены соответственно с входным сигналом низкого уровня для затвора Vss и входным сигналом низкого уровня для общего электрода Com_1.

Вход избирательной выходной схемы 606 микросхемы GOA соединен с выходным выводом пусковой схемы 5 для избирательного вывода сигнала возбуждения затвора или сигнала возбуждения общего электрода при двух временных последовательностях импульсов на четырех входах для синхронизирующих импульсов, имеющих один и тот же цикл и работающих асинхронно. Два импульса имеют разницу в 3/4 рабочего цикла, так что сигнал возбуждения затвора появляется раньше чем сигнал возбуждения общего электрода при трех длительностях импульсов линий затворов.

Как показано на Фиг. 6, сигнал возбуждения общего электрода С[n+3], выводимый микросхемой GOA на уровне n синхронизирован с сигналом G[n+3] на линии затворов n+3.

В одном варианте осуществления избирательная выходная схема 606 предпочтительно включает два ТПТ-транзистора Т15, Т16, при этом два затвора работают соответственно под управлением третьего входа для синхроимпульсов ClkC и первого входа для синхроимпульсов ClkA, и два истока вместе соединены с выходным выводом пусковой схемы 5, чтобы соответственно выводить выходной сигнал G[n] линии затворов n и выходной сигнал С[n+3] линии общего электрода n+3 при разных временных последовательностях.

На Фиг. 7 показана схема последовательности возбуждающих импульсов, генерируемых каскадными схемами возбуждения, согласно идее настоящего изобретения.

На этой фигуре можно видеть, что четыре входа для синхроимпульсов, имеющих один и тот же цикл и работающих асинхронно, последовательно отличаются на 1/4 рабочего цикла по фазе. Когда импульс появляется на линии затворов Gate1, импульс появляется на Com1, чем достигается синхронная работа по возбуждению затвора и возбуждению общего электрода.

Согласно одному аспекту настоящего изобретения также предложена схема возбуждения для панели дисплея, включающая некоторое множество вышеупомянутых микросхем GOA, при этом микросхемы GOA расположены каскадно в следующем порядке.

Выходной сигнал G[n-1] линии затворов n-1 и выходной сигнал G[n+2] линии затворов n+2 используются соответственно в качестве сигналов для пусковой схемы на этом уровне микросхем GOA, и выходной сигнал G[n+1] линии затворов n+1 и выходной сигнал G[n+4] линии затворов n+4 используются соответственно в качестве сигналов на перезапуск микросхем GOA этого уровня, четыре линии синхронизации соединены соответственно с входами для синхроимпульсов ClkA, ClkB, ClkC, ClkD на второй избирательной входной схеме микросхем GOA этого уровня, чтобы подавать сигналы синхронизации, имеющие один и тот же цикл, но разницу по фазе, и входной сигнал высокого уровня для затвора и входной сигнал высокого уровня для общего электрода пропускаются соответственно при разных синхронизирующих импульсах, чтобы выводить разные повышающие напряжения, при этом выходным сигналом микросхемы GOA на этом уровне является выходной сигнал G[n] линии затворов n и выходной сигнал С[n+3] линии общего электрода n+3.

Настоящее изобретение также предлагает подложку матрицы с выполненной на ней вышеописанной схемой возбуждения, включающей линию затворов и линию общего электрода, которые параллельны в поперечном направлении, и линию входных сигналов синхронизации, линию входных сигналов высокого и низкого уровней для затворов и линию входных сигналов высокого и низкого уровней для общего электрода, которые параллельны в продольном направлении, при этом выходные сигналы линии затворов и линии общего электрода имеют разницу в 3 рабочих цикла в каскадных положениях или 3/4 рабочего цикла на временной последовательности.

Хотя выше описаны варианты осуществления, они являются просто вариантами осуществления для облегчения понимания настоящего изобретения, а не для ограничения настоящего изобретения. Любые изменения или альтернативные решения, которые будут очевидны для специалистов в данной области техники после ознакомления с настоящим описанием, будут подпадать под объем настоящего изобретения. Соответственно, объем настоящего изобретения будет определяться прилагаемой формулой изобретения.

1. Микросхема GOA для совместного возбуждения электрода затвора и общего электрода, включающая:

пусковую схему, имеющую входной вывод, выход синхронизации, вывод перезапуска, входной вывод низкого уровня и выходной вывод пусковой схемы;

первую избирательную входную схему, включающую два обратных отключающих диода, соединенных параллельно, при этом аноды этих диодов соединены соответственно с выходами линии затворов n-1 и линии затворов n+2 и катоды диодов используются в качестве выходов для соединения с входным выводом, чтобы выбирать сигналы уровня или сигналы фронта на линии затворов n-1 и линии затворов n+2 в качестве сигнала входного воздействия пусковой схемы;

вторую избирательную входную схему, выход которой соединен с выходом синхронизации, включающую четыре входа для синхронизирующих импульсов, которые имеют один и тот же цикл, но работают асинхронно, вход высокого уровня для общего электрода и вход высокого уровня для электрода затвора, чтобы пропускать соответственно входной сигнал высокого уровня для общего электрода и входной сигнал высокого уровня для электрода затвора на выход синхронизации пусковой схемы в разных временных последовательностях, чтобы поднять напряжение на выходном выводе пусковой схемы;

третью избирательную входную схему, включающую два обратных отключающих диода, соединенных параллельно, при этом аноды этих диодов соединены соответственно с выходами линии затворов n+1 и линии затворов n+4 и катоды диодов используются в качестве выходов для соединения с выходом перезапуска, чтобы выбирать сигналы уровня или сигналы фронта на линии затворов n+1 и линии затворов n+4 в качестве сигнала на перезапуск пусковой схемы;

четвертую избирательную входную схему, выход которой соединен с входным выводом низкого уровня для пропускания соответственно входного сигнала низкого уровня для затвора и входного сигнала низкого уровня для общего электрода на входной вывод низкого уровня пусковой схемы под управлением сигналов на линии затворов n+1 и линии затворов n+4, чтобы понизить напряжение на ней; и

избирательную выходную схему, вход которой соединен с выходным выводом пусковой схемы для избирательной подачи сигнала возбуждения электрода затвора или сигнала возбуждения общего электрода в двух из четырех последовательностей синхронизирующих импульсов, имеющих один и тот же цикл и работающих асинхронно.

2. Микросхема GOA по п. 1, отличающаяся тем, что обратный отключающий диод является схемой, эквивалентной диоду, состоящей из МОП-транзистора или ТПТ транзистора, причем затвор МОП-транзистора или ТПТ-транзистора соединен с его истоком, чтобы служить в качестве анода, и сток используется в качестве катода.

3. Микросхема GOA по п. 1, отличающаяся тем, что сигналы уровня или сигналы фронта в линии затворов n-1 и линии затворов n+2 являются сигналами низкого уровня или сигналами заднего фронта и сигналы уровня или сигналы фронта на линии затворов n+1 и линии затворов n+4 являются сигналами высокого уровня или сигналами переднего фронта.

4. Микросхема GOA по п. 1, отличающаяся тем, что четыре входа для синхронизирующих импульсов, имеющих один и тот же цикл и работающих асинхронно, отличаются друг от друга в последовательности на 1/4 рабочего цикла по фазе.

5. Микросхема GOA по п. 1, отличающаяся тем, что сигнал возбуждения общего электрода, выводимый микросхемой GOA, синхронизирован с сигналом на линии затворов n+3.

6. Микросхема GOA по п. 5, отличающаяся тем, что вторая избирательная входная схема включает четыре ТПТ-транзистора,

при этом истоки и стоки двух ТПТ-транзисторов соединены друг с другом и два затвора работают под управлением соответственно второго входа для синхронизирующих импульсов и третьего входа для синхронизирующих импульсов для введения входного сигнала высокого уровня для электрода затвора; и истоки и стоки двух других ТПТ-транзисторов соединены друг с другом и два затвора работают под управлением соответственно первого входа для синхронизирующих импульсов и четвертого входа для синхронизирующих импульсов для введения входного сигнала высокого уровня для общего электрода.

7. Микросхема GOA по п. 5, отличающаяся тем, что четвертая избирательная входная схема включает два ТПТ-транзистора, затворы которых соединены соответственно с выходами линий затворов n+1 и n+4 и истоки которых соединены соответственно с входным сигналом низкого уровня для затвора и входным сигналом низкого уровня для общего электрода.

8. Микросхема GOA по п. 5, отличающаяся тем, что избирательная выходная схема включает два ТПТ-транзистора, два затвора которых работают под управлением соответственно третьего входа для синхроимпульсов и первого входа для синхроимпульсов и два истока которых вместе соединены с выходным выводом пусковой схемы, чтобы выводить соответственно сигналы линии затворов n и линии общего электрода n+3 в разные временные последовательности, при этом эти две последовательности импульсов имеют разницу в 3/4 рабочего цикла.

9. Схема для возбуждения панели дисплея, включающая некоторое множество микросхем GOA по п. 1, отличающаяся тем, что микросхемы GOA расположены каскадом в следующем порядке:

выходные сигналы линий затворов n-1 и n+2 используются соответственно в качестве сигналов пусковой схемы для этого уровня микросхем GOA, выходные сигналы линий затворов n+1 и n+4 используются соответственно в качестве сигналов на перезапуск для микросхем GOA этого уровня и четыре линии синхронизации соединены соответственно с входами для синхроимпульсов на второй избирательной входной схеме этого уровня микросхем GOA, чтобы подавать синхронизирующие сигналы с одним циклом, но в разных фазах, и входной сигнал высокого уровня для электрода затвора и входной сигнал высокого уровня для общего электрода вводятся соответственно при разных синхронизирующих импульсах, чтобы выводить разные повышающие напряжения;

при этом выходные сигналы для этого уровня микросхем GOA включают выходные сигналы линии затворов n и линии общего электрода n+3.

10. Схема по п. 9, отличающаяся тем, что обратный отключающий диод является схемой, эквивалентной диоду, состоящему из МОП-транзистора или ТПТ транзистора, причем затвор МОП-транзистора или ТПТ-транзистора соединен с его истоком, чтобы служить в качестве анода, и сток используется в качестве катода.

11. Схема по п. 9, отличающаяся тем, что сигналы уровня или сигналы фронта в линии затворов n-1 и линии затворов n+2 являются сигналами низкого уровня или сигналами заднего фронта и сигналы уровня или сигналы фронта на линии затворов n+1 и линии затворов n+4 являются сигналами высокого уровня или сигналами переднего фронта.

12. Схема по п. 9, отличающаяся тем, что четыре входа для синхронизирующих импульсов, имеющих один и тот же цикл и работающих асинхронно, отличаются друг от друга в последовательности на 1/4 рабочего цикла по фазе.

13. Схема по п. 9, отличающаяся тем, что сигнал возбуждения общего электрода, выводимый микросхемой GOA, синхронизирован с сигналом на линии затворов n+3.

14. Схема по п. 13, отличающаяся тем, что вторая избирательная входная схема включает четыре ТПТ-транзистора, при этом истоки и стоки двух ТПТ-транзисторов соединены друг с другом и два затвора работают под управлением соответственно второго входа для синхронизирующих импульсов и третьего входа для синхронизирующих импульсов для введения входного сигнала высокого уровня для электрода затвора; и

истоки и стоки двух других ТПТ-транзисторов соединены друг с другом, и эти два затвора работают под управлением соответственно первого входа для синхронизирующих импульсов и четвертого входа для синхронизирующих импульсов для введения входного сигнала высокого уровня для общего электрода.

15. Схема по п. 13, отличающаяся тем, что четвертая избирательная входная схема включает два ТПТ-транзистора, причем их затворы соединены соответственно с выходами линий затворов n+1 и n+4 и истоки соединены соответственно с входным сигналом низкого уровня для затвора и входным сигналом низкого уровня для общего электрода.

16. Схема по п. 13, отличающаяся тем, что избирательная выходная схема включает два ТПТ-транзистора, два затвора которых работают под управлением соответственно третьего входа для синхроимпульсов и первого входа для синхроимпульсов, и два истока которых вместе соединены с выходным выводом пусковой схемы, чтобы выводить соответственно сигналы линии затворов n и линии общего электрода n+3 в разные временные последовательности, при этом эти две последовательности импульсов имеют разницу в 3/4 рабочего цикла.

17. Матрица с размещенной на ней схемой по п. 9, включающая:

линию затворов и линию общего электрода, которые расположены параллельно в поперечном направлении; и

линию входных сигналов синхронизации, линию входных сигналов высокого и низкого уровней для затворов и линию входных сигналов высокого и низкого уровней для общего электрода, которые расположены параллельно в продольном направлении,

при этом соответствующие выходы линии затворов и линии общего электрода имеют разницу в три уровня в смысле каскадного расположения, или в 3/4 рабочего цикла на временной последовательности.