Логическая схема «и—не/и»

Иллюстрации

Показать всеРеферат

1

ОП ГСAНИЕ

ИЗОБРЕТЕНИЯ

262952

Союз Советских

Социалистических

Республик

К АВТОРСКОМУ СВИДЕТЕЛЬСТВУ

Зависимое от авт. свидетельства №

Заявлено 06.V Ill.1968 (№ 1263017/18-24) Кл. 21ат, 36/18 с присоединением заявки №

МПК Н 03k

УДК 681.325.65(088.8) Приоритет

Опубликовано 04.11.1970. Бюллетень № 7

Дата опубликования описания ЗЛ 1.1970

Комитет по делам изобретений и открытий при Совете Мииистрое

СССР

Авторы изобретения

А. Г. Филиппов и О, А. Ханджян

Заявитель

ЛОГИЧЕСКАЯ СХЕМА «И — И Е/И»

Предложенная логическая схема «И вЂ” НЕ/И» относится к динамическим элементам вычислительной техники и предназначена для использования в качестве универсального логического элемента в цифровых вычислительных устройствах.

Логические схемы «И — НЕ/И» динамического типа, содержащие входные диодные схемы

«И» и транзисторы, известны. Недостатком их является наличие индуктивностей, трансформаторов; сложность схемы либо зависимость

pàáoòû от постоянной времени накопления и рассасывания заряда в базе транзистора.

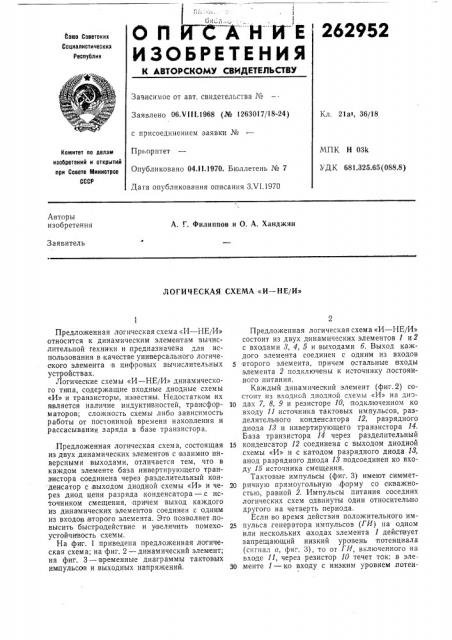

Предложенная логическая схема, состоящая из двух динамических элементов с взаимно инверсными выходами, отличается тем, что в каждом элементе база инвертирующего транзистора соединена через .разделительный конденсатор с,выходом диодной схемы «И» и через диод цепи разряда конденсатора — с источником смещения, причем выход каждого из динамических элементов соединен .с одним из входов imoporo элемента. Это позволяет,повысить быстродействие и увеличить помехоустойчивость схемы.

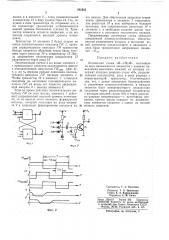

На фтсг. 1 приведена предложенная логическая схема; на фиг. 2 — динамический элемент; на фиг. 3 — временные диаграммы тактовых им пульсов и выходных напряжений.

Предложенная логическая схема «И вЂ” НЕ/И» состоит из двух динамических элементов I и 2 с входами 8, 4, 5 и выходами б. Выход каждого элемента соединен с одним из входов второго элемента, причем остальные входы элемента 2 подключены к источнику,постоянного питания.

Каждый динамический элемент (фиг. 2) состоит из входной диодной схемы «И» на диоl0 дах 7, 8, 9 и резисторе 10, подключенном ко входу 11 источника тактовых импульсов, разделительного конденсатора 12, разрядного диода 18 и инвертирующего транзистора 14.

База транзистора 14 через разделительный

15 конденсатор 12 соединена с выходом диодной схемы «И» и с катодом разрядного диода И, анод разрядного диода 13 подсоединен ко входу 15 источника смещения.

Тактовые импульсы (фиг. 3) имеют сим мет20 ричную прямоугольную, форму со сосважностью, равной 2. Импульсы питания соседних логических схем сдвинуты один относительно другого на четверть периода.

Если во время действия положительного им25 пульса, генератора импульсов (ГИ) па одном или нескольких входах элемента 1 действует запрещающий низкий уровень потенциала (спгнал а, фиг. 3), то оТ 1 И, включенного на входе 11, через резистор 10 течет ток:,в эле30 менте 1 — ко входу с низким уровнем,потен262952

9 ьг. t

Фиг. 2 ЪпелеЯ

Составитель Г. С. Колотова

Редактор Т. 3. Орловская

Техред А. А. Камышникова

Корректор С. М. Сигал

0 б

Типография, пр. Сапунова, 2 циала, а в элементе 2 — через разделительный конденсатор 12 в базу транзистора 14. Ток, текущий к базе транзистора 14, открывает его, и на коллекторе транзистора устанавливается низкий уровень потенциала (сигнал б). Транзистор элемента остается закрытым, и на его выходе сохраняется высокий уровень .потенциала.

Транзистор 14 элемента 2 будет открыт до конца положительного импульса ГИ. С приходом отрицательного импульса ГИ транзистор быстро закроется обратным током базы, текущим через резистор 10 и,конденсатор 12. После закрывания транзистора конденсатор 12 разряжается через диод 18.

Запрещающий сигнал а iHB входе элемента 1 с предыдущего элемента заканчиlваетcя вместе с положительным им пульсом ГИяред (фиг. 3), т. е. на т/4 периода раньше окончайия положительного импульса ГИ питания элемента .1.

Чтобы транзистор 14 в элементе 1 аста вался закрытым до окончания положительного импульса ГИ, на входе его подается за(прещающий импульс б с выхода элемента 2.

Если во время дейстгзия,положительно го импульса ГИ на всех входах элемента 1 действует разрешающий высокий уровень потенциала, то на выходе этого элемента формируется импульс, который поступает на вход элемента 2 и запрещает формирование импульса на его выходе. Для обеспечения задержки открывания транзистора iB элементе 2 сопроти вление резистора 10 ia нем выбирается большей величины, чем сопротивление резистора 10 в элементе 1, а свободные входные диоды подключаются к источнику постоянного питания.

Предложенная логическая схема обладает повы шенной помехоустойчивостью, обеспечиваемойой р азделением входных и выходных це10 пей элементов конденсатором и введением в цепь базы транзисторов напряжения смещения — Еси

Предмет изобретения

Логическая схема «И вЂ” НЕ/И», состоящая из двух динамических элементов с взаимно инверсными выходами, каждый из которых содержит входную дивную схему «И», .раздели20 тельный конденсатор, диод в цепи разряда и инвертирующий транзистор, отличающаяся тем, что, с целью повышения быстродействия и увеличения помехоустойчивости, в каждом элементе база инвертирующего транзистора

25 соединена через разделительный конденсатор с выходом диодной схемы «И» и через диод цепи разряда конденсатора — с источником смещения, причем выход каждого из динамических элементов соединен с одним из входов

30 второго элемента.

Заказ 1328/16 Тираж 500 Подписное

ЦНИИПИ Комитета по делам изобретений и открытий при Совете Министров СССР

Москва, )К-35, Раушская наб„д. 4/5