Способ начальной загрузки компьютерной системы с множеством центральных процессоров

Иллюстрации

Показать всеИзобретение относится к компьютерным технологиям, а именно к начальной загрузи компьютерной системы, имеющей множество центральных процессоров. Технический результат – уменьшение времени начальной загрузки компьютерной системы с множеством CRU. Способ начальной загрузки компьютерной системы с множеством центральных процессоров (CPU), содержащий этапы, на которых инициируют по меньшей мере два CPU из множества CPU при запуске процесса начальной загрузки, получают с помощью каждого из указанных по меньшей мере двух инициализированных CPU доступ к таблице описания задач (TDC), хранимой в компьютерной системе, причем TDC включает в себя информацию по меньшей мере о двух задачах процесса начальной загрузки, при этом когда первым CPU из инициализированных CPU получен доступ к TDC, указанный первый CPU выполнен с возможностью блокировки TDC, при этом заблокированная TDC не является доступной для CPU, отличающихся от первого CPU, выбирают с помощью каждого из указанных по меньшей мере двух инициализированных CPU задачу по меньшей мере из двух задач согласно информации о выборе указанных по меньшей мере двух задач в TDC, получают с помощью каждого из указанных по меньшей мере двух инициализированных CPU выбранную задачу согласно адресной информации выбранной задачи в TDC, и исполняют с помощью каждого из указанных инициализированных CPU выбранные задачи по меньшей мере частично параллельно. 3 н. и 15 з.п. ф-лы, 7 ил., 1 табл.

Реферат

Область техники, к которой относится изобретение

Данная заявка относится, в общем, к компьютерным технологиям и, более конкретно, к способу начальной загрузки компьютерной системы, имеющей множество центральных процессоров (CPU).

Уровень техники

Начальная загрузка компьютерной системы является процессом самозагрузки. Когда компьютерная система включается, этот процесс инициализирует аппаратное обеспечение компьютерной системы, а затем запускает операционную систему (например, ядро). Короткая последовательность начальной загрузки обычно начинается с базовой системы ввода-вывода (BIOS), начального загрузчика и затем ядра.

Когда компьютерная система включается, BIOS выполняет внутренний начальный тест (POST), который инициализирует устройства, включающие в себя оперативное запоминающее устройство (RAM), процессор, клавиатуру, монитор и т.д. Обычно, процессор в компьютерной системе является функциональным блоком аппаратного обеспечения, который включает в себя один CPU или множество CPU (часто называемым одноядерным процессором или многоядерным процессором). Или, компьютерная система может включать в себя множество процессоров. Если компьютерная система включает в себя множество CPU (например, в формах многопроцессорной системы или многоядерной процессорной системы), то один из этих CPU может быть определен как «CPU начальной загрузки», который исполняет коды инициализации BIOS и коды инициализации ядра для процесса начальной загрузки. Остающиеся CPU (часто называемые прикладными процессорами (AP)) остаются нерабочими, пока OS не начнет исполнение. Как только инициализация BIOS завершена, устройство начальной загрузки идентифицируется, и начальный загрузчик загружается из устройства начальной загрузки в RAM, и управление передается начальному загрузчику. Начальный загрузчик определяет, какую OS (например, ядро) следует загрузить, загружает эту определенную OS из устройства начальной загрузки в RAM и передает управление этой OS. Как только OS начинает исполнение, она инициализирует ресурсы и структуру данных, остающиеся CPU и исполняет начальный сценарий, который инициализирует различные службы.

В большинстве существующих компьютерных системах, вышеописанные этапы начальной загрузки последовательно исполняются только одним CPU. Некоторая величина времени затрачивается в процессе начальной загрузки, и уменьшение времени начальной загрузки имеет главное значение.

Раскрытие изобретения

Для экономии времени начальной загрузки компьютерной системы с множеством CPU, различные варианты осуществления обеспечены посредством этого раскрытия.

В качестве первого аспекта этого раскрытия обеспечивается способ начальной загрузки компьютерной системы с множеством CPU. Этот способ содержит этапы, на которых: инициируют по меньшей мере два CPU из множества CPU при запуске процесса начальной загрузки; получают с помощью каждого из указанных по меньшей мере двух инициализированных CPU доступ к таблице описания задач (TDC), хранимой в компьютерной системе, причем TDC включает в себя информацию по меньшей мере о двух задачах процесса начальной загрузки; и выбирают с помощью каждого из указанных по меньшей мере двух инициализированных CPU задачи по меньшей мере из двух задач согласно информации о выборе указанных по меньшей мере двух задач в TDC; получают с помощью каждого из указанных по меньшей мере двух инициализированных CPU выбранную задачу согласно адресной информации выбранной задачи в TDC; и исполняют, каждым из указанных инициализированных CPU, выбранные задачи по меньшей мере частично параллельно.

В качестве второго аспекта этого раскрытия, обеспечивается компьютерная система. Компьютерная система включает в себя: множество CPU, соединенных с памятью, причем по меньшей мере два CPU из множества CPU выполнены с возможностью инициализации при запуске процесса начальной загрузки; указанная память выполнена с возможностью хранения TDC и первой команды, причем TDC включает в себя информацию по меньшей мере о двух задачах процесса начальной загрузки; а указанные по меньшей мере два инициализированных CPU из множественных CPU выполнены с возможностью получения, согласно первой команде, доступа каждого из них к TDC, выбора каждым из них задачи из указанных по меньшей мере двух задач согласно информации о выборе указанных по меньшей мере двух задач в TDC, получения каждым из них выбранной задачи согласно адресной информации выбранной задачи в TDC; и исполнения выбранных задач по меньшей мере частично параллельно.

В качестве третьего аспекта этого раскрытия, обеспечен энергонезависимый машиночитаемый носитель данных, содержащий коды для начальной загрузки компьютерной системы с множеством CPU. Эти коды при исполнении множеством инициализированных CPU из множества CPU вызывают выполнение этапов, на которых: получают доступ с помощью каждого из инициализированных CPU к TDC, хранимой в компьютерной системе, причем TDC включает в себя информацию по меньшей мере о двух задачах процесса начальной загрузки; и выбирают с помощью каждого из указанных по меньшей мере двух инициализированных CPU задачи, по меньшей мере из двух задач согласно информации о выборе указанных по меньшей мере двух задач в TDC; получают с помощью каждого из указанных по меньшей мере двух инициализированных CPU выбранную задачу согласно адресной информации выбранной задачи в TDC; и исполняют с помощью каждого из указанных инициализированных CPU выбранных задач по меньшей мере частично параллельно.

В качестве четвертого аспекта этого раскрытия, обеспечена таблица данных. Таблица данных включает в себя: поле информации о выборе, выполненное с возможностью указания информации о выборе, соответствующей по меньшей мере двум задачам; и поле адресной информации, выполненное с возможностью указания адресной информации, соответствующей этим по меньшей мере двум задачам; причем множество инициализированных CPU компьютерной системы с множеством CPU выполнены с возможностью выбора задачи из указанных по меньшей мере двух задач согласно полю информации о выборе, получения выбранных задач согласно полю адресной информации и исполнения выбранных задач по меньшей мере частично параллельно.

В качестве пятого аспекта этого раскрытия, обеспечен другой способ начальной загрузки компьютерной системы с множеством CPU, причем указанный способ содержит этапы, на которых: инициируют с помощью схемы инициализации компьютерной системы один или более CPU компьютерной системы; выбирают с помощью каждого из инициализированных CPU задачу по меньшей мере из двух задач согласно TDC, хранимую в компьютерной системе, причем каждая задача имеет свою информацию о выборе и адресную информацию, записанную в TDC, при этом различные задачи выбираются из указанных по меньшей мере двух задач различными инициализированными CPU согласно информации о выборе указанных задач; получают с помощью каждого из инициализированных CPU программные команды выбранной задачи согласно адресной информации выбранной задачи; и исполняют с помощью каждого из инициализированных CPU выбранные задачи по меньшей мере частично одновременно; причем TDC включает в себя информацию обо всех задачах для процесса начальной загрузки, при этом инициализированные CPU выполнены с возможностью продолжения выбора и исполнения указанных задач согласно TDC, пока не исполнены все задачи, информация о которых находится в TDC.

Краткое описание чертежей

Фиг. 1 является блок-схемой компьютерной системы в соответствии с одним вариантом осуществления указанного раскрытия;

фиг. 2 является блок-схемой способа параллельного исполнения в соответствии с одним вариантом осуществления этого раскрытия;

фиг. 3 показывает структуру таблицы описания задач (TDC) в соответствии с одним вариантом осуществления этого раскрытия;

фиг. 4 является блок-схемой процедуры выбора и исполнения CPU задач из TDC, в соответствии с одним вариантом осуществления этого раскрытия;

фиг. 5 является блок-схемой множества CPU, исполняющих задачи параллельно, согласно одному варианту осуществления этого раскрытия;

фиг. 6 является примерной структурой TDC, и процесса модуляризации генерирования TDC для процесса начальной загрузки; и

фиг. 7 является блок-схемой устройства для начальной загрузки компьютерной системы.

Осуществление изобретения

Чтобы сделать вышеупомянутые задачи, технические решения и преимущества данной заявки более понятными, варианты осуществления описываются ниже с сопутствующими чертежами.

Фиг. 1 является блок-схемой компьютерной системы 100 в соответствии с одним вариантом осуществления этого раскрытия. Компьютерная система 100 включает в себя процессор 101, связанный с памятью, такой как оперативное запоминающее устройство (RAM) 104, и, в случае необходимости, связанный с блоком 106 памяти. Блоком 106 памяти может быть постоянное запоминающее устройство (ROM) или другое запоминающее устройство (например, жесткий диск или флэш-память и т.д.).

Процессор 101 может включать в себя множество CPU, такие как CPU 0 и CPU 1, показанные на фиг. 1. В случае необходимости, компьютерная система 100 включает в себя более одного процессора, например процессор 101 и процессор 108 на фиг. 1. Каждый из процессоров 101 и 108 может быть либо одноядерным процессором, либо многоядерным процессором.

Различные коды для исполнения CPU процессора 101 могут храниться либо в RAM 104, либо в блоке 106 памяти. В случае необходимости, коды 109 копируются в RAM 104 из блока 106 памяти для исполнения процессором 101. В случае необходимости, коды, хранимые в блоке памяти, включают в себя, но не ограничены этим, любой модуль или комбинацию из BIOS-модуля, модуля начального загрузчика, модуля ядра. Также в блоке памяти находятся таблица описания задач (TDC), первая команда и вторая команда, которые будут подробно обсуждаться позже.

В случае необходимости, компьютерная система дополнительно включает в себя устройство 102 вывода (например, устройство отображения, такое как LCD (жидкокристаллический дисплей), a LED дисплей (дисплей на светодиодах), CRT (электроннолучевая трубка) или проектор), устройство 103 ввода (например, мышь, клавиатуру, сенсорный экран или считывающее устройство, которое может обнаруживать ввод пользователя). Устройство 102 вывода управляется процессором 101 для отображения графического интерфейса взаимодействия. В случае необходимости, компьютерная система дополнительно включает в себя интерфейс 105 связи для обмена данными или сигналами с внешней сетью или другими устройствами. Вышеупомянутые различные коды для исполнения CPU процессора 101 (такие как любое или комбинация из BIOS-модуля, модуля начального загрузчика, модуля ядра, TDC, первой команды и второй команды) могут быть получены через интерфейс 105 связи от другого устройства.

Вышеупомянутые элементы компьютерной системы 100 могут быть соединены друг с другом посредством шины, такой как шина данных, адресная шина, шина управления, шина расширения или локальная шина и т.д.

Компьютерной системой 100 может быть настольный компьютер, сетевой сервер, персональный цифровой/электронный секретарь (PDA), мобильный телефон, планшет, терминальное устройство, устройство связи, встроенная система или любые другие устройства, имеющие структуру, подобную показанной на фиг. 1. Однако данное раскрытие не ограничено какими-либо конкретными типами компьютерной системы.

Обеспечен способ начальной загрузки компьютерной системы с множеством CPU.

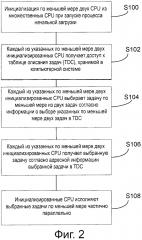

Фиг. 2 является блок-схемой этого способа. Хотя способ, описанный здесь, может быть реализован в компьютерной системе 100, показанной на фиг. 1, он не ограничен такой системой.

Для компьютерной системы, которая включает в себя множество CPU, и по меньшей мере два CPU включены в процесс начальной загрузки, этот способ предусматривает следующие блоки:

S100: инициализацию по меньшей мере двух CPU из множества CPU при запуске процесса начальной загрузки;

В случае необходимости, эти по меньшей мере два CPU, которые включены в процесс начальной загрузки инициализируются посредством схемы 110 инициализации, связанной с этими CPU (см. фиг. 1) компьютерной системы. Схема инициализации состоит в том, что, после включения или перезагрузки компьютерной системы, она инициализирует компоненты компьютерной системы, включающие в себя эти по меньшей мере два CPU, которые включены в процесс начальной загрузки. Схема инициализации может также инициализировать RAM 104 для использования этими по меньшей мере двумя CPU. Альтернативно, схема инициализации может сначала инициализировать часть из этих по меньшей мере двух CPU, например CPU начальной загрузки из этих по меньшей мере двух CPU, а затем инициализировать остальное. Например, инициализированный CPU начальной загрузки может получить доступ к носителю 106 данных для получения второй команды, хранимой в носителе 106 данных, и инициализировать оставшийся (оставшиеся) CPU согласно этой второй команде.

S102: каждый из этих по меньшей мере двух инициализированных CPU получает доступ к таблице описания задач (TDC), хранимой в компьютерной системе, причем TDC включает в себя информацию по меньшей мере о двух задачах процесса начальной загрузки;

В случае необходимости, когда первый CPU из инициализированных CPU получает доступ к TDC, этот первый CPU блокирует TDC, и заблокированная TDC не является доступной для CPU, отличающегося от первого CPU. Например, как показано на фиг. 3, TDC может включать в себя поле «блокировки TDC». Для блокировки TDC, первый CPU может пометить поле блокировки TDC как «заблокированная».

S104: каждый из этих по меньшей мере двух инициализированных CPU выбирает задачу из по меньшей мере двух задач согласно информации о выборе этих по меньшей мере двух задач в TDC;

В случае необходимости, информация о выборе дополнительно содержит поле приоритета, указывающее приоритет каждой из этих по меньшей мере двух задач, и задача с более высоким приоритетом среди этих по меньшей мере двух задач выбирается сначала первым CPU.

В случае необходимости, информация о выборе дополнительно содержит поле зависимости, указывающее вторую задачу, от которой зависит первая задача из этих по меньшей мере двух задач, и первая задача является выбираемой первым CPU, когда вторая задача помечена как завершенная.

В случае необходимости, информация о выборе дополнительно содержит поле блокировки, указывающее заблокирована ли каждая из этих по меньшей мере двух задач инициализированным CPU, причем после выбора первым CPU третьей задачи в этих по меньшей мере двух задачах согласно информации о выборе, первый CPU помечает поле блокировки третьей задачи как заблокированное, и причем третья задача, помеченная как заблокированная, не является выбираемой инициализированными CPU, отличающимися от первого CPU.

В случае необходимости, информация о выборе дополнительно содержит поле состояния, указывающее, завершена ли каждая из этих по меньшей мере двух задач, и причем после завершения исполнения четвертой задачи в этих по меньшей мере двух задачах, первый CPU помечает поле состояния четвертой задачи как завершенная, и причем четвертая задача, помеченная как завершенная, не является выбираемой инициализированными CPU.

В случае необходимости, после окончания выбора первым CPU, первый CPU разблокирует TDC.

S106: каждый из этих по меньшей мере двух инициализированных CPU получает выбранную задачу согласно адресной информации выбранной задачи в TDC;

S108: инициализированные CPU исполняют выбранные задачи по меньшей мере частично параллельно.

В случае необходимости, информация о выборе дополнительно содержит поле размера, указывающее размер каждой из этих по меньшей мере двух задач, и первый CPU определяет, исполнить ли пятую задачу из этих по меньшей мере двух задач согласно доступной памяти для исполнения задач и полей размеров пятой задачи и задач, исполняемых в доступной памяти.

В случае необходимости, после этапа инициализации, этапы доступа, выбора, получения и исполнения инициализированными CPU повторяются, пока не будут исполнены все задачи, чья информация находится в TDC.

Вышеупомянутые этапы S102-S108 могут быть осуществлены первым CPU согласно первой команде.

В случае необходимости, эти по меньшей мере две задачи включают в себя задачи, исполняемые параллельно инициализированными CPU, и происходят из процесса начальной загрузки компьютерной системы, которая включает в себя модуль базовой системы ввода-вывода (BIOS), модуль начального загрузчика и модуль ядра.

В случае необходимости, этапы из BIOS-модуля, модуля начального загрузчика и модуля ядра модуляризуются на этапы, включающие в себя независимые или асинхронные этапы, и модуляризованные этапы выделяются для образования задач из этих по меньшей мере двух задач.

В случае необходимости, этапы инициализации периферийных устройств в BIOS-модуле разделены на этапы инициализации для инициализации устройства, отличной от модификации регистра конфигурации, и этапы регистра для модификации регистра конфигурации на основе этапов инициализации, и этапы инициализации и этапы регистра выделяются для образования других задач из этих по меньшей мере двух задач.

В случае необходимости, TDC генерируется согласно задачам, генерируемым из модуляризации и разделения.

Как показано на фиг. 3, примерная TDC включает в себя адресную информацию и информацию о выборе множества задач (например, задач 1-N, N>2). Каждый из инициализированных CPU, включенных в процесс начальной загрузки, выбирает задачу из этих по меньшей мере двух задач согласно информации о выборе, получает выбранную задачу из блока 106 памяти или RAM 104 согласно адресной информации этой задачи и исполняет полученную задачу.

TDC может включать в себя поле метаданных TDC, указывающих информацию о TDC-файле, который может использоваться процессом для манипулирования файловым контентом и вопросов, связанных с безопасностью, и т.д. Поле блокировки TDC может быть частью поля метаданных TDC.

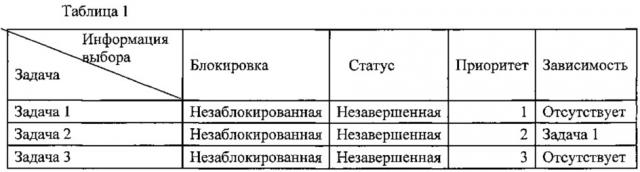

Нижеследующее является примером двух инициализированных CPU (например, CPU 1 и CPU 2), выбирающих задачи из трех задач в TDC (например, задачи 1, задачи 2 и задачи 3) с различной информацией о выборе (такой как блокировка, состояние, приоритет и зависимость) согласно TDC. Информация о выборе задач 1-3 показана в таблице 1.

Когда CPU 1 получает доступ к TDC, он может выбрать задачу 1 для исполнения согласно информации о выборе, так как задача 1 имеет наивысший приоритет среди задач 1-3, и она помечена как «незаблокированная». После выбора задачи 1, CPU 1 может пометить поле блокировки задачи 1 как «заблокированная». Затем, CPU 2 получает доступ к TDC для выбора задачи. Поскольку: 1) поле блокировки задачи 1 указывает, что задача 1 заблокирована (т.е. задача 1 с наивысшим приоритетом уже выбрана CPU 1); 2) задача 2 со вторым наивысшим приоритетом зависит от задачи 1, и 3) поле состояния задачи 1 указывает, что задача 1 является незавершенной, CPU 2 выбирает задачу 3 с третьим наивысшим приоритетом для исполнения согласно информации о выборе. После выбора задачи 3, CPU 2 может пометить поле блокировки задачи 3 как «заблокированная». После исполнения задачи 1, CPU 1 может повторно получить доступ к TDC, пометить поле состояния задачи 1 как «завершенная» и выбрать другую задачу в TDC для исполнения. Поскольку: 1) поле блокировки задачи 3 указывает, что задача 3 является «заблокированной», и поле состояния задачи 1 указывает, что задача 1 является «завершенной» (т.е. задачи 1 и 3 не являются выбираемыми), CPU 1 может выбрать задачу 2, которая является теперь выбираемой из-за завершения задачи 1. Вышеупомянутый выбор задач и модификация информации о выборе могут быть осуществлены приложением планировщика, исполняемым на процессоре согласно первой команде.

Во время процесса начальной загрузки, память (такая как RAM 104) может быть частично инициализирована. Следовательно, существует ограниченное пространство памяти, доступное для задач с некоторым размером, исполняемых параллельно. Если много задач больших размеров исполняются параллельно, то другая задача не может исполняться / или копироваться в память. Для решения этой проблемы, диспетчер памяти (например, приложение диспетчера памяти, исполняемое одним из CPU) обеспечен в варианте осуществления для управления памятью. TDC может дополнительно включать в себя поле размера задач. Поле размера может указывать размер соответствующей задачи. Приложение планировщика может дополнительно решить, какую задачу исполнять или не исполнять в настоящее время согласно доступной памяти, информация о которой обеспечивается диспетчером памяти, и полю размера (такого как размер исполняемых задач и задач, подлежащих более позднему исполнению). Например, приложение планировщика может получить доступ к TDC для модификации информации о выборе некоторой задачи (такой как любое или любая комбинация из поля блокировки, поля состояния, поля приоритета и поля зависимости). Соответственно, последовательность исполнения задач может динамически регулироваться для лучшего использования памяти. Диспетчер памяти может также запустить инициализацию других частей памяти, если это необходимо. Инициализация других частей памяти может исполняться параллельно с другими задачами.

В этом варианте осуществления, задачи планируются на основе TDC, которая действует как точка опоры для планирования. Базовое управление памятью может быть также достигнуто посредством использования этой TDC.

В случае необходимости, информацию о выборе может дополнительно включать в себя поле кода ошибки для возможной отладки. Например, если задача неудачно завершается во время исполнения, выбора или управления диспетчера памяти, то соответствующий код ошибки будет помещен в поле кода ошибки этой задачи.

В качестве примера, программные коды задач, первая команда или вторая команда могут храниться в блоке 106 памяти или могут быть считаны в RAM 104. Согласно первой команде и TDC, Каждый инициализированный CPU, который включен в процесс начальной загрузки, может получить доступ к блоку 106 памяти или RAM 104, для исполнения задачи, которую он выбрал. Инициализированный CPU, служащий как CPU начальной загрузки, может инициализировать другие CPU и активировать их с использованием межпроцессорных прерываний (IPI) настройки. Исполнение инициализированных CPU может начаться с адреса начала реального режима, определенного IPI-сообщением. Этот адрес начала соответствует первой команде для выбора и исполнения инициализированными CPU задачи согласно TDC.

Для уменьшения времени начальной загрузки, инструктируется, что по меньшей мере две задачи, выбранные инициализированными CPU, которые включены в процесс начальной загрузки, исполняются по меньшей мере частично одновременно.

Через техническое решение в вышеупомянутом варианте осуществления этого раскрытия, время для исполнения задач может быть уменьшено посредством исполнения по меньшей мере частично параллельно. Может быть ясно, что возможно, что чем больше CPU используются в этом решении, тем больше времени исполнения может быть сэкономлено в процессе начальной загрузки.

Фиг. 4 является блок-схемой примерной процедуры для выбора и исполнения задач CPU из TDC в соответствии с одним вариантом осуществления этого раскрытия. Этот способ предусматривает следующие блоки:

в блоке S401, CPU загружает вышеупомянутую первую команду и начинает исполнять эту первую команду. Как утверждалось ранее, первая команда используется для выбора и исполнения задач CPU согласно TDC. После блока S401, CPU сначала исполняет блок S403;

в блоке S403, CPU определяет, заблокирована ли TDC. Если TDC заблокирована, то CPU исполняет блок S402. Если TDC не заблокирована, то CPU исполняет блок S404;

в блоке 402, CPU ожидает/опрашивает некоторое время, затем переходит к блоку S403 для повторного определения, заблокирована ли TDC.

Атрибут блокировки используется как механизм синхронизации в этом варианте осуществления для ограничения доступа к данным в TDC, которая может совместно использоваться множеством процессоров. Это позволяет одному процессу, например, управляемому CPU, получить доступ к этим данным в данный момент/время. Так что даже хотя множество процессоров, например, управляющие множеством CPU, могут получить доступ/модифицировать совместно используемые данные, в любой данный момент/время, только процесс, имеющий блокировку на этих данных, может получить доступ/модифицировать их. Эти данные могут быть доступны/модифицированы другим процессом, только когда он приобретает блокировку на эти данные (когда процесс, ранее удерживающий блокировку на эти данные, освобождает эту блокировку).

В блоке S404, CPU блокирует соответствующие поля TDC. Например, CPU может пометить поле блокировки задачи, подлежащей исполнению им, в TDC как «заблокированная» с идентификацией CPU, для защиты тех же самых данных в TDC от доступа посредством других CPU.

В блоке S405, CPU определяет, завершены ли все задачи в TDC согласно информации о выборе этих задач. Если не все задачи в TDC были завершены, то CPU исполняет блок S407. Если все задачи в TDC были завершены, то CPU исполняет блок S406 или может непосредственно исполнять блок S416.

В блоке S406, CPU разблокирует задачу в TDC. Например, CPU может пометить поле блокировки задачи в TDC как «незаблокированная». Тогда CPU может исполнять блок S416.

В блоке S407, CPU выбирает задачу из TDC согласно информации о выборе TDC и блокирует выбранную задачу. Конкретная стратегия выбора задачи уже была описана выше. Для краткости, она не будет повторно описываться здесь.

В блоке S408, CPU разблокирует задачу в TDC и переходит к исполнению блока S409 или непосредственно переходит к исполнению блока S411. После блока S408, другие CPU могут получить доступ к TDC для выбора задач.

В блоке S409, CPU определяет, находится ли уже выбранная задача в RAM. Если да, CPU переходит к исполнению блока S411. Если нет, CPU переходит к исполнению блока S410.

В блоке S410, CPU копирует задачу, подлежащую исполнению, в RAM. Затем CPU переходит к исполнению блока S411. Например, CPU может осуществить поиск кода задачи в блоке памяти согласно адресной информации этой задачи и копировать код этой задачи в RAM из блока памяти для исполнения.

В блоке S411, CPU исполняет выбранную задачу. После завершения исполнения выбранной задачи, CPU может перейти к исполнению блока S413. В случае необходимости, перед исполнением, CPU осуществляет поиск выбранной задачи в RAM согласно адресной информации этой задачи и получает выбранную задачу.

В блоке S413, CPU определяет, заблокирована ли TDC. Если TDC заблокирована, то CPU исполняет блок S412. Если TDC не заблокирована, то CPU исполняет блок S414;

В блоке 412, CPU ожидает/опрашивает некоторое время, затем переходит к блоку S413 для повторного определения, заблокирована ли TDC.

В блоке S414, CPU блокирует задачу в TDC. Затем, CPU переходит к исполнению блока S415.

В блоке S415, CPU помечает поле состояния в информации о выборе завершенной задачи как «завершенная». Затем CPU может перейти к блоку S405.

В блоке S416, CPU выходит из процедуры выбора и исполнения, показанной на фиг. 4. Например, CPU может остановить исполнение первой команды.

Фиг. 5 является блок-схемой множества CPU, исполняющих задачи параллельно в соответствии с одним вариантом осуществления этого раскрытия.

Как показано на фиг. 5, на необязательной стадии 1, включение или перезагрузка компьютерной системы может инициализировать все или часть из множества CPU (например, CPU 0 из CPU 0-N). Некоторые или все инициализированные CPU могут быть включены в процесс начальной загрузки.

В случае необходимости, когда только CPU 0 как CPU начальной загрузки был инициализирован во время стадии 1, и другие CPU находятся в нерабочем состоянии (или неинициализированном состоянии), инициализированный CPU 0 инициализирует оставшиеся CPUs на необязательной стадии 2.

На стадии 3, инициализированные CPU могут выбрать задачи из TDC и исполнить их независимо и по меньшей мере частично одновременно способом, показанным, например, на фиг. 4, пока все задачи в TDC не завершатся.

Через вышеописанное параллельное исполнение множества CPU, время для исполнения задач в процессе начальной загрузки в CPU компьютерной системы с множеством CPU может быть уменьшено. Например, время начальной загрузки может быть уменьшено до 90/100*(X/N-N*D*X), где X - текущее время начальной загрузки, а N - число CPUs, D - период времени для выбора CPU следующей задачи в TDC. Это просто оценка, и она не может масштабироваться вне некоторых чисел.

Отметим, что вышеприведенный вариант осуществления относительно параллельного исполнения множеством CPU может быть реализован в различных процессах в компьютерной системе, а не только в процессе начальной загрузки. Однако процесс начальной загрузки может быть процессом, который получает большую выгоду от параллельного исполнения. Как отмечалось выше, типичный процесс начальной загрузки включает в себя BIOS-модуль, модуль начального загрузчика и модуль ядра. BIOS-модуль используется для инициализации и тестирования системных аппаратных компонентов. BIOS-модулем может быть любой вид системы, реализующей по меньшей мере функцию инициализации и тестирования системных аппаратных компонентов, таких как базовая система ввода-вывода, унифицированный расширяемый интерфейс встроенного программного обеспечения (UEFI) и расширяемый интерфейс встроенного программного обеспечения (EFI)). Начальный загрузчик является модулем, запускаемым посредством BIOS для загрузки изображения ядра в RAM. Ядро является главным компонентом большинства компьютерных операционных систем. Оно является мостом между приложениями и фактической обработкой данных, осуществляемой на аппаратном уровне. После завершения модуля начального загрузчика, модуль ядра может исполняться для инициализации ресурсов и структуры данных ядра.

Хорошо известно, что каждый из этих трех модулей в процессе начальной загрузки включает в себя различные этапы исполнения. Как показано на фиг. 6, для реализации исполнения множеством CPU в процессе начальной загрузки, эти этапы этих трех модулей могут быть взаимно организованы в процедуре, названной «модуляризацией», т.е. каждый модуль может быть разбит на части. Каждая часть может включать в себя один или более независимых или асинхронных этапов. Со ссылкой на фиг. 6, например, этапы init() в BIOS-модуле могут быть разбиты на этапы init_0_0() и init_O_1(), которые являются независимыми друг от друга. Другой конкретный пример модуляризации на BIOS-модуле также обеспечен здесь. Этапы инициализации периферийных устройств в BIOS-модуле используются для последовательного исполнения, так как регистры конфигурации могут быть модифицированы только одним процессом в данное время/момент. В этом варианте осуществления, этапы инициализации периферийных устройств могут быть разбиты на две меньшие группы этапов: этапы инициализации для инициализации устройства, отличной от модификации регистров конфигурации, и этапы регистров для модификации регистров конфигурации на основе этого этапа инициализации. Таким образом, этапы инициализации для инициализации множества периферийных устройств могут исполняться множеством CPU параллельно. А этапы регистров относительно множества периферийных устройств могут исполняться CPU последовательно позже, когда это необходимо. Подобная модуляризация может быть реализована на модуле начальной загрузки и модуле ядра. Для совместно используемых ресурсов, она может быть доступна для множества CPU с использованием блокировок для синхронизации.

Модуляризованные этапы могут быть затем разделены для образования индивидуальных задач. Например, модуляризованные этапы в BIOS-модуле могут быть сгруппированы в задачи bios_task1() и bios_task2(). По меньшей мере две задачи из сгруппированных задач могут быть одновременно исполняемыми задачами. Последовательность этих задач может быть определена согласно установленному приоритету каждой задачи. Например, задачи из модуля начального загрузчика могут быть настроены для исполнения параллельно задачам из BIOS-модуля. Таким образом, задачи, подобные копированию ядра и распаковке, могут быть достигнуты в то время, как BIOS-модуль завершает свое исполнение. TDC, описывающая эти задачи, может быть сгенерирована согласно по меньшей мере одному из следующих атрибутов каждой задачи: приоритету, адресу, размеру, коду ошибки, блокировке, состоянию и зависимости.

В случае необходимости, таблица векторов прерываний (IVT) инициализируется для всех CPU во время исполнения части или всех этапов из BIOS-модуля. IVT является таблицей, связанной с CPU, которая содержит соответствие прерываний и обработчиков прерываний. Это таблица, которая дает информацию CPU, какой обработчик прерываний (программу/функцию) исполнять, при приеме конкретного прерывания.

В случае необходимости, инициализация RAM осуществляется по фазам. В каждой фазе, только часть области RAM должна быть инициализирована. Например, только область RAM для копирования задач BIOS-модуля и модуля начального загрузчика будет инициализирована в первой фазе и/или второй фазе. Инициализация остальной области RAM для копирования задач модуля ядра может быть осуществлена в третьей фазе. В случае необходимости, так как TDC включает в себя размер каждой задачи, инициализация RAM может обрабатываться более точным образом. Например, инициализация RAM может быть осуществлена во множественные фазы согласно последовательности и размеру задач в TDC. В случае необходимости, инициализация RAM как задача в TDC осуществляется параллельно с другими задачами начальной загрузки.

На фиг. 7 показана блок-схема устройства для начальной загрузки компьютерной системы. Это устройство включает в себя: множество модулей 702 обработки (включающие в себя по меньшей мере два модуля обработки, такие как модуль 1 обработки и модуль 2 обработки) и модуль 703 памяти, причем по меньшей мере два модуля обработки из множества модулей 702 обработки инициализируются при запуске процесса начальной загрузки; модуль 703 памяти выполнен с возможностью хранения таблицы описания задач (TDC), причем TDC включает в себя информацию по меньшей мере о двух задачах процесса начальной загрузки; и инициализированные модули обработки из множественных модулей обработки выполнены с возможностью доступа каждого к TDC, выбора каждым задачи из этих по меньшей мере двух задач согласно информации о выборе этих по меньшей мере двух задач в TDC, получения каждым выбранной задачи согласно адресной информации выбранной задачи в TDC; и исполнения выбранных задач по меньшей мере частично параллельно.

В случае необходимости, множество модулей 702 обработки соответствуют процессору 101 и/или процессору 108 на фиг. 1. Модуль памяти соответствует блоку 106 памяти и RAM 104 на фиг. 1.

В случае необходимости, первый модуль обработки из инициализированных модулей обработки дополнительно выполнен с возможностью блокировки TDC после доступа к TDC, и причем заблокированная TDC не является доступной для модулей обработки, отличающихся от первого модуля обработки.

В случае необходимости, информация о выборе дополнительно содержит поле приоритета, указывающее приоритет каждой из этих по меньшей мере двух задач, и причем первый модуль обработки дополнительно выполнен с возможностью сначала выбрать задачу с более высоким приоритетом среди этих по меньшей мере двух задач.

В случае необходимости, информация о выборе дополнительно содержит поле зависимости, указывающее вторую задачу, от которой зависит первая задача в этих по меньшей мере двух задачах, и причем первый модуль обработки дополнительно выполнен с возможностью выбрать первую задачу, когда вторая задача помечена как завершенная.

В случае необходимости, информация о выборе дополнительно содержит поле блокировки, указывающее, заблокирована ли каждая из этих по меньшей мере двух задач инициализированным модулем обработки, причем первый модуль обработки дополнительно выполнен с возможностью блокировки третьей задачи в этих по меньшей мере двух задачах после выбора первым модулем обработки третьей задачи, и причем третья задача, помеченная как заблокированная, не является выбираемой инициализированными модулями обработки, отличающимися от первого модуля обработки.

В случае необходимости, информация о выборе дополнительно содержит поле состояния, указывающее, завершена ли каждая из этих по меньшей мере двух задач, п