Пары инструкций установления очерёдности исполнения инструкций, процессоры, способы и системы

Иллюстрации

Показать всеГруппа изобретений относится к области компьютерной техники и может быть использована для установления и изменения очередности исполнения инструкций в процессорах. Техническим результатом является обеспечение желаемой очередности исполнения инструкций. Процессор содержит блок выборки инструкций для выборки пары инструкций установления очередности исполнения инструкций, которая должна быть частью набора инструкций процессора, причем пара инструкций установления очередности исполнения инструкций включает в себя инструкцию активации и инструкцию установления, причем инструкция активации появляется перед инструкцией установления в очереди программы; и модуль установления очередности исполнения инструкций, в ответ на пару инструкций установления очередности исполнения инструкций, для предотвращения обработки инструкций, появляющихся после инструкции установления в очереди программы, перед инструкцией активации в части с изменением очередности исполнения инструкций процессора. 4 н. и 20 з.п. ф-лы, 20 ил.

Реферат

Область техники, к которой относится изобретение

Варианты осуществления, описанные здесь, относятся, в общем, к процессорам. В частности, варианты осуществления, описанные здесь, относятся, в общем, к установлению очередности исполнения инструкций в процессорах с изменением очередности исполнения инструкций.

Уровень техники

Многочисленные современные процессоры представляют собой процессоры с изменением очередности исполнения инструкций (ОоО), которые способны исполнять инструкции в очередности, которая отличается от очередности, в которой инструкции появляются в первоначальной программе программного обеспечения. Термин "очередность программы" часто используется по отношению к очередности исполнения инструкций в первоначальной программе программного обеспечения. Вместо обязательного исполнения инструкций с очередностью исполнения инструкций программы, ОоО-процессор может исполнять инструкции с очередностью, которая может зависеть от доступности входных данных, а также от потенциально различных других факторов. Посредством примера, возможны ситуации, когда некоторые младшие по значимости инструкции должны вводить данные из старших по значимости инструкций, в то время как другие младшие по значимости инструкции не должны вводить данные из любых старших по значимости инструкций.

Исполнение инструкций с изменением их очередности (ОоО) позволяет процессору незамедлительно исполнять инструкции, которые готовы к исполнению без задержки, связанной с ожиданием предыдущих инструкций, которые сами по себе могут быть не готовы к исполнению, так как они ожидают обработки данных. Очередность, с которой инструкции фактически исполняются в ОоО-процессоре, часто упоминается как очередность данных. Далее ОоО-процессор может переупорядочить результаты исполнения и/или состояние архитектуры и представить результаты исполнения и/или состояние архитектуры (например, для программного обеспечения, пользователя и т.д.) в виде первоначальной очередности программы вместо очередности данных, в которой были фактически исполнены инструкции. Преимущественно, такие ОоО-процессоры обычно имеют повышенную производительность и/или быстродействие, необходимую в части повышения использования каскадов конвейера или обработки временных слотов.

Однако одна сложная задача, связанная с ОоО-процессорами, в некоторых ситуациях состоит в том, что проблемы могут возникать тогда, когда ресурс, который должен быть доступен в очереди программы, доступен в очередности данных в результате изменения исполнения инструкций с изменением их очередности.

Краткое описание чертежей

Настоящее изобретение можно будет лучше понять со ссылкой на последующее описание и сопроводительные чертежи, которые используются для иллюстрации вариантов осуществления. На чертежах:

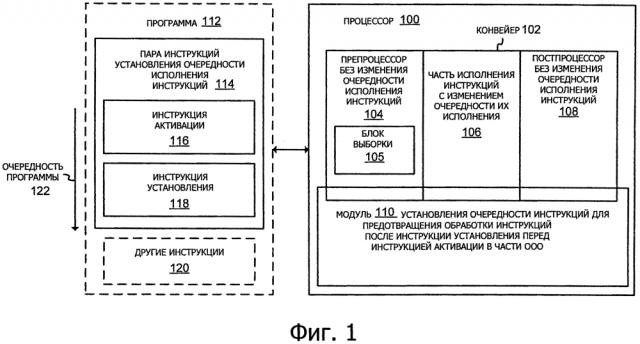

на фиг. 1 показана блок-схема варианта осуществления процессора, который выполнен с возможностью обработки или выполнения пары инструкций установления очередности исполнения инструкций;

на фиг. 2 показана блок-схема последовательности операций варианта осуществления способа, который выполняется в процессоре для обработки или выполнения варианта осуществления пары инструкций установления очередности исполнения инструкций;

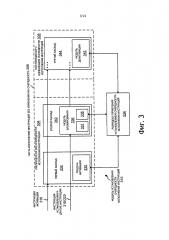

на фиг. 3 показана блок-схема первого примерного варианта осуществления подходящего модуля установления очередности исполнения инструкций;

на фиг. 4 показана блок-схема второго примерного варианта осуществления подходящего модуля установления очередности исполнения инструкций;

на фиг. 5А-С показаны блок-схемы, иллюстрирующие несколько вариантов осуществления подходящих каскадов конвейера для реализации активации, установления и деактивации очередности исполнения инструкций;

на фиг. 6 показана блок-схема первого варианта осуществления подходящего формата инструкции активации;

на фиг. 7А показана блок-схема второго варианта осуществления подходящего формата инструкции активации;

на фиг. 7В показана блок-схема варианта осуществления подходящего формата инструкции установления;

на фиг. 8А показана блок-схема, иллюстрирующая как примерный конвейер исполнения инструкций без изменения их очередности и примерное переименование регистров, так и конвейер с изменением очередности выдачи/исполнения инструкций согласно вариантам осуществления изобретения;

на фиг. 8В показана блок-схема, иллюстрирующая как примерный вариант осуществления ядра архитектуры исполнения инструкций без изменения их очередности и примерное переименование регистров, так и ядро архитектуры с изменением очередности выдачи/исполнения инструкций, которое будет включено в процессор, согласно вариантам осуществления изобретения;

на фиг. 9А показана блок-схема одного ядра процессора наряду с его подсоединением к сети межсоединений на кристалле и с его локальным подмножеством кэш-памяти 2-го уровня (L2) согласно вариантам осуществления изобретения;

на фиг. 9В показан расширенный вид части ядра процессора (фиг. 9А) согласно вариантам осуществления изобретения;

на фиг. 10 показана блок-схема процессора, который может иметь более одного ядро, может иметь встроенный контроллер памяти и может иметь встроенную графику согласно вариантам осуществления изобретения;

на фиг. 11 показана блок-схема системы в соответствии с одним вариантом осуществления настоящего изобретения;

на фиг. 12 показана блок-схема первой более конкретной примерной системы в соответствии с вариантом осуществления настоящего изобретения;

на фиг. 13 показана блок-схема второй более конкретной примерной системы в соответствии с вариантом осуществления настоящего изобретения;

на фиг. 14 показана блок-схема SoC в соответствии с вариантом осуществления настоящего изобретения;

на фиг. 15 показана блок-схема, сопоставляющая использование программного конвертера инструкций для преобразования двоичных инструкций в наборе инструкций источника в двоичные инструкции в целевом наборе инструкций согласно вариантам осуществления изобретения.

Подробное описание изобретения

В данном документе раскрыты пары инструкций установления очередности исполнения инструкций, процессоры для обработки или выполнения пар инструкций, способы, выполняемые процессорами при обработке или выполнении пар инструкций, и системы, входящие в состав одного или более процессоров, для обработки или выполнения пар инструкций. В последующем описании изложены многочисленные конкретные детали (например, функциональные возможности конкретных инструкций, конфигурации процессоров, микроархитектурные детали, последовательности операций и т.д.). Однако варианты осуществления могут применяться на практике без этих конкретных деталей. В других случаях хорошо известные схемы, структуры и технологии не были показаны подробно во избежание усложнения понимания описания.

На фиг. 1 показана блок-схема варианта осуществления процессора 100, который выполнен с возможностью обработки или выполнения пары инструкций 114 установления очередности исполнения инструкций. В некоторых вариантах осуществления процессор 100 может представлять собой процессор общего назначения (например, центральное процессорное устройство (CPU), или другой микропроцессор общего назначения, или процессор типа, который используется в настольном компьютере, ноутбуке, планшетном компьютере и в подобных компьютерах). Альтернативно, процессор может представлять собой процессор специального назначения. Примеры подходящих процессоров специального назначения включают в себя, но не ограничиваются ими, сетевые процессоры, коммуникационные процессоры, криптографические процессоры, графические процессоры, сопроцессоры, встроенные процессоры, процессоры цифровых сигналов (DSPS) и контроллеры (например, микроконтроллеры), и это всего лишь несколько примеров. Процессор может вполне представлять собой любой из различных процессоров с полным набором команд (CISC), различных процессоров с сокращенным набором инструкций (RISC), различных процессоров с очень длинным командным словом (VLrW), различных их гибридов и других типов процессоров.

Показана также программа 112. Посредством примера, программа может храниться в основной памяти или в другом подходящем запоминающем устройстве. Во время работы программа может запускаться, исполняться или иным образом выполняться процессором. Процессор может осуществлять выборку или иным образом принимать инструкции программы. В некоторых вариантах осуществления инструкции программы могут представлять собой часть набора инструкций процессора. Инструкции из набора инструкций могут представлять собой макроинструкции относительно высокого уровня, инструкции на языке ассемблера, инструкции на уровне машины или управляющие сигналы на уровне набора инструкций, который можно подать в процессор для исполнения в отличие от микроинструкций относительно низкого уровня, микроопераций или других инструкций или управляющих сигналов, декодируемых процессором из инструкций относительно более высокого уровня.

В некоторых вариантах осуществления процессор может представлять собой процессор 100 с изменением очередности исполнения инструкций (ОоО-процессор), который выполнен с возможностью исполнения инструкций с изменением очередности. ОоО-процессоры были обсуждены выше в разделе "Уровень техники". ОоО-процессор имеет ОоО-конвейер 102. Конвейер включает в себя препроцессор 104 без изменения очередности исполнения инструкций, часть 106 с изменением очередности исполнения инструкций и постпроцессор 108 без изменения очередности исполнения инструкций. Конкретные блоки или составные части этих фаз конвейера могут изменяться от реализации к реализации. В одном репрезентативном варианте осуществления препроцессор без изменения очередности исполнения инструкций может включать в себя блок или каскад выборки инструкций (например, блок 105 выборки), блок или каскад декодирования длины, блок или каскад декодирования, блок или каскад выделения, блок или каскад переименования. В одном репрезентативном варианте осуществления часть с изменением очередности исполнения инструкций может включать в себя блок или каскад планировщика (который иногда также упоминается как блок отправки или выдачи), регистровый(е) файл(ы) блоки и блок памяти или каскад считывания регистра/считывания памяти, исполнительный модуль(и) или каскад, блоки регистрового(ых) файла(ов) и блок памяти или каскад перезаписи/записи в память. В одном репрезентативном варианте осуществления постпроцессор без изменения очередности исполнения инструкций включает в себя каскад обработки исключений и блок или каскад завершения или фиксации изменений. Это является просто одним конкретным примером и следует понимать, что объем изобретения не ограничивается этим конкретным примером. В других вариантах осуществления можно использовать другие комбинации и конфигурации блоков и/или каскадов конвейера. В общем, для ОоО-процессоров применимы любые комбинации или конфигурация блока и/или каскадов конвейера, известных в технике.

Одна проблема ОоО-процессоров состоит в том, что иногда важно или по меньшей мере полезно поддерживать некоторые инструкции в первоначальной очередности программы даже в пределах ОоО-части 106 процессора. Посредством примера, может иметь случай, когда ячейка памяти, отображенное значение ввода-вывода или другой ресурс должны только обновляться или иным образом иметь доступ первоначальной очередности программы. Характерно, если ячейка памяти обновляется с очередностью данных вместо очередности программы, то может возникнуть ошибка (например, запись более старой/предыдущей инструкции можно обновить на запись более новой инструкции, исполняемой с изменением ее очередности около более старой/предыдущей инструкции). Такая ошибка может привести к тому, что значения будут отличаться и не соответствовать целям первоначальной программы. В более общем смысле это может иметь место в любых из всевозможных ситуаций, в которых может возникнуть некорректный или противоречивый результат или может возникнуть некоторая другая проблема, если инструкции исполняются с изменением очередности (ОоО) и/или с очередностью данных вместо исполнения инструкции без изменения очередности и/или в очереди программы.

Обращаясь снова к фиг. 1, программа включает в себя пару инструкций 114 установления очередности исполнения инструкций. Пара инструкций установления очередности исполнения инструкций включает в себя инструкцию активации 116 и инструкцию установления 118. В некоторых вариантах осуществления инструкцию активации можно выполнить с возможностью заставлять или приводить процессор к активации установления очередности исполнения инструкций, и инструкцию установления можно выполнить с возможностью заставлять или приводить процессор к установлению очередности инструкций. Программа также включает в себя другие инструкции 120. Увеличение очередности 122 программы показано стрелкой, направленной вниз. В иллюстрированном варианте осуществления первоначальная очередность 122 программы обозначает, что инструкция 116 активации появляется перед инструкцией 118 установления в очереди программы. Более того, другие инструкции 120 происходят после инструкции установления в очереди программы. При желании одну или более инструкций (не показано) можно опционально включить в очередность программы между инструкциями активации и установления.

Как показано на иллюстрации, процессор также включает в себя модуль 110 установления очередности исполнения инструкций. Модуль установления очередности исполнения инструкций можно реализовать в виде аппаратных средств (например, в виде интегральной схемы, транзисторов или других элементов схемы и т.д.), программно-аппаратных средств (например, в виде микрокода или других инструкций более низкого уровня, хранящихся в энергонезависимой памяти), программного обеспечения (например, в виде инструкций более высокого уровня, которые хранятся в памяти) или их комбинаций (например, в виде аппаратных средств, потенциально объединенных с одним или более программно-аппаратными средствами и/или программным обеспечением).

В некоторых вариантах осуществления модуль 110 установления очередности исполнения инструкций, в ответ на пару инструкций 114 установления очередности исполнения инструкций, можно выполнить с возможностью предотвращения обработки других инструкций 120, появляющихся после инструкции 118 установления в очередности 122 программы перед инструкцией 116 активации, в части 106 с изменением очередности исполнения инструкций из процессора 100. Пара инструкций может побудить или привести процессор к установлению ограничения исполнения инструкций на инструкции или операции, выданные перед и после пары инструкций. В некоторых вариантах осуществления инструкцию 116 активации можно выполнить с возможностью активации установления очередности исполнения инструкций в заданном каскаде конвейера, таком, например, как каскад препроцессора 104 без изменения очередности исполнения инструкций. В дальнейшем будут описаны и рассмотрены различные способы активации установления очередности исполнения инструкций. В некоторых вариантах осуществления инструкцию 118 установления можно выполнить с возможностью установления очередности исполнения инструкций в заданном каскаде конвейера, таком, например, как каскад препроцессора 104 без изменения очередности исполнения инструкций. Например, в некоторых вариантах осуществления инструкцию установления можно приостановить в очереди в заданном каскаде конвейера и тем самым предотвратить, а также предотвратить другие более новые инструкции 120, их прохождение через конвейер за пределами данного каскада конвейера. Иногда в более поздний момент времени установление очередности исполнения инструкций можно деактивировать, и затем инструкции установления и другие более новые инструкции могут продолжить прохождение по конвейеру. Преимущественно, это может оказать помощь при установлении очередности исполнения инструкций, например, которая может быть полезна для упорядочивания доступа к ячейкам памяти или другим ресурсам.

Как упоминалось ранее, в некоторых вариантах осуществления инструкции активации и установления могут представлять собой инструкции из набора инструкций процессора. Преимущественно, при использовании двух инструкций из набора инструкций (то есть инструкций уровня набора инструкций) нет никакой необходимости выполнять операции или функции, связанные с очередностью исполнения инструкций, в виде микрокода. В одном аспекте это может стать преимуществом для процессора RISC и/или процессора, который не выполнен с возможностью использования микрокода (например, микроинструкции или микрооперации) для выполнения пары инструкций 114 установления очередности исполнения инструкций (например, процессор может и не использовать микрокод или может использовать только микрокод только лимитированным или ограниченным образом, который не подходит для реализации пары инструкций установления очередности исполнения инструкций). Однако инструкции можно также опционально использовать в CISC и других типах процессоров, включая процессоры, которые позволяют опционально реализовать пару инструкций установления очередности исполнения инструкций в микрокоде. Более того, пара инструкций может позволить специалисту-практику (например, программисту) или программному обеспечению гибко управлять ячейками в программе или коде пары инструкций для достижения желаемой очередности исполнения инструкций.

В некоторых вариантах осуществления, в отличие от некоторых типов инструкций, таких как инструкции сравнения и обмена и т.п., которые затрагивают только одиночный семафор, мьютекс или совместно используемую количественную переменную, варианты осуществления пары инструкций установления очередности исполнения инструкций позволяют упорядочить доступ к многочисленным, с любым количеством, адресам памяти. В некоторых вариантах осуществления, в отличие от некоторых инструкций защиты памяти или барьера памяти, варианты осуществления пары инструкций установления очередности исполнения инструкций могут устанавливать очередность в многочисленных, многих или любого количества различных типов инструкций вместо инструкций только доступа к памяти (например, загрузки памяти, сохранения в память, загрузки памяти и сохранения в память и т.д.). Более того, инструкции защиты памяти обычно устанавливают только очередность доступа к памяти. Напротив, варианты осуществления инструкций, раскрытых в данном документе, могут устанавливать очередность доступа к памяти, а также устанавливать очередность для других аспектов, таких, например, как доступ к регистрам, арифметические операции и/или время обработки инструкций. В дополнение, варианты осуществления инструкций, раскрытые в данном документе, позволяют устанавливать очередность в других ситуациях, в которых инструкции защиты памяти обычно не позволяют устанавливать очередность. В качестве примера рассмотрим устройство ввода/вывода (I/O), которое имеет два местоположения: первое местоположение X и второе местоположение Y. Запись X может разрешить считывание Y. Инструкции защиты памяти могут поддерживать взаимодействие между Y, который появляется спустя некоторое время после X, но не наоборот.

Во избежание излишнего усложнения описания процессор описан и показан в упрощенном виде. Процессор может опционально включать в себя другие известные компоненты, которые обычно используются в процессорах. Примеры таких компонентов включают в себя, но не ограничиваются ими, блок предсказания ветвлений, кэш-память данных и инструкций, кэш-память второго или более высокого уровня, буферы предварительной выборки для трансляции данных и инструкций, буферы предварительной выборки, блок переименования регистра, блок планирования инструкций, блоки шинного интерфейса, блок завершения, другие компоненты, включенные в процессоры, и различные их комбинации. В процессорах существуют в прямом смысле многочисленные различные комбинации и конфигурации компонентов, и варианты осуществления не ограничиваются какой-либо конкретной комбинацией или конфигурацией. Варианты осуществления могут быть включены в процессоры, имеющие многочисленные ядра, логические процессоры или исполнительные блоки, по меньшей мере один из которых выполнен с возможностью обработки пары инструкций установления очередности исполнения инструкций так, как это раскрыто в данном документе.

На фиг. 2 показана блок-схема последовательности операций варианта осуществления способа 226, выполняемого в процессоре для обработки или для выполнения варианта осуществления пары инструкций установления очередности исполнения инструкций. В различных вариантах осуществления способ можно выполнить с помощью процессора общего назначения, процессора специального назначения или другого устройства для обработки инструкций или цифрового логического устройства. В некоторых вариантах осуществления операции и/или способ, показанный на фиг. 2, можно выполнить с помощью и/или внутри процессора, показанного на фиг. 1. Компоненты, признаки и специфические опциональные детали, описанные в данном документе для процессора (фиг. 1), также опционально применимы для операций и/или способа (фиг. 2). Альтернативно, операции и/или способ (фиг. 2) можно выполнить с помощью и/или внутри аналогичного или другого процессора. Более того, процессор (фиг. 1) может выполнять операции и/или способы, подобные, аналогичные или различные чем операции и/или способы, показанные на фиг. 2.

Способ включает в себя прием пары инструкций установления очередности исполнения инструкций на этапе 227. В различных аспектах пару инструкций можно принимать в процессоре или его части (например, в блоке выборки инструкций, кэш-памяти инструкций, декодере и т.д.). В различных аспектах инструкцию можно принимать из источника вне кристалла (например, из памяти, межсоединения вне кристалла и т.д.) или из источника на кристалле (например, из кэш-памяти инструкций). Пара инструкций установления очередности исполнения инструкций может представлять собой часть набора инструкций процессора. В некоторых вариантах осуществления пара инструкций установления очередности исполнения инструкций может включать в себя инструкцию активации и инструкции установления. Обычно инструкция активации может появляться перед инструкцией установления в очереди программы.

Способ включает в себя, в ответ на пару инструкций установления очередности исполнения инструкций, предотвращение обработки инструкций, появляющихся после инструкции установления в очереди программы перед инструкцией активации в части с изменением очередности исполнения инструкций процессора на этапе 228. В некоторых вариантах осуществления этот способ может включать в себя активацию установления очередности исполнения инструкций, в ответ на инструкцию активации, в первом каскаде конвейера процессора (например, в каскаде препроцессора без изменения очередности исполнения инструкций процессора). В некоторых вариантах осуществления после активации установления очередности исполнения инструкций способ может включать в себя установление очередности исполнения инструкций путем предотвращения продвижения инструкции установления и инструкций, появляющихся после инструкции установления в очереди программы за пределами второго каскада конвейера (например, каскада препроцессора без изменения очередности исполнения инструкций процессора). В некоторых вариантах осуществления инструкцию установления можно удерживать в очереди (например, во втором каскаде конвейера) и можно предотвратить продвижение инструкций после инструкции установления в очереди программы около инструкции установления. Некоторое время спустя установление очередности исполнения инструкций можно деактивировать, и затем инструкция установления и инструкции после инструкции установления могут продвигаться по конвейеру.

Способ был показан и описан в относительно простом формате, но операции можно опционально добавить и/или удалить из способа. Например, в других вариантах осуществления способ может опционально включать в себя выборку инструкций, декодирование инструкций, планирование инструкций (например, планирование изменения очередности исполнения инструкции активации), исполнение инструкций, выполнение микроархитектурных операций, связанных с исполнением инструкций (например, модификацию одного или более разрядов, программирование или активацию счетчика и т.д.), фиксацию изменений инструкций и т.д.

На фиг. 3 показана блок-схема первого примерного варианта осуществления подходящего модуля 310 установления очередности исполнения инструкций. В некоторых вариантах осуществления модуль 310 установления очередности исполнения инструкций может быть включен в процессор (фиг. 1) и/или можно использовать для выполнения операции(й) или способа (фиг. 2). Альтернативно, модуль 310 установления очередности исполнения инструкций может быть включен в аналогичный или другой процессор и/или можно использовать для выполнения аналогичных или различных операций или способов. Более того, процессор (фиг. 1) может включать в себя аналогичный или другой модуль установления очередности исполнения инструкций чем тот, который показан на фиг. 3, и/или операцию(и) или способ (фиг. 2) можно выполнить с помощью аналогичного или другого модуля установления очередности исполнения инструкций, чем тот, который показан на фиг. 3.

Модуль 310 установления очередности исполнения инструкций включает в себя модуль активации 330. Модуль активации выполнен с возможностью инициирования или активации установления очередности исполнения инструкций в ответ на инструкцию 316 активации в первом каскаде 332 конвейера процессора. Как показано, в некоторых вариантах осуществления первый каскад 332 может находиться внутри препроцессора 304 без изменения очередности исполнения инструкций, хотя объем настоящего изобретения не ограничивается этим. Посредством примера, подходящие примеры первого каскада внутри препроцессора без изменения очередности исполнения инструкций включают в себя, но не ограничиваются ими, каскад выборки, каскад декодирования и каскад выделения или различные места, расположенные между ними. Альтернативно, другие каскады в препроцессоре без изменения очередности исполнения инструкций или другой участок процессора можно использовать опционально. Например, первый каскад может представлять собой каскад исполнения, каскад планирования или другой каскад. В некоторых вариантах осуществления активация может находиться в препроцессоре без изменения очередности исполнения инструкций, и деактивация может находиться в препроцессоре без изменения очередности исполнения инструкций секции с изменением очередности исполнения инструкций или постпроцессоре без изменения очередности исполнения инструкций. Если каскады конвейера, которые используются непосредственно инструкциями активации и установления, не гарантируют достаточного порядка во избежание сценария зависания (например, если инструкции активации и установления выдаются с очередностью таким образом, что возникает проблема), то в процессор можно включить некоторый другой механизм для обеспечения гарантии достаточного порядка во избежание таких сценариев зависания.

В этом первом примерном варианте осуществления активация установления очередности исполнения инструкций происходит с помощью одного или более разрядов 334 управления установлением очередности исполнения инструкций. Как показано, модуль активации может быть связан с одним или более разрядами 334 управления. В некоторых вариантах осуществления модуль активации можно выполнить с возможностью модификации или изменения одного или более разрядов 334 управления из первого состояния (например, начального двоичного значения) во второе другое состояние (например, другое двоичное значение) для активизации установления очередности исполнения инструкций. В качестве одного конкретного примера, модуль активации можно выполнить с возможностью установки единственного бита на двоичную единицу для активации установления очередности исполнения инструкций, тогда как одиночный разряд можно иным образом заменить на двоичный нуль при деактивации такого установления очередности исполнения инструкций.

Модуль 310 установления очередности исполнения инструкций также включает в себя модуль 336 блокирования. Модуль блокирования выполнен с возможностью, в ответ на инструкции активации и установлении при установлении очередности исполнения инструкций, установления очередности исполнения инструкций. В некоторых вариантах осуществления модуль блокирования можно выполнить с возможностью блокирования или предотвращения продвижения инструкции установления и других инструкций, возникающих после инструкции установления в очереди программы, за пределами второго каскада 340 конвейера. Как показано, в некоторых вариантах осуществления, второй каскад может находиться в отдельном каскаде, чем модуль активации, и модуль блокирования может быть соединен с модулем активации. В других вариантах осуществления второй каскад и/или модуль блокирования может находиться в том же самом каскаде, как и модуль активации. Посредством примера подходящие каскады для модуля блокирования включают в себя, но не ограничиваются ими, каскад выборки, каскад декодирования, каскад выделения, каскад планирования, каскад исполнения и различные места между ними. Альтернативно, можно опционально использовать и другие каскады.

Как показано, в этом первом примерном варианте осуществления модуль блокирования может включать в себя логическую схему 338 проверки разряда управления, связанную с разрядами управления. Логическая схема проверки разряда управления и/или модуль блокирования можно выполнить с возможностью считывания или осуществления доступа к разрядам управления для определения того, активируется или нет в текущий момент времени установление очередности исполнения инструкций. Как дополнительно показано, в этом первом примерном варианте осуществления модуль блокирования может включать в себя логическую схему 337 удержания инструкции (например, очередь, многопоточный ресурс, который совместно используется инструкциями из двух или более потоков и т.д.), которая выполнена с возможностью удержания инструкции установления. В некоторых вариантах осуществления, когда это определено, что установление очередности исполнения инструкций активирована, логическую схему удержания инструкции и/или модуль блокирования можно выполнить с возможностью удержания инструкции установления во втором каскаде 340 и предотвращения продвижения других инструкций после инструкции установления в очереди программы около инструкции установления и/или продвижения за пределы второго каскада. Конвейерное исполнение для потока, имеющего инструкции активации и установления и инструкции после инструкций установления, можно, по существу, приостановить или сделать паузу в течение периода времени. Во время этого периода времени инструкции из других потоков можно опционально поместить в конвейер, чтобы воспользоваться преимуществами неиспользованных слотов или каскадов конвейера.

В этом первом примерном варианте осуществления модуль 310 установления очередности исполнения инструкций может также включать в себя модуль 342 деактивации. В некоторых вариантах осуществления модуль деактивации можно выполнить с возможностью деактивации установления очередности исполнения инструкций, в ответ на инструкцию 316 активации, в третьем каскаде 344 конвейера. Как показано, в некоторых вариантах осуществления, модуль деактивации может быть связан с одним или более разрядами управления установлением очередности исполнения инструкций 334. В некоторых вариантах осуществления модуль деактивации может изменять или модифицировать разряды 334 управления из второго состояния, которое используется для индикации активации, в другое состояние (например, первое состояние), которое используется для индикации деактивации. Как показано, в некоторых вариантах осуществления, третий каскад может находиться внутри постпроцессора 308 без изменения очередности исполнения инструкций, хотя объем изобретения не ограничивается этим. Посредством примера, подходящие места в постпроцессоре без изменения очередности исполнения инструкций включают в себя, но не ограничиваются ими, каскад фиксации изменений, место после фиксации изменений, где сохранение является глобально видимым и известно для появления, но еще фактически не появилось, место после фиксации изменений, где сохранение фактически появилось, и различные места между ними. Альтернативно, можно опционально использовать другие места или каскады в конвейере процессора. После деактивации инструкция установления и другие последующие инструкции в очереди программы могут иметь возможность проходить дальше или продвигаться по конвейеру. В качестве другой опции, в некоторых вариантах осуществления инструкцию установления можно обработать после этого как неоперацию (NOP) во втором каскаде или в последующем каскаде.

На фиг. 4 показана блок-схема второго примерного варианта осуществления подходящего модуля 410 установления очередности исполнения инструкций. В некоторых вариантах осуществления модуль 410 установления очередности исполнения инструкций можно включить в процессор (фиг. 1) и/или можно использовать для выполнения операции(й) или способа (фиг. 2). Альтернативно, модуль 410 установления очередности исполнения инструкций можно включить в аналогичный или другой процессор и/или можно использовать для выполнения аналогичных или других операций или способов. Более того, процессор (фиг. 1) может включать в себя аналогичный или другой модуль установления очередности исполнения инструкций, например, показанный на фиг. 4, и/или операцию(и) или способ (фиг. 2) можно выполнить с помощью аналогичного или другого модуля установления очередности исполнения инструкций, например, который показан на фиг. 4.

Модуль 410 установления очередности исполнения инструкций включает в себя модуль 430 активации. Модуль активации выполнен с возможностью инициирования или активации установления очередности исполнения инструкций в ответ на инструкцию 416 активации в первом каскаде 432 конвейера процессора. Как показано, в некоторых вариантах осуществления первый каскад 432 может находиться в пределах препроцессора 404 без изменения очередности исполнения инструкций, хотя объем изобретения этим не ограничивается. Посредством примера подходящие примеры первого каскада, которые находятся в пределах препроцессора без изменения очередности исполнения инструкций, включают в себя, но не ограничиваются ими, каскад выборки, каскад декодирования и каскад выделения или различные места между ними. Альтернативно, можно использовать и другие каскады в препроцессоре без изменения очередности исполнения инструкций или другой части процессора. Например, первый каскад может представлять собой каскад исполнения, каскад планирования или другой каскад.

В этом втором варианте осуществления активация установления очередности исполнения инструкций выполняется посредством счетчика 448 установления очередности исполнения инструкций. Как показано, модуль 430 активации может быть соединен со счетчиком 448. В некоторых вариантах осуществления модуль активации можно выполнить с возможностью активации или инициирования счетчика для запуска подсчета до заданного или предварительно определенного значения для того, чтобы активировать установление очередности исполнения инструкций. Посредством примера счетчик может осуществлять отсчет от начального значения (например, нуля) до заданного или предварительного определенного значения остановки (например, нуля). В некоторых вариантах осуществления заданное или предварительно опре