Устройство выявления скрытых каналов на основе идентификации ошибок в тестируемых узлах автоматизированных систем

Иллюстрации

Показать всеИзобретение относится к области информационной безопасности. Технический результат заключается в выявлении скрытых каналов на основе идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств, в тестируемых узлах автоматизированных систем. В устройство выявления скрытых каналов введен блок выявления скрытых каналов, содержащий информационный вход, модуль выбора параметров скрытых каналов, модуль идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств, и модуль сигнализации о выявлении скрытого канала, информационный выход, причем вход модуля идентификации ошибок соединен с выходом компаратора напряжения, а выход модуля выбора параметров скрытых каналов - с входом модуля идентификации ошибок, выход которого соединен с входом модуля сигнализации о выявлении скрытого канала. 2 ил.

Реферат

1. Область техники, к которой относится изобретение

Изобретение относится к автоматике и вычислительной технике, а также к системам обеспечения информационной безопасности и может найти применение в качестве устройства выявления скрытых каналов (СК) на основе идентификации ошибок в тестируемых узлах автоматизированных систем.

2. Уровень техники

Известно устройство устранения группирования ошибок, включающее счетчик, триггер, первый элемент И и матрицу блоков сдвига, причем первые тактовые входы всех блоков сдвига соединены с выходом первого элемента И, первый вход которого соединен с тактовым входом устройства и со счетным входом счетчика, информационный вход устройства соединен с первым прямым входом блока сдвига, блок сдвига содержит регистр сдвига, элемент ИЛИ и первый и второй элементы И-ИЛИ, выходы которых соответственно соединены с прямым и инверсным входами регистра сдвига, тактовый вход которого соединен с выходом элемента ИЛИ, первый и второй входы которого являются соответственно первым и вторым тактовыми входами блока сдвига и соединены с первым и вторым входами первого и второго элементов И-ИЛИ, третьи входы которых являются первыми прямым и инверсным входами блока сдвига, вторые прямой и инверсный входы которого соответственно соединены с четвертыми входами первого и второго элементов И-ИЛИ, прямой и инверсный выходы сдвигового регистра соответственно являются прямыми и инверсными выходами блока сдвига (патент 77737 Российская Федерация, МПК H03M 13/00. Устройство устранения групповых ошибок [Текст] / Н.И. Елисеев, Ф.Г. Хисамов, С.А. Питько; заявитель и патентообладатель Краснодарское высшее военное училище. - №2007146548/22; заявл. 12.12.2007; опубл. 27.10.2008, бюл. №30).

К причинам, препятствующим достижению указанного ниже технического результата при использовании известного устройства, относится то, что известное устройство не обеспечивает возможности идентификации ошибок, возникающих в узлах автоматизированных систем для выявления скрытых каналов.

Наиболее близким устройством того же назначения к заявляемому изобретению по максимальному количеству сходных признаков является устройство выявления и предотвращения ошибок, возникающих в результате несанкционированных воздействий закладочных устройств (ЗУ), содержащее счетчик, триггер, первый элемент И, второй элемент И, третий элемент И и матрицу блоков сдвига, причем первые тактовые входы всех блоков сдвига соединены с выходом первого элемента И, первый вход которого соединен с тактовым входом устройства и со счетным входом счетчика, информационный вход устройства соединен с первым прямым входом блока сдвига, блок сдвига содержит регистр сдвига, элемент ИЛИ и первый и второй элементы И-ИЛИ, выходы которых соответственно соединены с прямым и инверсным входами регистра сдвига, тактовый вход которого соединен с выходом элемента ИЛИ, первый и второй входы которого являются соответственно первым и вторым тактовыми входами блока сдвига и соединены с первым и вторым входами первого и второго элементов И-ИЛИ, третьи входы которых являются первыми прямым и инверсным входами блока сдвига, вторые прямой и инверсный входы которого соответственно соединены с четвертыми входами первого и второго элементов И-ИЛИ, прямой и инверсный выходы сдвигового регистра соответственно являются прямыми и инверсными выходами блока сдвига, блок анализа информационного потока, в состав которого входит параметрический стабилизатор, компаратор напряжения и счетчик ошибок, причем вход параметрического стабилизатора соединен с выходом матрицы блоков сдвига, а выход параметрического стабилизатора соединен со входом компаратора напряжения, выход тестируемого устройства соединен со входом компаратора напряжения, выход которого соединен со входом счетчика ошибок, которое принято за прототип (патент 87592 Российская Федерация, МПК H03M 13/00. Устройство выявления и предотвращения ошибок, возникающих в результате несанкционированных воздействий закладочных устройств [Текст] / А.П. Сызранов, Н.И. Елисеев, А.В. Крупенин, О.Н. Мызников, И.В. Назаров; заявитель и патентообладатель Государственное образовательное учреждение высшего профессионального образования "Кубанский государственный технологический университет" (ГОУВПО "КубГТУ"). - №2009126206/22; заявл. 08.07.2009; опубл. 10.10.2009).

К причинам, препятствующим достижению указанного ниже технического результата при использовании прототипа, относится то, что известное устройство не обеспечивает возможности идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств, в тестируемых узлах автоматизированных систем для выявления скрытых каналов.

3. Раскрытие изобретения

Скрытый канал (covert channel): Не предусмотренный разработчиком системы информационных технологий и автоматизированных систем коммуникационный канал, который может быть применен для нарушения политики безопасности (ГОСТ Р 53113.1-2008 Информационная технология. Защита информационных технологий и автоматизированных систем от угроз информационной безопасности, реализуемых с использованием скрытых каналов. Общие положения. - М.: Стандарты, 2008. - Ч. 1).

Традиционные средства обеспечения информационной безопасности (ИБ), такие как средства разграничения доступа, межсетевые экраны, системы обнаружения вторжений, контролируют только информационные потоки, которые проходят по каналам, предназначенным для их передачи. Возможность обмена информацией вне этих рамок посредством скрытых каналов не учитывается.

В системах, требующих обеспечения повышенного уровня доверия, должны учитываться угрозы безопасности, возникающие вследствие наличия возможности несанкционированного действия с помощью СК.

Согласно ГОСТ Р 53113.1-2008: Опасность СК для информационных технологий и автоматизированных систем и других активов организации связана с отсутствием контроля средствами защиты информационных потоков, что может привести к утечке информации, нарушить целостность информационных ресурсов и программного обеспечения в компьютерных системах или создать иные препятствия по реализации информационных технологий. Для обеспечения защиты информации, обрабатываемой в автоматизированных системах, необходимо выявлять и нейтрализовывать все возможные информационные каналы несанкционированного действия, как традиционные, так и скрытые.

Задача, стоящая перед изобретателем, заключалась в создании устройства выявления скрытых каналов, которое обеспечивает выявление СК на основе идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств, в тестируемых узлах автоматизированных систем.

Ошибки второго вида в некоторых случаях могут не оказывать заметного влияния на работу узлов автоматизированных систем, при этом скрытые каналы не могут быть выявлены традиционными средствами защиты информации.

Указанный технический результат достигается тем, что известное устройство выявления и предотвращения ошибок, возникающих в результате несанкционированных воздействий закладочных устройств, содержит счетчик, триггер, первый элемент И, второй элемент И, третий элемент И и матрицу блоков сдвига, причем первые тактовые входы всех блоков сдвига соединены с выходом первого элемента И, первый вход которого соединен с тактовым входом устройства и со счетным входом счетчика, информационный вход устройства соединен с первым прямым входом блока сдвига, блок сдвига содержит регистр сдвига, элемент ИЛИ и первый и второй элементы И-ИЛИ, выходы которых соответственно соединены с прямым и инверсным входами регистра сдвига, тактовый вход которого соединен с выходом элемента ИЛИ, первый и второй входы которого являются соответственно первым и вторым тактовыми входами блока сдвига и соединены с первым и вторым входами первого и второго элементов И-ИЛИ, третьи входы которых являются первыми прямым и инверсным входами блока сдвига, вторые прямой и инверсный входы которого соответственно соединены с четвертыми входами первого и второго элементов И-ИЛИ, прямой и инверсный выходы сдвигового регистра соответственно являются прямыми и инверсными выходами блока сдвига, блок анализа информационного потока, в состав которого входит параметрический стабилизатор, компаратор напряжения и счетчик ошибок, причем вход параметрического стабилизатора соединен с выходом матрицы блоков сдвига, а выход параметрического стабилизатора соединен со входом компаратора напряжения, выход тестируемого устройства соединен со входом компаратора напряжения, выход которого соединен со входом счетчика ошибок.

Дополнительно в него введен блок выявления скрытых каналов, содержащий информационный вход, модуль выбора параметров скрытых каналов, модуль идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств, и модуль сигнализации о выявлении скрытого канала, причем вход модуля идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств, соединен с выходом компаратора напряжения, а выход модуля выбора параметров скрытых каналов - со входом модуля идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств, выход которого соединен со входом модуля сигнализации о выявлении скрытого канала, информационный выход.

Благодаря введению в известный объект совокупности существенных отличительных признаков устройство позволяет идентифицировать ошибки, искусственно вызванные в работе закладочных устройств либо возникающие в результате несанкционированных воздействий закладочных устройств, в тестируемых узлах автоматизированных систем и на основе данных, полученных в результате идентификации ошибок, выявить скрытые каналы.

Проведенный анализ уровня техники позволил установить, что аналоги, характеризующиеся совокупностью признаков, тождественные всем признакам заявленного технического решения, отсутствуют, что указывает на соответствие заявленного устройства условию патентоспособности «новизна». Результаты поиска известных решений в данной и смежных областях техники с целью выявления признаков, совпадающих с отличительными от прототипа признаками заявленного объекта, показали, что они не следуют явным образом из уровня техники. Из уровня техники также не выявлена известность влияния предусматриваемых существенными признаками заявленного изобретения преобразований на достижение указанного технического результата. Следовательно, заявленное изобретение соответствует условию патентоспособности «изобретательский уровень».

4. Краткое описание чертежей

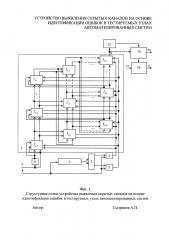

На чертежах представлено: на фиг. 1 изображена структурная схема устройства выявления скрытых каналов на основе идентификации ошибок в тестируемых узлах автоматизированных систем, состоящего из матрицы блоков сдвига 1, счетчика 2, триггера 3, первого элемента И 4, второго элемента И 5, третьего элемента И 6, информационного входа 7, входа тактовых импульсов 8, информационного выхода матрицы блоков сдвига 9, блока анализа информационного потока 10, информационного входа 15, блока выявления скрытых каналов 16, информационного выхода 20, информационного выхода 21; также представлен тестируемый узел 12.

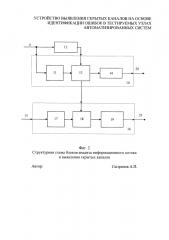

На фиг. 2 изображена структурная схема блока анализа информационного потока 10, состоящего из параметрического стабилизатора 11, компаратора напряжения 13, счетчика ошибок 14, информационного выхода 20 и блока выявления скрытых каналов 16, содержащего информационный вход 15, модуль выбора параметров скрытого канала 17, модуль идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств 18, модуль сигнализации о выявлении скрытого канала 19, информационный выход 21; также показан тестируемый узел 12.

5. Осуществления изобретения

Устройство выявления скрытых каналов на основе идентификации ошибок в тестируемых узлах автоматизированных систем содержит: матрицу блоков сдвига 1, счетчик 2, триггер 3, первый элемент И 4, второй элемент И 5, третий элемент И 6, информационный вход 7, вход тактовых импульсов 8, информационный выход матрицы блоков сдвига 9, блок анализа информационного потока 10, информационный вход 15, блок выявления скрытых каналов 16, информационный выход 20, информационный выход 21, представленные на фиг. 1, где также показан тестируемый узел 12; блок анализа информационного потока 10, состоящий из параметрического стабилизатора 11, компаратора напряжения 13, счетчика ошибок 14 и информационного выхода 20; и блок выявления скрытых каналов 16, содержащий информационный вход 15, модуль выбора параметров скрытого канала 17, модуль идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств 18, и модуль сигнализации о выявлении скрытого канала 19, информационный выход 21, изображенные на фиг. 2.

Устройство выявления скрытых каналов на основе идентификации ошибок в тестируемых узлах автоматизированных систем работает следующим образом. Входящая информация поступает через информационный вход 7 на вход третьего элемента И 6 (фиг. 1). Информация с выхода третьего элемента И 6 поступает на вход матрицы блоков сдвига 1, где происходит последовательное переписывание информации из первого блока сдвига во второй и далее в первый столбец матрицы блоков сдвига. Затем последовательно заполняет второй, третий, ..., n-й столбец. Матрица содержит n строк и m столбцов.

При поступлении n2×m бит информации происходит полное заполнение матрицы блоков сдвига. Одновременно с поступлением информации по информационному входу 7 поступают тактовые импульсы по входу тактовых импульсов 8, которые подсчитывает счетчик 2, и поступают через открытый первый элемент И 4 на первый тактовый вход блоков сдвига I, обеспечивая перезапись информации по столбцам. После поступления n2×m-го импульса счетчик 2 установлен в нулевое состояние и сигнал переполнения поступит на счетный вход триггера 3, который изменит свое состояние. После этого первый элемент И 4 закроется, а второй элемент И 5 откроется и тактовые импульсы будут поступать на тактовый вход блоков сдвига I. Это обеспечит сдвиг информации по строкам заданной длины, вызывая перемежение информации.

Дальнейшая запись поступающей по входу 7 информации и одновременное считывание ранее поступившей информации происходит последовательно по строкам, до тех пор пока счетчик 2 не выработает сигнал переполнения. Элементы И-ИЛИ и ИЛИ обеспечивают возможность сдвига информации в блоках сдвига по двум входам.

И одновременно с вводом информации через информационный вход 7 через вход 15 блока выявления скрытых каналов 16 осуществляется ввод данных о характеристиках скрытого канала, подлежащего выявлению (вид скрытого канала, параметры, при манипулировании которыми происходит передача информации и др.), в модуль выбора параметров скрытого канала 17 с выхода модуля выбора параметров скрытого канала 17 информация о выбранных параметрах скрытого канала поступает на вход модуля идентификации ошибок 18.

После этого информация с информационного выхода 9 матрицы блоков сдвига 1 поступает на информационный вход тестируемого узла 12 и одновременно на вход блока анализа информационного потока 10, изображенного на фиг. 2, откуда информация поступает на вход параметрического стабилизатора 11. После чего информация с выхода тестируемого узла 12 и выхода параметрического стабилизатора 11 поступает на вход компаратора напряжения 13. Далее в случае несовпадения информации сигнал об ошибке в работе закладочного устройства, находящегося в тестируемом узле, будет снят с выхода компаратора напряжения 13 и передан одновременно на вход счетчика ошибок 14 и вход модуля идентификации ошибок 18, в модуле идентификации ошибок происходит процесс идентификации ошибок (на основе ранее введенных данных о скрытом канале), возникших в закладочном устройстве в тестируемом узле 12. Информация о неидентифицированной ошибке будет снята с выхода счетчика ошибок 14 и поступит на информационный выход 20. В случае идентификации ошибки СК информация с выхода модуля идентификации ошибок 18 поступает на вход модуля сигнализации о выявлении скрытого канала 19. После чего сигнал о выявлении конкретного вида скрытого канала будет снят с выхода модуля сигнализации о выявлении скрытого канала 19 и поступит на информационный выход 21.

В случае если работа закладочного устройства в тестируемом узле 12 не нарушена, сигнал об ошибке в работе закладочного устройства не сформирован и ЗУ продолжает скрытую передачу, в таком случае им вносятся искажения в информационные сигналы, поступившие с выхода 9 матрицы блоков сдвига 1. Тогда анализ информационного потока осуществляется порядком, аналогичным описанному.

При отсутствии ошибок в информационном потоке информация будет передана для дальнейшей обработки.

Преимущество изобретения состоит в том, что выявление скрытых каналов происходит целенаправленно по выбранным параметрам на основе идентификации ошибок в узлах автоматизированных систем, что обеспечивает повышение эффективности борьбы со скрытыми каналами. Устройство обеспечивает выявление скрытых каналов на основе идентификации ошибок, как искусственно вызванных в работе закладочных устройств, так и возникающих в результате несанкционированных воздействий закладочных устройств, в тестируемых узлах автоматизированных систем. Ошибки второго вида могут не оказывать заметного влияния на работу узлов автоматизированных систем, вследствие чего их сложно выявить. Так как в настоящее время существуют различные виды скрытых каналов, которые не могут быть выявлены традиционными средствами защиты информации, а сбои или ошибки в работе узлов автоматизированных систем могут иметь различную природу происхождения, необходимо обеспечить целенаправленное противодействие СК, что позволит минимизировать деструктивные воздействия скрытых каналов.

Устройство выявления скрытых каналов на основе идентификации ошибок в тестируемых узлах автоматизированных систем содержит счетчик, триггер, первый элемент И, второй элемент И, третий элемент И и матрицу блоков сдвига, причем первые тактовые входы всех блоков сдвига соединены с выходом первого элемента И, первый вход которого соединен с тактовым входом устройства и со счетным входом счетчика, информационный вход устройства соединен с первым прямым входом блока сдвига, блок сдвига содержит регистр сдвига, элемент ИЛИ и первый и второй элементы И-ИЛИ, выходы которых соответственно соединены с прямым и инверсным входами регистра сдвига, тактовый вход которого соединен с выходом элемента ИЛИ, первый и второй входы которого являются соответственно первым и вторым тактовыми входами блока сдвига и соединены с первым и вторым входами первого и второго элементов И-ИЛИ, третьи входы которых являются первыми прямым и инверсным входами блока сдвига, вторые прямой и инверсный входы которого соответственно соединены с четвертыми входами первого и второго элементов И-ИЛИ, прямой и инверсный выходы сдвигового регистра соответственно являются прямыми и инверсными выходами блока сдвига, блок анализа информационного потока, в состав которого входит параметрический стабилизатор, компаратор напряжения и счетчик ошибок, причем вход параметрического стабилизатора соединен с выходом матрицы блоков сдвига, а выход параметрического стабилизатора соединен со входом компаратора напряжения, выход тестируемого устройства соединен со входом компаратора напряжения, выход которого соединен со входом счетчика ошибок, отличающееся тем, что введен блок выявления скрытых каналов, содержащий информационный вход, модуль выбора параметров скрытых каналов, модуль идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств, и модуль сигнализации о выявлении скрытого канала, причем вход модуля идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств, соединен с выходом компаратора напряжения, а выход модуля выбора параметров скрытых каналов - со входом модуля идентификации ошибок, искусственно вызванных в работе закладочных устройств либо возникающих в результате несанкционированных воздействий закладочных устройств, выход которого соединен со входом модуля сигнализации о выявлении скрытого канала, информационный выход.