Устройство для адаптивной оценки помехоустойчивости широкополосного радиоканала

Иллюстрации

Показать всеИзобретение относится к области электросвязи. Технический результат заключается в повышении надежности и помехоустойчивости радиоканала. Устройство содержит: анализатор принимаемых сигналов, два счетчика ошибок, блок сравнения, дешифратор, реверсивный счетчик, дешифратор номера состояния, регистр задания чисел, блок импульсных задержек, четыре элемента ИЛИ, счетчик импульсов, два элемента задержки, элемент И, управляемый генератор порога сравнения количества ошибок. 1 ил.

Реферат

Изобретение относится к области электросвязи и может быть использовано в аппаратуре контроля дискретных каналов связи.

Известны своим практическим использованием система для оценки помехоустойчивости телекоммуникационного комплекса, содержащая искусственный источник электромагнитных помех и датчик величины электромагнитного поля, расположенный в непосредственной близости к кабелю линии связи этого комплекса, взаимодействующие с этим кабелем путем измерения интегрального уровня помех, наведенных в линии связи этим источником, а также система для оценки помехоустойчивости телекоммуникационного комплекса.

Недостатком подобных устройств является отсутствие возможности выявления мест расположения побочных случайных источников электромагнитных помех, а также действующих электромагнитных наводок. В данных системах помехи, наведенные в линиях связи, возбуждены гармониками сигналов с широким спектром частот, которые экранируются гораздо сильнее низкочастотных помех. Также к недостаткам данных устройств следует отнести отсутствие возможности установить место фактического воздействия на линию связи относительно большой протяженности зоны влияния помехи. Это необходимо для реализации мероприятий, связанных с обеспечением электромагнитной совместимости. Такими мероприятиями могут быть, например, дополнительное экранирование или взаимный разнос трасс радиоканалов, взаимное перемещение источников помех и помехочувствительного оборудования [1].

Наиболее близким по технической сущности является система для оценки помехоустойчивости телекоммуникационного комплекса [2], принцип работы которой основан на фиксировании в цифровом формате временной зависимости спектрального состава полезного сигнала в линии связи телекоммуникационного комплекса на уровне спектрального состава помех.

Применение подобных устройств ограничивается сложностью поиска локации прохождения радиоволн линии радиосвязи и настройки необходимого диапазона частот, с целью того, чтобы не упустить основные составляющие широкополосного радиосигнала с для проведения достоверной оценки помехоустойчивости широкополосного радиоканала.

Задачей изобретения является повышение достоверности оценки помехоустойчивости широкополосного радиосигнала при резких изменениях состояния радиоканала.

Требуемый технический результат достигается тем, что в конструкцию изобретения вводится управляемый генератор порога сравнения количества ошибок.

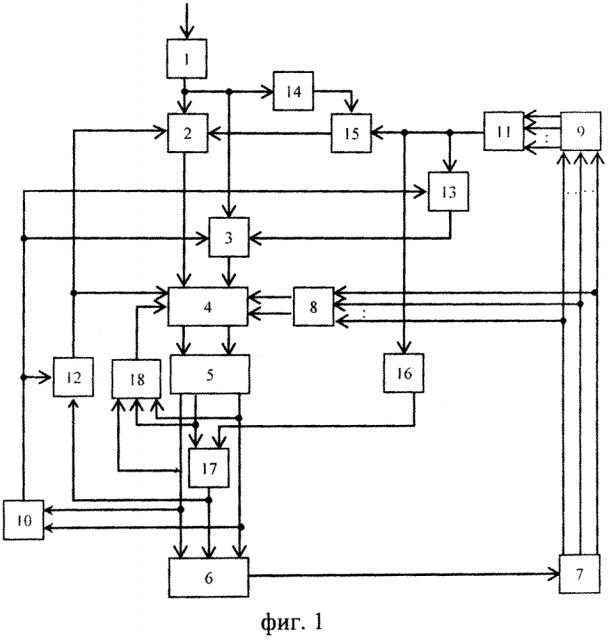

Сущность изобретения поясняется чертежом, где на фиг. 1 представлен возможный вариант построения устройства для адаптивной оценки помехоустойчивости широкополосного радиоканала, который в себе содержит:

1 - анализатор принимаемых сигналов

2, 3 - счетчики ошибок

4 - блок сравнения

5 - дешифратор

6 - реверсивный счетчик

7 - дешифратор номера состояния

8 - регистр задания чисел

9 - блок импульсных задержек

10, 11, 12, 15 - элемент ИЛИ

13 - счетчик импульсов

14, 16 - элементы задержки

17 - элемент И

18 - управляемый генератор порога сравнения количества ошибок

Устройство для адаптивной оценки помехоустойчивости широкополосного радиоканала работает следующим образом: осуществляется выборка n квазистационарных состояний, в течение которых статистические свойства канала связи считаются неизменными. Качеству i-го состояния канала соответствуют определенные длительности времени контроля: Ti - для определения момента перехода в (i-1)-е («худшее») состояние, задаваемое одной из n импульсных линий задержки блока 9 импульсных линий задержки; kTi - для определения момента перехода в (i+1)-е («лучшее») состояние канала.

Кроме того, заданы пределы числа ошибок для принятия решения о переходе из i-го в (i-1)-е или (i+1)-е состояния: Ni,i-1 и Ni,i+1 соответственно, записанные в одном из n регистров блока 8 регистров задания чисел.

Сигналы об обнаруженных ошибках с выхода анализатора 1 поступают на информационные входы первого 2 и второго 3 счетчиков ошибок, а также на вход первого элемента 14 задержки, время задержки которого равно времени срабатывания первого счетчика 2 ошибок. Через время , равное времени записи сигнала ошибки в счетчик 2 ошибок, с выхода первого элемента 14 задержки через четвертый элемент ИЛИ 15 на считывающий вход первого счетчика 2 ошибок поступает сигнал и подсчитанное первым счетчиком 2 ошибок текущее значение числа ошибок в канале связи Ni* перезаписывается в блок 4 сравнения, где сравнивается со значением числа ошибок Ni,i-1, полученным с блока 18 управляемого генератора порога сравнения количества ошибок. С блока 4 сравнения передается сигнал на вход дешифратора 5. При выполнении условия Ni*≤Ni,i-1, на втором выходе дешифратора 5 циклов измерений появляется импульс, который поступает на вход элемента И17. При отсутствии сигнала на другом входе элемента И17 он оказывается закрытым и изменений в состоянии блоков устройства не происходит. Сигнал на втором входе элемента И17 не появляется в течение времени контроля Ti. В течение времени контроля Ti на одном из трех выходов дешифратора 5 на вход блока 18 управляемого генератора порога сравнения количества ошибок поступает импульс запуска, после чего с блока 18 передается пороговое значение Ni,i-1 числа ошибок. По окончании времени контроля Ti, на i-выходе блока 9 импульсных линий задержки появляется импульс, который через второй 11 и четвертый 15 элементы ИЛИ поступает на считывающий вход первого счетчика 2 ошибок, а через второй элемент ИЛИ11 - на информационный вход счетчика 13 импульсов и на вход второго элемента 16 задержки, время задержки которого равно сумме времен срабатывания блока 4 сравнения и дешифратора 5 циклов измерения. Через указанное время на первом и втором входах элемента И17 появляются импульсы и импульс с его выхода поступает на установочный вход реверсивного счетчика 6 и через третий элемент ИЛИ12 на установочные входы первого счетчика 2 ошибок и блока 4 сравнения, в результате чего первый счетчик 2 ошибок и блок 4 сравнения обнуляются, а реверсивный счетчик 6 остается в i-м состоянии. Сигнал с реверсивного счетчика 6, соответствующий i-му состоянию канала, поступает на вход устройства передачи данных, которое в этом случае остается в прежнем режиме работы, и на вход дешифратора 7 номеров состояния, сигнал с i-го выхода которого поступает на i-е выходы блока 8 регистров задания чисел и блока 9 импульсных линий задержки. С i-го регистра блока 8 регистров задания чисел в блок 4 сравнения записываются прежние значения Ni,i-1 и Ni,i+1, а через i-ю импульсную линию задержки блока 9 по истечении времени Ti через второй 11 и четвертый 15 элементы ИЛИ поступает импульс на считывающий вход первого счетчика 2 ошибок, а через второй элемент ИЛИ 11 - на информационный вход счетчика 13 импульсов и на вход второго элемента 16 задержки.

Если за K последовательных измерений длительностью Ti, на выборках число ошибок, подсчитанное первым счетчиком 2 ошибок, не превышает предельного числа ошибок Ni,i-1 для принятия решения о переходе из i-го в (i-1)-е состояние, то по приходу K-го импульса на вход счетчика 13 импульсов, рассчитанного на (K-1) импульс, счетчик 13 переполняется и с его выхода переполнения поступает импульс на считывающий вход второго счетчика 3 ошибок, с выхода которого подсчитанное за время kTi число ошибок Ni(K) переписывается в блок 4 сравнения, где сравнивается с пределом числа ошибок Ni,i+1 для принятия решения о переходе из i-го в (i+1)-e состояние. При Ni*≤Ni,i+1 на третьем выходе дешифратора 5 циклов измерения появляется импульс, который поступает на вход суммирования реверсивного счетчика 6, через первый элемент ИЛИ10 - на установочные входы второго счетчика 3 ошибок и счетчика 13 импульсов, а через первый 10 и третий 12 элементы ИЛИ - на установочные входы блока 4 сравнения и первого счетчика 2 ошибок, в результате чего первый 2 и второй 3 счетчики ошибок, счетчик 13 импульсов, блок 4 сравнения обнуляются, а реверсивный счетчик 6 переводится в (i+1)-е состояние. Сигнал с реверсивного счетчика 6, соответствующий (i+1)-му состоянию канала, поступает на выход устройства (для перенастройки аппаратуры передачи данных на (i+1)-й режим работы) и на вход дешифратора 7 номеров состояния, сигнал с (i+1)-го выхода которого поступает на (i+1)-е входы блока 8 регистров задания чисел и блока 9 импульсных линий задержки. С (i+1)-го регистра блока 8 регистров задания чисел в блок 4 сравнения записываются значения Ni+1,i и Ni+1,i+2, а через (i+1)-ю импульсную линию задержки блока 9 по истечении времени Ti+1 через второй 11 и четвертый 15 элементы ИЛИ поступает импульс на считывающий вход первого счетчика 2 ошибок, а через первый элемент ИЛИ 11 - на информационный вход счетчика 13 ошибок и вход второго элемента 16 задержки.

При выполнении условия Ni*>Ni,i-1, на первом выходе дешифратора 5 циклов измерения появляется импульс, который поступает на вход вычитания реверсивного счетчика 6 и через первый элемент ИЛИ10 на установочные входы второго счетчика 3 ошибок и счетчика 13 импульсов, а через первый 10 и третий 12 элементы ИЛИ - на установочные входы первого счетчика 2 ошибок и блока 4 сравнения, в результате чего первый 2 и второй 3 счетчики ошибок, счетчик 13 импульсов и блок 4 сравнения обнуляются, а реверсивный счетчик 6 переводится в (i-1)-е состояние. Сигнал с реверсивного счетчика 6, соответствующий (i-1)-му состоянию канала, поступает на выход устройства (например, в аппаратуру передачи данных для ее перенастройки на (i-1)-й режим работы) и на вход дешифратора 7 номера состояния, сигнал с (i-1)-го выхода которого поступает на (i-1)-е входы блока 8 регистров задания чисел и блока 9 импульсных линий задержки. С (i-1)-го регистра блока 8 регистров задания чисел в блок 4 сравнения записываются значения Ni-1,i-2 и Ni-1,i.

Таким образом, принятие решения о переходе в «худшее» состояние осуществляется непосредственно при выполнении условия Ni*>Ni,i-1, не дожидаясь, когда закончится заданный интервал контроля Ti, что повышает достоверность результатов контроля. При этом наибольший эффект достигается при резких изменениях качества канала связи.

Источники информации

1 Томаси У., Электронные системы связи. М.: Техносфера, 2007, - 863 с.

2. RU 2436110, 2011 г.

Устройство для адаптивной оценки помехоустойчивости широкополосного радиоканала, состоящее из анализатора принимаемых сигналов, двух счетчиков ошибок, блока сравнения, дешифратора, реверсивных счетчиков, дешифратора номера состояния, регистра задания чисел, блока импульсных задержек, четырех элементов ИЛИ, счетчика импульсов, двух элементов задержки, элемента И, отличающееся тем, что в него дополнительно введен управляемый генератор порога сравнения количества ошибок, причем выход анализатора принимаемых сигналов соединен со входами счетчика ошибок и элемента задержки, выход счетчика ошибок соединен со входом блока сравнения, выходы которого, в свою очередь, соединены со входами дешифратора, выходы которого соединены с управляемым генератором порога сравнения количества ошибок, с входами реверсивного счетчика, с входами элемента ИЛИ и со входом элемента И, выход которого соединяется с входом реверсивного счетчика и с входом элемента ИЛИ, выход которого, в свою очередь, соединен с входом блока сравнения и с входом счетчика ошибок, выход элемента ИЛИ соединен со входами элемента ИЛИ, счетчика ошибок, счетчика импульсов, выход которого соединен со входом счетчика ошибок, выход которого, в свою очередь, соединен со входом блока сравнения, выход реверсивного счетчика соединен со входом дешифратора номера состояния, выходы которого соединены со входами блока импульсных задержек, выходы которого, в свою очередь, соединены со входами элемента ИЛИ, выход которого соединен со входом счетчика импульсов и со входом элемента ИЛИ, выход которого соединен со входом счетчика ошибок, выходы дешифратора номера состояния также соединены со входами регистра задания чисел, выходы которого соединены со входом блока сравнения, выход элемента ИЛИ также, в свою очередь, соединен со входом элемента задержки, выход которого соединен со входом элемента И, выход управляемого генератора порога сравнения количества ошибок соединен со входом блока сравнения, а выход элемента задержки соединен со входом элемента ИЛИ.