Управление синхронизацией для несогласованного приемника сигнала

Иллюстрации

Показать всеГруппа изобретений относится к запоминающим устройствам и может быть использована для управления синхронизацией для записи в запоминающие устройства в несогласованной архитектуре. Техническим результатом является компенсация изменений задержки реальной сети распределения тактового сигнала. Устройство содержит схему приемника и схему кольцевого генератора. Схема приемника включает в себя путь передачи данных и сеть распределения тактового сигнала в несогласованной конфигурации. Схема кольцевого генератора включает в себя реплику сети распределения тактового сигнала, согласованную с реальной сетью распределения тактового сигнала. 3 н. и 17 з.п. ф-лы, 10 ил.

Реферат

Область техники, к которой относится изобретение

Варианты осуществления изобретения, в общем, относятся к записи в запоминающие устройства и, более конкретно, к управлению синхронизацией для записи в запоминающие устройства в несогласованной архитектуре.

Уведомление об авторских правах/разрешении

Части раскрытия данного патентного документа могут содержать материал, который защищен авторскими правами. Владелец авторских прав не возражает против воспроизведения любым лицом патентного документа или патентного раскрытия, в том виде, как он представлен в патентном файле Ведомства управления по патентам и товарным знакам или в записях, но в остальном сохраняет все авторские права. Уведомление о защите авторских прав относится ко всем данным, представленным ниже, и к приложенным чертежам, а также к любому программному средству, описанному ниже: Copyright © 2013, Intel Corporation, All Rights Reserved.

Уровень техники

Передача данных между компонентами на платформе главного устройства необходима для работы электронного устройства. Однако различные условия влияют на временные характеристики высокоскоростной передачи данных между компонентами, такие как изменения температуры и вариации напряжения. Обычно передача данных между разными компонентами может называться I/O (вводом/выводом) и часто управляется стандартами (например, между компонентами подсистемы памяти). Стандарты I/O могут относиться к рабочим характеристикам для мощности I/O, задержки I/O и частоты I/O. Стандарты или номинальные значения установок рабочих характеристик I/O установлены на значения, которые могут быть достигнуты в разных системах для обеспечения совместимости и возможности взаимодействия. Как правило, существует компромисс между мощностью и задержкой. Таким образом, используя жестко выдержанные временные параметры, может уменьшить мощность, но это приводит к большей степени отрицательного влияния на задержку I/O со стороны температуры, напряжения и вариаций обработки.

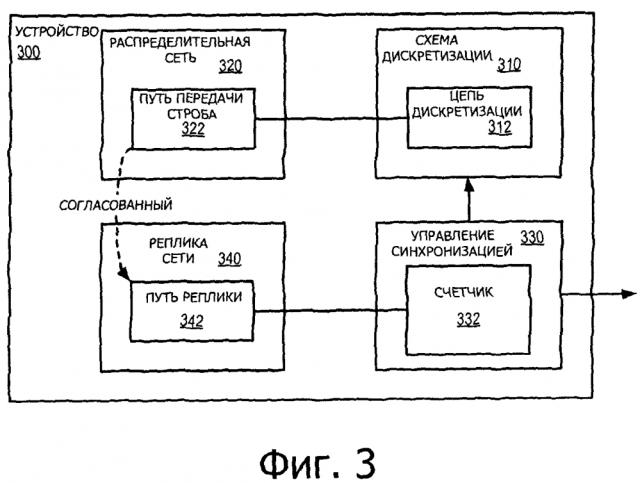

В подсистемах памяти обычно используется согласованная архитектура, где как путь передачи данных (DQ), так и путь данных строба (DQS) усиливается согласованными усилителями с непрерывным временем работы. На фиг. 1А показана блок-схема известной схемы согласованного приемника. В согласованной архитектуре 102 усилитель 124 пути строба согласован с усилителем 122 пути данных. Путь данных включает в себя ввод данных DQ [7:0], подаваемых в усилитель 122 с внутренним сигналом 110 Vref. Путь данных строба включает в себя входы для дифференциального приемника, где DQS_P представляет положительный дифференциальный сигнал, и DQS_N представляет отрицательный дифференциальный сигнал. Усилитель 124 передает сигнал в сеть 130 распределения тактовой частоты, которая образует сеть для распределения сигнала тактовой частоты для множества устройств приемников одновременно. В частности, показан сигнал, поступающий в элементы 142 и 144 схемы 140 выборки.

Используя несогласованную архитектуру, можно улучшить мощность приемника и рабочие характеристики по сравнению с использованием согласованной архитектуры. На фиг. 1В показана блок-схема известной схемы несогласованного приемника. В несогласованной архитектуре 104, выборку напряжения данных (DQ) выполняют непосредственно на выводе. После выборки система может усиливать сигнал без жестких ограничений по синхронизации, необходимых для согласованной архитектуры 102. А именно, усиление может происходить по всему UI (единичному интервалу) или, возможно, больше. Таким образом, требования к усилению/полосе пропускания несогласованного приемника слабее, чем у согласованного приемника. Как представлено, DQ [7:0] и интервал Vref 110 поступают непосредственно к элементам 162 и 164 схемы 160 выборки. Путь DQS все еще требует постоянно работающего усилителя, усилителя 126, но переход на DQS обычно является большим, чем переход на DQ, что означает, что можно использовать усилитель 126 с меньшим коэффициентом усиления, поскольку он не обязательно должен быть согласован с усилителем с высоким коэффициентом усиления на пути данных.

Несогласованная архитектура 104 улучшает определенное значение полосы пропускания и чувствительности к напряжению приемника по сравнению с согласованной архитектурой 102, но ухудшает управление синхронизацией. Задержка на путях DQS и DQ не является самокомпенсирующейся в несогласованной архитектуре 104. Таким образом, любое изменение в TDQS или во времени распространения сигнала строба через усилитель 124 или сеть 130 распределения тактовой частоты приводит к непосредственному ухудшению бюджета временных характеристик приемника. Существующая тренировка может скорректировать синхронизацию один раз, но любой дрейф от полученного в результате тренировки положения непосредственно влияет на запас синхронизации. Дрейф может возникнуть по напряжению, температуре и/или в результате старения, что может привести к ухудшению запасов по синхронизации и, возможно, может привести к неудачному соединению.

Известна периодическая тренировка, при которой данные после тренировки записывают через соединение (например, из контроллера памяти в DRAM (динамическое оперативное запоминающее устройство)) и проверяют на наличие ошибок. Однако периодическая тренировка является сложной и составляет нагрузку на полосу пропускания шины. Кроме того, тренировка могла бы быть наиболее эффективной, если бы выполнялось усреднение большого количества выборок, но усреднение большего количества выборок приводит к непосредственным конфликтам с желанием обеспечить широкую полосу пропускания для соединения данных, которая используется для реальных операций с данными. Кроме того, такая периодическая тренировка по своей сути является медленной из-за итеративного свойства контура обратной связи, для которого требуется выполнять поиск множества установок для определения оптимального значения.

Краткое описание чертежей

В следующем описании представлено описание фигур, на которых показаны иллюстрации, представленные в качестве примера выполнения вариантов осуществления изобретения. Чертежи следует понимать, как пример, а не как ограничение. Используемые здесь ссылки на один или больше "вариантов осуществления" требуется понимать, как описывающие определенные свойства, структуры и/или характеристики, включенные в, по меньшей мере, один вариант выполнения изобретения. Таким образом, такие фразы как "в одном варианте осуществления" или "в альтернативном варианте осуществления", появляющиеся здесь, описывают различные варианты осуществления и варианты выполнения изобретения, и не обязательно все относятся к одному и тому же варианту осуществления. Однако они не обязательно также являются взаимно исключающими.

На фиг. 1А показана блок-схема известной согласованной схемы приемника.

На фиг. 1В показана блок-схема известной несогласованной схемы приемника.

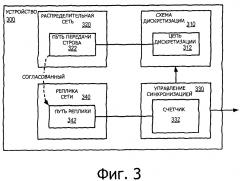

На фиг. 2 показаны блок-схема варианта осуществления системы, имеющей несогласованную схему приемника, и путь распределения реплики тактовой частоты.

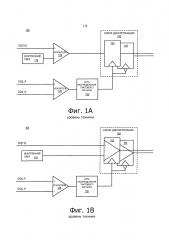

На фиг. 3 показана блок-схема варианта осуществления системы, имеющей реплику сети для пути распределения реплики тактовой частоты для несогласованной схемы приемника.

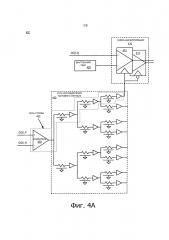

На фиг. 4А показана блок-схема варианта осуществления несогласованной схемы приемника.

На фиг. 4В показана блок-схема варианта осуществления схемы генератора с путем распределения реплики тактовой частоты для несогласованной схемы приемника по фиг. 4А.

На фиг. 5 показана временная диаграмма варианта осуществления временных характеристик операции для схемы генератора с путем распределения реплики тактовой частоты.

На фиг. 6 показана блок-схема последовательности операций варианта осуществления обработки для регулирования задержки сети распределения тактовой частоты на основе детектированных изменений задержки в сети распределения реплики тактовой частоты.

На фиг. 7 показана блок-схема варианта осуществления вычислительной системы, в которой может быть выполнен путь распределения реплики тактовой частоты.

На фиг. 8 показана блок-схема варианта осуществления мобильного устройства, в котором может быть выполнен путь распределения реплики тактовой частоты.

Описания некоторых деталей и вариантов выполнения следуют далее, включая в себя описание фигур, на которых могут быть представлены некоторые или все варианты осуществления, описанные ниже, так же как обсуждение других потенциальных вариантов осуществления или вариантов выполнения представленных здесь изобретательных концепций.

Подробное описание изобретения

Как описано здесь, в интерфейсе I/O из компонента в компонент используется несогласованная схема приемника. Несогласованный приемник включает в себя путь распределения реплики тактовой частоты, согласованный с путем распределения тактовой частоты, который управляет схемой выборки. В описании, "путь распределения тактовой частоты" относится к любой или всем частям пути, включая в себя сам путь распределения тактовой частоты, усилитель или другие части пути. Устройство может отслеживать изменения по задержке на пути реплики и регулировать задержку на реальном пути распределения тактовой частоты в ответ на изменения задержки, детектируемые на пути реплики. Схема приемника включает в себя путь данных и сеть распределения тактовой частоты в несогласованной конфигурации. Схема кольцевого генератора включает в себя сеть распределения реплики тактовой частоты, согласованную с реальной сетью распределения тактовой частоты. Таким образом, изменения задержки, детектируемые для сети распределения реплики тактовой частоты, обозначают изменение в задержке сети распределения реальной тактовой частоты, которая может быть компенсирована, соответственно.

В одном варианте осуществления описанная система тестирования или механизм тестирования могут использоваться для тестирования крупных узлов системы памяти и, более конкретно, I/O (ввода-вывода) или обмена данными между компонентом платформы (например, процессором, контроллером памяти) и запоминающим устройством. Любая подсистема памяти, в которой используется контроллер памяти с планировщиком или эквивалентной логикой, может быть воплощена, по меньшей мере, в одном варианте осуществления механизма тестирования. Ссылка, сделанная здесь на запоминающие устройства, может включать в себя разные типы памяти. Например, в качестве системы памяти, в общем, используют DRAM, которое представляет собой один пример запоминающие устройства, как описано здесь. Таким образом, механизм тестирования, описанный здесь, является совместимым с любым из множества технологий памяти, таких как DDR3 (двойная скорости передачи данных, версия 3, оригинальный выпуск компании JEDEC (Объединенный инженерный совет по электронным устройствам) от 27 июня 2007 г., в настоящее время выпуск 21), DDR4 (DDR версия 4, исходная спецификация, опубликованная в сентябре 2012 г. компанией JEDEC), LPDDR4 (версия 4 с двойной скоростью передачи данных, низким уровнем питания, спецификация в развитие JEDEC, в соответствии с подачей данной заявки), WIDEIO (спецификация развивающегося JEDEC, в соответствии с подачей настоящей заявки) и/или другие, и технологиями, основанными на производных или расширениях таких спецификаций.

В одном варианте осуществления операцией схемы интерфейса I/O можно дополнительно управлять через использование эмпирического тестирования. На основе изменений задержки, детектируемой путем распределения реплики тактовой частоты, система может эмпирически тестировать параметры рабочих характеристик устройства I/O (ввода/вывода) для определения, какой параметр (параметры) следует модифицировать для регулирования детектируемой задержки. На основе эмпирического тестирования через систему тестирования система может устанавливать параметры рабочих характеристик, специфичных для системы или устройства, в котором происходит передача данных между устройствами. Для каждой из множества разных установок, для множества разных параметров схемы I/O, система тестирования может устанавливать значение для каждого параметра схемы I/O, генерировать трафик тестирования для нагрузочных испытаний передачи данных со значением (значениями) параметра, и измерять рабочий запас для рабочих характеристик I/O. Система тестирования может дополнительно выполнять функцию поиска для определения значения для каждого параметра схемы I/O, в котором компенсируется задержка. В одном варианте осуществления система устанавливает значения рабочего цикла для параметров схемы I/O на основе функции поиска. Установки могут динамически изменяться для определенных компонентов конкретных систем на основе тестирования.

Как указано выше, несогласованная архитектура может обеспечивать существенные улучшения в полосе пропускания и по частоте в отношении согласованной архитектуры. Однако, на традиционную несогласованную архитектуру оказывает отрицательное влияние ухудшение управления синхронизацией. Как более подробно описано ниже, архитектура несогласованного приемника может иметь улучшенное управление синхронизацией в результате использования пути распределения согласованной реплики тактовой частоты, используемой для прогнозирования изменений во временной характеристике для пути распределения реальной тактовой частоты. В одном варианте осуществления система может регулировать поведение временных характеристик пути распределения реальной тактовой частоты на основе изменений временных характеристик, детектируемых на пути реплики. Более конкретно, можно предполагать, что изменения во временных характеристиках, детектируемых для пути реплики, имеют равный эффект на краю (краях) индикаторной диаграммы данных для реального пути данных. Таким образом, путем отслеживания изменений во временных характеристиках на пути реплики можно компенсировать изменения на кромке (кромках) индикаторной диаграммы данных.

В одном варианте осуществления схема приемника предоставляет информацию обратно в передатчик для обеспечения возможности регулирования передатчиком своей операции на основе детектируемых изменений задержки. Таким образом, изменения задержки могут быть компенсированы путем изменения поведения при передаче устройством передатчика. В одном варианте осуществления устройство приемника может рассчитывать требуемую регулировку задержки и/или регулировать задержку приемника для компенсации изменений задержки. В одном варианте осуществления устройство приемника просто передает необработанные данные в форме величины подсчета генератора в передатчик, который может затем рассчитывать регулировку временных характеристик на основе детектируемых изменений.

На фиг. 2 показана блок-схема варианта осуществления системы, имеющей схему несогласованного приемника, и путь распределения тактовой частоты реплики. Система 200 включает в себя устройство 210, которое показано с передающими аппаратными средствами ТХ 212, и устройство 220, которое показано с приемными аппаратными средствами 222. Следует понимать, что в одном примерном варианте осуществления устройство 220 также может передавать данные в устройство 210; таким образом, устройство 220 может включать в себя передающие аппаратные средства, которые не показаны в явном виде, и устройство 210 может включать в себя приемные аппаратные средства, которые не показаны в явном виде. В одном варианте осуществления, передающие и приемные аппаратные средства представляют собой аппаратные средства приемопередатчика, которые позволяют формировать интерфейс, как при передаче, так и при приеме. Устройства соединены через одну или больше линий передачи, которые управляются возбудителем передачи. Линия передачи может представлять собой любого типа линию передачи сигнала (например, трассу, провод), соединяющую I/O устройства 210 с устройством 220.

Устройство 220 включает в себя приемный контроллер 230, который представляет собой аппаратные средства и другие логические схемы, которые выполняют операции приема для устройства 220. Контроллер 230 приема может включать в себя схему 232 выборки для выборки уровней напряжения принимаемого сигнала. Схемой 232 выборки управляют по стробу 234 выборки или по другому сигналу управления, который обозначает, когда следует выполнить выборку поступающего или принимаемого сигнала. Контроллер 230 приема генерирует строб 234 выборки, как отдельный сигнал. Контроллер 230 приема включает в себя управление 236 синхронизацией для управления генерированием строба 234 выборки.

В одном варианте осуществления контроллер 230 приема включает в себя реплику 238 строба, которая представляет собой путь реплики строба 234 выборки. Дрейф (положительный или отрицательный) во временных характеристиках строба 234 выборки может отрицательно влиять на способность устройства 230 успешно принимать входящий сигнал. Реплика 238 строба представляет собой путь, который согласован с путем строба 234 выборки. Таким образом, такой же дрейф может возникать в выборке 234 строба, который может возникнуть эквивалентно в реплике 238 строба. На основе такого дрейфа или изменения в задержке сигнала строба или сигнала управления, управление 236 временными характеристиками можно регулировать для его изменения. В одном варианте осуществления в управлении 236 временными характеристиками регулируют задержку с помощью устройства 210 передачи сигналов для изменения его параметров передачи, с тем, чтобы лучше согласовать временные характеристики выборки схемы 232 выборки. Таким образом, управление 214 временными характеристиками устройства 210 позволяет регулировать операцию ТХ 212. В одном варианте осуществления управление 236 временными характеристиками регулирует временные характеристики выборки 234 строба для регулирования временных характеристик схемы 232 выборки. Таким образом, система 200 управляет временными характеристиками схемы приема устройства 220 в отношении схемы передачи устройства 210.

Предполагая, в качестве одного примера, что устройство 210 представляет собой контроллер или процессор памяти, и устройство 220 представляет собой запоминающее устройство, можно сказать, что система 200 относится к тому, как измерять задержку tDQS (задержку на распространение сигнала строба данных), и регулировать временные характеристики передатчика контроллера/процессора для компенсации изменений в задержке. В результате использования реплики 238 строба, как в отдельной схеме, система 200 может измерять дрейф сигнала строба без влияния на нормальную операцию. Таким образом, система измерения может обеспечить обратную связь точно на величину изменения задержки строба, предоставляя как магнитуду, так и величину дрейфа. Кроме того, поскольку реплика 238 строба представляет собой отдельную схему, которая не влияет на рабочие характеристики фактического канала передачи данных, система 200 выполнена с возможностью генерировать множество выборок измерений задержки для совместного усреднения, что может существенно улучшить разрешение и точность для системы, в которой используется сам путь данных для измерений.

Следует понимать, что путь схемы строба 234 выборки не согласован со схемой 232 выборки. Таким образом, контроллер 230 приема использует архитектуру схемы несогласованного приемника. Несогласованная архитектура обычно чувствительна к изменениям температуры и напряжения, таким образом, что поведение схемы (и в частности, задержки) изменяется с течением времени. Однако, отслеживание изменения задержки, используя реплику 238 строба, позволяет системе 200 регулировать задержку сигнала строба, что, в свою очередь, регулирует точку выборки. В противном случае, в точке выборки мог бы возникнуть дрейф, приводящий к выборкам в неправильной части сигнала и, в результате чего, возникали бы ошибки приема.

В одном варианте осуществления, система 200 использует измерения задержки в качестве входных сигналов, для выполнения поиска, который, в частности, определяет установку для работающей системы, для улучшения I/O. На основе измеренного значения задержки, и, возможно, других измеренных параметров I/O, логика поиска (которая может представлять собой часть логики тестирования или может представлять собой отдельную логику), определяет по измеренным значениям, какие установки следует использовать для I/O между устройствами. В одном варианте осуществления логика поиска позволяет использовать измерения для генерирования одной или больше представительных рабочих характеристик для I/O. На основе представительных кривых логика может выполнять функцию поиска для определения, какие установки следует использовать так, чтобы они удовлетворяли лучшие характеристики для, по меньшей мере, одного параметра, при этом с поддержанием, по меньшей мере, требуемых (стандартом или конфигурацией) рабочих характеристик для других. Логика поиска может включать в себя любую из N-мерной логики поиска, 1-мерной логики поиска (для выполнения n 1-мерных поисков), логики поиска линейного соответствия, логики поиска квадратичного соответствия, логики поиска наискорейшего спуска, логики поиска соответствия кривой или другие. Следует понимать, что n представляет собой целое число, обозначающее количество комбинаций для поиска. В одном варианте осуществления логика поиска может также комбинировать множество результатов измерений вместе, либо для уменьшения повторяемости шумов, или для экстраполяции по условиям наихудшего случая.

На фиг. 3 показана блок-схема варианта осуществления системы, имеющей реплику сети для пути распределения тактовой частоты реплики, для схемы несогласованного приемника. Устройство 300 представляет собой один пример варианта осуществления системы 200 на фиг. 2. Устройство 300 включает в себя схему 310 выборки для выборки принимаемого или входящего сигнала из передающего устройства (не показано). Временными характеристиками выборки схемы 312 выборки управляют на пути 322 строба, который представляет собой часть распределительной сети 320. Как представлено, схема 312 выборки может представлять собой одну из множества схем выборки схемы 310 выборки устройства 300. Как правило, временные характеристики одного пути 322 строба могут обозначать временные характеристики для всех путей строба распределительной сети 320, и, таким образом, временные характеристики для всех схем 310 выборки.

Путь 342 реплики согласован с путем 322 строба. Аналогично тому, как временные характеристики пути 322 строба обозначают временные характеристики всей распределительной сети 320, временные характеристики пути 342 реплики обозначают путь 322 строба, и, таким образом, распределительной сети 320. Путь 342 реплики обозначен, как часть сети 340 реплики. В одном варианте осуществления реплика сети 340 представляет собой эквивалентную схему для распределительной сети 320, а не всей сети. Таким образом, реплику пути 342 и реплику сети 340 можно рассматривать, как одно и то же в некоторых вариантах осуществления.

В одном варианте осуществления реплика пути 342 представляет собой или включает в себя схему генератора, которая передает по обратной связи сигнал в усилитель в начале пути. Количество колебаний за заданный период времени может предоставлять значение, которое обозначает временные характеристики реплики пути 342. В результате сравнения количества колебаний в одном тесте с ранее сохраненным значением, устройство 300 может определять магнитуду и знак изменений задержки в пути. В одном варианте осуществления управление 330 временными характеристиками включает в себя счетчик 332 для подсчета колебаний варианта осуществления реплики пути 342, который включает в себя генератор или кольцевой генератор. В одном варианте осуществления управление 330 временными характеристиками (или устройство передатчика, для которого управление 330 временными характеристиками передает значение счетчика 332) включает в себя или имеет доступ к устройству сохранения (например, регистру - не показан), для сохранения подсчета генератора, для сравнения с новой величиной подсчета.

В одном варианте осуществления реплика сети 340 и распределительная сеть 320 интегрированы в одной интегральной схеме, а также представляют собой эквивалентные схемы. Таким образом, схемы могли бы быть согласованы при обработке, и, следовало бы ожидать, что они проявляют одинаковое поведение во время работы. Реплика сети 340 может дополнительно быть размещена в непосредственной близости на той же подложке, что и распределительная сеть 320, что могло бы дополнительно обеспечить то, что изменения температуры и горячие температурные точки не влияли бы одинаково на реплику сети 340 и распределительную сеть 320.

Регулировка задержки в передатчике и/или регулировка временных характеристик сигнала строба могут быть основаны на величине подсчета счетчика 332. В одном варианте осуществления управление 330 временными характеристиками выполняет расчеты для определения регулировки задержки. В одном варианте осуществления управление 330 временными характеристиками передает величину подсчета счетчика 332 в передатчик, который выполняет расчеты. Либо в запоминающем устройстве, или в контроллере, или в процессоре для расчетов может потребоваться очень большой объем ресурсов обработки. Вместо выполнения деления при расчетах, ресурсы вычислительной обработки могут использовать разложение в ряд Тейлора, для получения рабочей аппроксимации. Такой подход более подробно описан ниже со ссылкой на фиг. 4В. Использование разложения в ряд Тейлора и/или предварительных расчетов определенных значений может уменьшить требования к расчетам во время работы, благодаря уменьшению необходимости выполнения операций во время исполнения/операций, выполняемых в режиме реального времени, и/или других расчетов на основе аппаратных средств. Таким образом, общая нагрузка на вычисления, выполняемые аппаратными средствами, может быть уменьшена. Предварительный расчет может быть выполнен для любого значения, известного заранее для измерений величины подсчета генератора. Такие расчеты могут быть выполнены, используя встроенное программное обеспечение априори измерениям величины подсчета/временных характеристик генератора. Результаты предварительных расчетов могут быть сохранены в регистрах или другом накопителе для доступа при расчете регулировки задержки.

На фиг. 4А показана блок-схема варианта осуществления схемы несогласованного приемника. Схема 402 представляет собой схему несогласованного приемника, включающую в себя схему 410 выборки, несогласованный усилитель 430 и сеть 440 распределения тактовой частоты. Схема 410 выборки выполняет выборку принимаемого сигнала данных DQ [7:0] в соответствии с внутренним опорным напряжением Vref 420. Следует понимать, что сигналы данных могут составлять больше или меньше, чем 8 битов, в зависимости от конфигурации системы, часть которой составляет схема 402. Схема 410 выборки включает в себя элемент 412 для предоставления выборки входного сигнала, и элемент 414 для предоставления взаимодополняющей выборки входного сигнала для случая систем с двойной скоростью передачи данных, где оба края тактовой частоты используются для передачи данных. Таким образом, взаимодополняющий путь может не потребоваться в конфигурациях с одиночной скоростью передачи данных. Возможны другие конфигурации. Элементы 412 и 414 представляют собой усилители выборки, которые выполняют выборку фактически принимаемого сигнала и усиливают выборку. Таким образом, усиление может быть выполнено усилителем с меньшей скоростью по сравнению с усилением перед выборкой, как при использовании согласованной конфигурации.

Усилитель 430 принимает, как входной сигнал, поднимающего строба и сигнал опускающего строба. Сеть 440 распределения тактовой частоты распределяет строб или сигнал выборки для множества разных элементов, например, множества разных элементов выборки (не показаны). Точное количество уровней сети 440 распределения может изменяться в соответствии с вариантом осуществления. Следует понимать, что сеть распределения в виде двоичного дерева показана для простоты. Обычно используется Н-дерево (где каждый дополнительный уровень включает в себя четыре ветви вместо просто двух, и, следовательно, выглядит как "Н"). Независимо от того, какая конфигурация распределительной сети 440 используется, и, однако, используется множество уровней, существует путь строба или путь задержки от усилителя 430 к элементам 412 и 414 выборки.

Задержка на пути 450 строба изменяется с течением времени на основе операция устройства, в результате старения, изменения уровней напряжения, изменений температуры или, возможно, в результате других рабочих условий. Следует понимать, что временные характеристики на пути 450 строба не согласованы с задержкой для сигнала данных (которые могут быть выражены как tDQ≠tDQS). Разница по времени может быть компенсирована в результате изменения временных характеристик передаваемого сигнала или изменения, когда генерируется строб данных. Следует понимать, что линии передачи (дорожки или провода) вдоль разных уровней сети распределения тактовой частоты иллюстрируются, как имеющее сопротивление и емкость, как обычно представлено в данной области техники. Другие общие иллюстрации включают в себя представление индуктивности в каждой линии передачи, обозначающей, что задержка в каждой линии формируется комплексным импедансом из-за наличия сопротивления, емкости и индуктивности, свойственных данным линиям. Следует также понимать, что каждый треугольник представляет буфер, который предотвращает потерю сигнала, по мере его распространения через путь 450 строба.

На фиг. 4В показана блок-схема варианта осуществления схемы генератора с путем распределения реплики тактовой частоты для схемы несогласованного приемника по фиг. 4А. Реплика схемы 404 может быть интегрирована на той же подложке, что и схема 402, используя те же этапы обработки. В одном варианте осуществления реплика схемы 404 помещена в непосредственной физической близости к схеме 402 на подложке. Таким образом, поведение двух схем должно тесно соответствовать в отношении изменений задержки из-за условий окружающей среды. Реплика схемы 404 расположена параллельно схеме 402, и работает независимо от и в фоновом режиме относительно схемы 402. Будучи репликой, реплика сети 442 имеет ту же структуру, что и распределительная сеть 440. Таким образом, путь 452 реплики имеет такую же задержку, как путь 450 строба.

Как показано, реплика схемы 404 выполнена с возможностью или включает в себя кольцевой генератор. Кольцевой генератор генерирует колебания в течение периода из N циклов (где N представляет собой количество циклов, для которых разрешающий сигнал, поступающий в усилитель 432, является активным). Таким образом, N представляет собой количество циклов, для которых разрешены путь 452 реплики и реплика схемы 450. В одном варианте осуществления реплика схемы 404 не рассматривается, как включающая в себя счетчик 460, но, вместо этого, предоставляет вход в счетчик 460. В другом варианте осуществления счетчик 460 рассматривается, как часть реплики схемы 404. Счетчик 460 отслеживает количество колебаний за период циклов для пути 452 реплики. Таким образом, система, которой принадлежит схема 402 и 404, может рассчитывать задержку в распределительной сети, и, в частности, может идентифицировать вариации задержки. Задержка может быть рассчитана как или на основе 1 превышения значения подсчета, где величина подсчета представляет собой конечное значение подсчета, сохраненное в счетчике 460 после N циклов. Счетчик 460 может быть воплощен, например, 8-битным или 16-битным в большинстве случаев для достаточной точности.

Путь 452 реплики может называться "фиктивным путем" в отношении реального пути передачи данных или реального пути стробирования схемы 402. Реплика схемы 404 может непосредственно измерять задержку на пути tDQS, используя конфигурацию кольцевого генератора, без влияния на нормальную операцию приемника. В одном варианте осуществления реплика схемы 404 работает непрерывно или в режиме, близком в непрерывному, генерируя большое количество выборок для уменьшения шумов, все еще обеспечивая гораздо большую полосу пропускания, чем известные подходы периодической тренировки. Математически, частота кольцевого генератора может быть выражена, как функция системной тактовой частоты, где системная тактовая частота может быть выведена из множества потенциальных источников. Выражение может представлять собой: Уравнение 1: FRingOsc=FSystemClk*ROCount/N, где FRingOsc представляет частоту схемы кольцевого генератора, FSystemClk представляет частоту тактовой частоты системы, ROCount представляет конечную величину подсчета кольцевого генератора (записанную счетчиком 460), и N представляет количество циклов системной тактовой частоты, в течение которых кольцевой генератор включен или является активным.

Благодаря выбору большой величины N, становится возможным получить очень точное измерение задержки, и любые шумы в системе будут автоматически усреднены внутри кольцевого генератора с нулевыми дополнительными служебными издержками. Например, благодаря обеспечению возможности работы схемы 404 в течение 1 мс, где типичное значение tDQS составляет 0,5 нс, обеспечивается величина ROCount, приблизительно равная 2000. Любое дрожание тактовой частоты или простые шумы будут усреднены за 2000 колебаний, обеспечивая измерение для tDQS с точностью в пределах меньше, чем 1%.

Для расчета дрейфа задержки tDQS в течение времени, система может сохранять, по меньшей мере, одно значение для ROCount по предыдущим измерениям, и сравнивать новое значение ROCount относительно сохраненного значения. В одном варианте осуществления исходное значение для ROCount может быть сгенерировано в течение времени тренировки BIOS (основная система ввода-вывода), когда DQ центрируют вокруг DQS. Таким образом, одно измерение фактической системы может быть выполнено, и новое значение задержки может быть рассчитано на основе сохраненных результатов измерения, в отличие от итеративной сущности подхода периодической тренировки. В одном варианте осуществления дрейф может быть выражен математически, как в уравнении 2: ΔtDQS=N/FSystemClk*(1/ROCountNEW-1/ROCountOLD), где ΔtDQS представляет собой изменение задержки пути строба, N представляет собой количество циклов системной тактовой частоты, для которых обеспечивается возможность тестирования/измерений, FSystemClk представляет собой частоту системной тактовой частоты, ROCountNEW представляет собой значение текущих измерений ROCount и ROCountOLD представляет собой сохраненное значение ROCount.

Следует понимать, что математическое выражение для расчета дрейфа требует операции деления, которая представляет собой обоснованно объемную операцию, если воплощать в цифровых аппаратных средствах. Уравнение 2 может быть дополнительно оценено по разложению в ряд Тэйлора: Уравнение 3: ΔtDQS≈(N/FSystemClk)-(N/(FSystemClk/ROCountOLD))*ROCountNEW, и Уравнение 4: ΔtDQS≈(N/(FSystemClk/ROCountOLD2))*ROCountNEW2-(3*N/(FSystemClk/ROCountOLD))*ROCountNEW+(2*N/FSystemClk), где Уравнение 3 представляет собой разложение в ряд Тэйлора первого порядка. Уравнение 2 и Уравнение 4 представляют собой разложение в ряд Тэйлора второго порядка Уравнения 2. Следует отметить, что количество циклов, N, для измерения системной тактовой частоты, FSystemClk, и сохраненное значение величины подсчета кольцевого генератора, ROCountOLD, все представляют собой известные значения. Таким образом, каждая из требуемых операций деления для Уравнений 3 и 4 может быть выполнена не в режиме реального времени, сохранена, и доступ к ней может осуществляться для использования при умножении в режиме реального времени. Таким образом, Уравнение 3 и Уравнение 4 требуют только умножения в режиме реального времени с заранее рассчитанными операциями деления. Следует понимать, что более высокие порядки разложения в ряд Тэйлора и/или другие технологии оценки также можно использовать.

Схема 404 обеспечивает инверсию, необходимую для колебаний, путем соединения сигнала обратной связи с выхода реплики сети 442 с инвертирующим выводом усилителя 432, и подачей Vref на другой вывод. Другие варианты осуществления также позволяют достичь инверсии другими способами, и в других вариантах осуществления может использоваться дифференциальная обратная св