Усиление механизма перечисления и/или конфигурации одного протокола межсоединений для другого протокола межсоединений

Иллюстрации

Показать всеИзобретение относится к технологиям сетевой связи. Технический результат заключается в повышении безопасности передачи данных. Ведущее устройство LLI с архитектурой межсоединений, содержащее: процессор для формирования транзакции, не совместимой с LLI; логику преобразования, связанную с процессором и предназначенную для преобразования транзакции, не совместимой с LLI, в пакет LLI; и контроллер LLI, связанный с логикой преобразования, при этом контроллер LLI предназначен для связи устройства с архитектурой межсоединений с каналом связи LLI, и контроллер LLI предназначен для передачи символа, соответствующего пакету LLI, по каналу LLI, в котором транзакция выбирается из транзакции конфигурации PCI и транзакции конфигурации PCIE, и в котором логика преобразования должна преобразовать транзакцию конфигурации в пакет обслуживания LLI. 5 н. 17 з.п. ф-лы, 10 ил.

Реферат

Область техники, к которой относится изобретение

Описанные здесь варианты осуществления обычно относятся к межсоединениям. В частности, описанные здесь варианты осуществления обычно относятся к перечислению и/или конфигурации устройств, соединенных межсоединениями.

Краткое описание чертежей

Изобретение может быть наилучшим образом понято при обращении к последующему описанию и сопроводительным чертежам, используемым для пояснения вариантов осуществления изобретения. На чертежах:

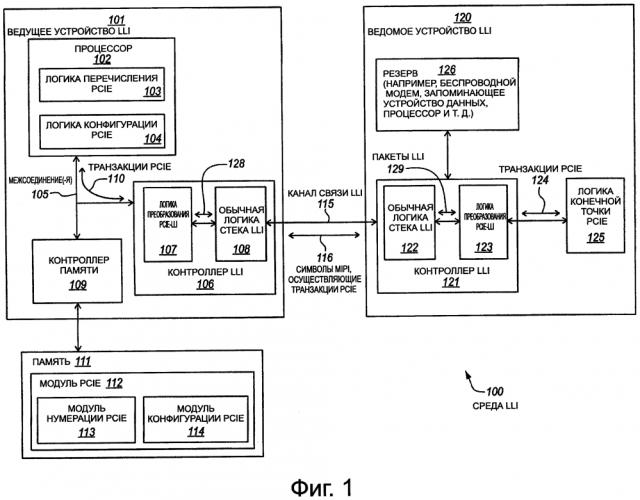

фиг. 1 - блок-схема варианта осуществления среды LLI, содержащей вариант осуществления ведущего устройства LLI, соединенного с вариантом осуществления ведомого устройства LLI посредством канала связи LLI;

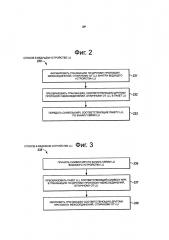

фиг. 2 - блок-схема последовательности выполнения операций варианта осуществления способа, который может выполняться ведущим устройством LLI;

фиг. 3 - блок-схема последовательности выполнения операций варианта осуществления способа, который может выполняться ведомым устройством LLI;

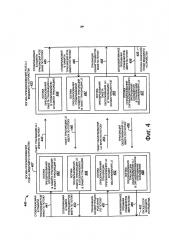

фиг. 4 - блок-схема примерных вариантов осуществления соответствующих преобразований PCIE-LLI;

фиг. 5 - блок-схема варианта осуществления интегрированной логики локализации корневого комплекса PCIE;

фиг. 6 - блок-схема варианта осуществления мобильного беспроводного устройства, в котором могут присутствовать варианты осуществления изобретения;

фиг. 7 - вариант осуществления архитектуры межсоединений, совместимой с PCIe, содержащей многоуровневый стек;

фиг. 8 - вариант осуществления различных протоколов, которые должны передаваться на различных физических уровнях архитектуры межсоединений;

фиг. 9 - вариант осуществления низковольтной компьютерной платформы;

фиг. 10 - вариант осуществления блок-схемы компьютерной системы.

Подробное описание вариантов осуществления

Здесь раскрыты способы, устройства и системы для усиления механизма перечисления и/или конфигурации одного протокола межсоединений для другого протокола межсоединений. В последующем описании изложены многочисленные конкретные подробности (например, конкретные протоколы межсоединений, типы транзакций, типы преобразований транзакций, логические реализации, подробности логического разделения/интеграции, последовательности операций, типы и взаимосвязи системных компонент и т.п.). Однако, следует понимать, что варианты осуществления изобретения могут быть осуществлены на практике без этих конкретных деталей. В других случаях, известные схемы, структуры и технологии не показаны подробно, чтобы не мешать пониманию настоящего описания.

Альянс Mobile Industry Processor Interface (MIPI®) Alliance (Альянс по мобильным промышленным процессорным интерфейсам) является организацией с открытым членством, имеющей цель определения и способствование открытым техническим требованиям для интерфейсов внутри мобильных терминалов. Рабочая группа MIPI по интерфейсам с низкой задержкам (LLI) создала технические требования Альянса MIPI® для интерфейса с низкой задержкой (LLI). Для простоты эта спецификация здесь будет также упоминаться как MIPI LLI или просто LLI.

LLI является интерфейсом с низкой задержкой, разработанным для соединения устройств (например, мобильного устройства или терминала) на уровне межсоединений (например, посредством открытого протокола ядра (Open Core Protocol, ОСР), усовершенствованной архитектуры шины микроконтроллера (Advanced Microcontroller Bus Architecture, AMBA®), и т.д.), используя отображаемые в памяти транзакции. Канал связи LLI является двунаправленным интерфейсом, который позволяет любому из устройств инициировать транзакции. LLI является межсоединением типа "точка-точка", которое позволяет осуществлять связь устройствам на отдельных микросхемах, как если бы устройство, расположенное на удаленной микросхеме, находилось на локальной микросхеме. Спецификация LLI выражается как многоуровневый протокол на уровне транзакций, в котором цели и инициаторы, находящиеся на микросхемах, соединенных LLI, способны обмениваться транзакциями, по существу, без вмешательства программного обеспечения, что помогает добиться низкой задержки. LLI также обычно демонстрирует низкое потребление энергии, которое имеет тенденцию делать LLI пригодным для сотовых телефонов, планшетов и других мобильных устройств с батарейным питанием. Единственным ограничением для LLI является то, что в настоящее время он не имеет достаточного механизма, чтобы перечислять и конфигурировать устройства, присоединенные к звеньям связи LLI.

На фиг. 1 представлена блок-схема варианта осуществления среды 100 LLI, которая содержит вариант осуществления ведущего устройства 101 LLI, связанного с вариантом осуществления ведомого устройства 120 LLI каналом 115 связи LLI. Термины "ведущее устройство" и "ведомое устройство" используются для совместимости с техническими требованиями к LLI. Ведущее устройство может также представлять собой хост-устройство или просто первое устройство, а ведомое устройство может также представлять собой ведомое устройство или просто второе устройство. Ведущее устройство LLI может быть выполнено с возможностью управления ведомым устройством LLI. В некоторых вариантах осуществления ведущее и ведомое устройства LLI могут быть различными микросхемами, матрицей, интегральными схемами или потенциально разными упаковками.

Примеры подходящих ведущих устройств LLI содержат, в частности, микросхемы прикладных процессоров и системы прикладных процессоров на микросхемах (SoCs). Примерами соответствующих ведомых устройств LLI являются, в частности, микросхемы сопроцессоров, микросхемы беспроводных модемов (например, микросхемы сотовых модемов, микросхемы модемов беспроводной локальной сети (WLAN) и т.д.) и микросхемы запоминающего устройства данных (например, микросхемы флэш-памяти), если назвать несколько примеров. Как показано, ведомое устройство LLI может быть беспроводным модемом, устройством хранения данных, сопроцессором или другим ресурсом 126, который используется ведущим устройством LLI. Компоненты ведущего и ведомого устройств LLI могут отображаться в памяти, чтобы облегчить адресацию устройства. Ведущее устройство LLI может быть выполнено с возможностью управления всей картой системной памяти.

Ведущее устройство LLI содержит процессор 102, контроллер 106 LLI и контроллер 109 памяти. Процессор, контроллер LLI и контроллер памяти все связываются вместе друг с другом или как-либо иначе при осуществлении связи друг с другом с помощью одной или более шин или других межсоединений 105. Контроллер памяти связывается или соединяется с памятью 111. Контроллер 106 LLI связывается или соединяется с одним концом канала 115 связи LLI. Контроллер LLI выполнен с возможностью связи ведущего устройства с каналом связи LLI. Ведомое устройство 120 LLI также содержит контроллер 121 LLI, который связывается или соединяется с другим концом канала 115 связи LLI.

В некоторых вариантах осуществления механизм перечисления и/или конфигурации первого протокола межсоединений может быть усилен или использоваться повторно для второго, другого протокола межсоединений. В одном из вариантов второй протокол межсоединений может не иметь присущего ему механизма конфигурации и/или перечисления. В другом варианте второй протокол межсоединений может иметь механизм перечисления и/или конфигурации, но он может быть не настолько хорошим, обширным, всесторонним, хорошо разработанным, хорошо протестированным, гибким или быстрым как механизм первого протокола межсоединений. В еще одном другом варианте второй протокол межсоединений может иметь механизм перечисления и/или конфигурации, но по какой-то другой причине может быть желательным использовать механизм перечисления и/или конфигурации первого протокола (например, потому что он имеет особенность, отсутствующую в другом протоколе, с ним хорошо знакомы или он предпочтителен и т.д.).

Как дополнительно будет описано ниже, в некоторых вариантах осуществления, механизм перечисления и/или конфигурации межсоединения периферийных компонент (Peripheral Component Interconnect, PCI), экспресс-межсоединения периферийных компонент (Peripheral Component Interconnect Express, PCIE) или расширенного межсоединения периферийных компонент (Peripheral Component Interconnect extended, PCI-X) может быть усилен и/или использован повторно для MIPI LLI, хотя объем изобретения этим не ограничивается. В других вариантах осуществления механизм перечисления и/или конфигурации по другому интернет-протоколу, помимо PCI, PCIE или PCI-X, может быть усилен или использоваться повторно для LLI как, например, будущая версия PCI, PCIE, или PCI-X, производная версия PCI, PCIE, или PCI-X, протокол, связанный с PCI, PCIE или PCI-X, протокол, подобный PCI, PCIE или PCI-X, замена PCI, PCIE или PCI-X или протокол, имеющий возможности перечисления и/или конфигурации, сравнимые с PCI, PCIE или PCI-X. Альтернативно, как вариант, могут использоваться другие протоколы с возможностями перечисления и/или конфигурации, такие, как, например, протоколы универсальной последовательной шины (Universal Serial Bus, USB), другие протоколы, производные от USB или связанные с USB, или другие разработанные в будущем протоколы. Термины "протокол на основе межсоединений периферийных компонент", "протокол на основе PCI" и т.п., как они используются здесь, в совокупности упоминаются как PCI, PCIE, PCI-X и другие протоколы на основе PCI или производные от PCI. В других дополнительных вариантах осуществления, механизм перечисления и/или конфигурации PCI, PCI-X, PCIE или какой-либо другой протокол межсоединений, может быть усилен или повторно использоваться для протокола межсоединений, отличного от LLI (например, будущая версия или производный протокол LLI или другой протокол межсоединений, имеющий ограниченные возможности перечисления и/или конфигурации). В других вариантах осуществления вместо LLI могут использоваться протокол Unified Protocol (Unipro), digRF, SuperSpeed Inter-Chip (SSIC), или другие. В приведенных здесь вариантах осуществления PCIE часто используется в качестве примерного протокола, хотя следует понимать, что PCIE может альтернативно быть заменен PCI или PCI-X или USB или другим соответствующим протоколом межсоединений, имеющим механизм перечисления и конфигурации. Кроме того, в описанных ниже вариантах осуществления LLI часто используется в качестве примерного протокола, хотя следует понимать, что LLI может альтернативно быть заменен будущей версией LLI, производным протоколом LLI, протоколом, связанным с LLI, протоколом, подобным LLI или другим протоколом межсоединений, который может получить выгоду от усиления и/или повторного использования возможностей перечисления и конфигурации другого, отличного от них протокола межсоединений.

Обращаясь снова к фиг. 1, память 111 имеет модуль 112 PCIE. Альтернативно, память может иметь модуль другого протокола межсоединений, который отличается от LLI (например, PCI, PCI-X, протокол на основе PCI, USB, и т.д.). В некоторых вариантах осуществления модуль PCIE может быть выполнен с возможностью управления связью через шину PCIE. Шина PCIE не показана и реально это может быть не шина PCIE, как будет объяснено далее. Например, модуль PCIE может содержать драйвер шины PCIE, стек программного обеспечения PCIE или подобные функциональные возможности. В некоторых вариантах осуществления модуль PCIE может содержать по существу стандартный драйвер шины PCIE, стек программного обеспечения PCIE, или по меньшей мере участок в них, достаточный для выполнения перечисления и/или конфигурации, как описано здесь. Различные большие операционные системы обычно содержат стандартные драйверы шины PCIE и/или стеки программного обеспечения PCIE, пригодные для вариантов осуществления.

Стандартные драйверы шины PCIE и/или стеки программного обеспечения PCIE обычно имеют механизм перечисления и конфигурации устройств, подключенных к шинам PCIE. Показанный модуль имеет модуль 113 перечисления PCIE, который полезен для перечисления PCIE, чтобы перечислить одно или более ведомых устройств LLI ведущему устройству LLI. Например, модуль перечисления PCIE может содержать команды, управляющую программу, подпрограммы или процедуры, которые позволяют процессору раскрывать или обнаруживать устройства, присоединенные к шинам PCIE, раскрывать или обнаруживать возможности устройств, присоединенных к шинам PCIE, раскрывать или обнаруживать ресурсы, которые будут использовать устройства, присоединенные к шинам PCIE (например, сколько памяти будут использовать устройства), типы и количества поддерживаемых прерывателей, тип и количество функций в каждом устройстве и т.п. Показанный модуль PCIE также имеет модуль 114 конфигурации PCIE, полезный для конфигурации PCIE. Например, модуль конфигурации PCIE может содержать команды, управляющую программу, подпрограммы или процедуры, которые позволяют процессору конфигурировать устройства, присоединенные к шинам PCIE, например, конфигурируя диапазоны адресов памяти, конфигурируя векторы прерывания, модифицируя регистры конфигурации PCIE и/или структуры возможностей и т.д. Хотя были показаны отдельные модули перечисления и конфигурации PCIE, другие варианты осуществления могут объединять эти модули в единый модуль. В других вариантах осуществления модуль перечисления PCIE может содержаться без модуля конфигурации PCIE или модуль конфигурации PCIE может содержаться без модуля перечисления PCIE.

В некоторых вариантах осуществления модули перечисления 113 PCIE и модули 114 конфигурации PCIE могут быть, по существу, стандартными и могут быть полезны, чтобы выполнять, по существу, стандартные перечисление и конфигурацию. В некоторых вариантах осуществления ведущее устройство 101 LL1 может усиливать или повторно использовать, по существу, стандартные модули перечисления PCIE и/или модули конфигурации PCIE, чтобы выполнять перечисление и/или конфигурацию ведомого устройства 120 LLI 120 по каналу 115 связи LLI. В некоторых вариантах осуществления это может помочь избежать необходимости разрабатывать новые механизмы перечисления и/или конфигурации специально для LLI, что может помочь избежать или, по меньшей мере, сократить время и затраты на разработку. Кроме того, модули перечисление и конфигурации PCIE имеют тенденцию быть хорошо разработанными, протестированными и понятыми. Кроме того, они уже широко доступны через несколько больших операционных систем. Кроме того, PCIE использует стандартизированное механизмы перечисления и конфигурации. Использование таких стандартизированных механизмов может помочь избежать разработки специализированных и/или собственных механизмов перечисления и/или механизмов конфигурации, которые могут иметь тенденцию снижать функциональную совместимость устройства.

Обращаясь опять к фиг. 1, процессор 102 может исполнять команды модуля 113 перечисления PCIE и/или модуля 114 конфигурации PCIE (например, как часть операционной системы, исполняемой на процессоре), которые могут конфигурировать процессор, чтобы иметь модуль/механизм/логику 103 перечисления PCIE и/или модуль/механизм/логику 104 конфигурации PCIE, соответственно. В некоторых вариантах осуществления это может заставить процессор формировать и обеспечивать транзакцию 110, основанную на PCIE или PCI. То есть, процессор может формировать и представлять транзакцию, имеющую протокол межсоединений, отличный от LLI. Модуль/механизм/логика перечисления PCIE и/или модуль/механизм/логика конфигурации PCIE могут обеспечить транзакции 110 на основе PCIE или PCI контроллеру 106 LLI ведущего устройства LLI через одно или более межсоединений 105.

Контроллер LLI содержит вариант осуществления логики 107 преобразования PCIE-LLI, который связан с процессором 102. В другом варианте осуществления логика 107 преобразования PCIE-LLI может быть отдельной от контроллера 106 LLI, но быть связанной с контроллером 106 LLI (например, связанной или логически расположенной между контроллером LLI и процессором). Логика 107 преобразования PCIE-LLI может принимать транзакции 110 PCIE. В некоторых вариантах осуществления логика 107 преобразования PCIE-LLI может быть выполнена с возможностью осуществления преобразований PCIE-LLI и преобразований LLI-PCIE. Альтернативно, логика преобразования PCI-LLI может содержаться для преобразования между PCI (или другим протоколом на основе PCI) и LLI или может содержаться другая логика для преобразования между LLI и другим протоколом межсоединений, помимо LLI. Логика 107 преобразования PCIE-LLI может быть выполнена с возможностью преобразования принятых транзакций 110 PCIE в соответствующие транзакции LLI, пакеты или форматы 128 данных, совместимые с LLI, которые реализуют или представляют транзакции ПО PCIE. В некоторых вариантах осуществления преобразование может содержать отображение разрядов или полей транзакций PCIE в соответствующие биты или поля пакетов LLI или совместимых с LLI форматов данных. Конкретные примеры того, как это может быть сделано, будут описаны здесь далее. Логика преобразования PCIE-LLI может затем обеспечить пакеты LLI или другие форматы 128 данных LLI, совместимые со связанной логикой 108 стеков LLI. В некоторых вариантах осуществления логика стеков LLI может, как вариант, представлять, по существу, стандартный стек LLI, который содержит уровень транзакции, уровень канала передачи данных, уровень адаптера PHY и один или более M-PHY. В некоторых вариантах осуществления логика преобразования PCIE-LLI может быть выполнена с возможностью обеспечения транзакций LLI, которые она формирует на уровне транзакций логики 108 стека LLI. Логика стека LLI может преобразовывать принятые пакеты LLI в соответствующие символы MIPI и затем M-PHY логики 108 стеков LLI и/или контроллер LLI 106 может передавать символы 116 MIPI полученные из пакетов 128 LLI), которые реализуют или представляют транзакции 110 PCIE, по линии 115 связи LLI. Соответственно, в некоторых вариантах осуществления транзакции PCIE, используемые для перечисления и/или конфигурации, могут быть переданы по линии связи LLI как символы MIPI, которые были получены из пакетов LLI.

Ведомое устройство 120 LLI содержит контроллер 121 LLI. Контроллер LLI соединяется с другим противоположным концом канала 115 связи LLI и выполнен с возможностью соединения ведомого устройства LLI с каналом связи LLI. Контроллер 121 LLI содержит логику 122 стека LLI. В некоторых вариантах осуществления логика 122 стека LLI может дополнительно представлять, по существу, стандартный стек LLI, который содержит уровень транзакций, уровень канала передачи данных, уровень адаптера PHY и один или более M-PHY. M-PHY логики 122 стека LLI могут принимать от канала 112 связи LLI символы MIPI (полученные из пакетов 128 LLI), которые осуществляют или представляют транзакции 110 PCIE. Логика 122 стека LLI может обрабатывать символы MIPI и формировать транзакции LLI, пакеты или другие форматы 129 данных, совместимые с LLI. Уровень транзакции логики 122 стека LLI может обеспечивать транзакции LLI или пакеты 129 для варианта осуществления логики 123 преобразования PCIE-LLI. Альтернативно, транзакции LLI или пакеты могут предоставляться для логики преобразования PCI-LLI или для логики, чтобы проводить преобразование между протоколом LLI и другим протоколом межсоединений помимо LLI, отличным от PCI и PCIE.

На чертеже логика 123 преобразования PCIE-LLI является частью контроллера 121 LL1. В другом варианте осуществления логика 123 преобразования PCIE-LLI может быть отдельной от контроллера 121 LLI 121, но связанной с контроллером 121 LLI 121 (например, связанной или логически расположенной между контроллером LLI и вариантом осуществления логики 125 конечной точки PCIE). Логика 123 преобразования PCIE-LLI 123 выполнена с возможностью осуществления преобразований PCIE-LLI и преобразований LLI-PCIE. Альтернативно, другие преобразования на основе PCI или другие преобразования могут быть выполнены как описано здесь в другом месте. Логика преобразования PCIE-LLI может преобразовывать принятые транзакции LLI или пакеты 129, которые реализуют или представляют транзакции PCIE 110, в соответствующие транзакции 124 PCIE. В некоторых вариантах осуществления преобразование может содержать отображение разрядов или полей пакетов LLI, чтобы приспособить соответствующие разряды или поля транзакций PCIE. Конкретные примеры таких преобразований будут дополнительно обсуждены ниже.

Логика 123 преобразования PCIE-LLI связана с вариантом осуществления логики 125 конечной точки PCIE 125. Альтернативно, вместо логика конечной точки PCIE может использоваться логика конечной точки PCI или может использоваться логика конечной точки другого протокола межсоединений, помимо LLI, PCI, и PCIE. Логика 123 преобразования PCIE-LLI может обеспечить транзакции 124 PCIE, она формирует логику 125 конечной точки PCIE. В некоторых вариантах осуществления транзакции 124 PCIE 124, обеспечиваемые для логики конечной точки PCIE, могут быть идентичными или, по меньшей мере, по существу, идентичными транзакциям 110 PCIE, первоначально обеспечиваемым от процессора 101 (например, биты в полях пакета транзакции 124 PCIE могут быть идентичны битам в полях пакета транзакции 110 PCIE). В некоторых вариантах осуществления логики конечной точки PCIE может иметь настолько большую логику PCIE, какой она может быть у нормального устройство PCIE, соединенного с шиной PCIE. Альтернативно, логика конечной точки PCIE может иметь, по меньшей мере, так много логики PCIE, сколько необходимо для поддержания желаемых перечисления и/или конфигурации, требующихся для конкретного варианта осуществления. Для примера, в некоторых вариантах осуществления логика конечной точки PCIE может содержать регистры конфигурации, совместимые с PCIE, (или другие, основанные на PCI) (например, индексные регистры PCIE и т.д.), и структуры возможностей, которые могут быть выполнены с возможностью использования описанных здесь вариантов осуществления. В качестве другого примера, в некоторых вариантах осуществления логика конечной точки PCIE может содержать логику обслуживания/реализации отображаемых в памяти транзакций и/или логику обслуживания/реализации транзакций конфигурации PCIE. В некоторых вариантах осуществления, логика конечной точки PCIE может быть введена в ведомое устройство LLI даже при том, что ведомому устройству LLI не обязательно иметь шины PCIE и/или логика конечной точки PCIE не обязательно должна быть связана с шиной PCIE.

В некоторых вариантах осуществления логика конечной точки PCIE может представить интегрированную логику конечной точки корневого комплекса PCIE. В PCIE ведущее устройство также иногда упоминается как интегрированное устройство корневого комплекса. Удаленное устройство иногда упоминается как конечная точка или конечная точка корневого комплекса. Исторически, в PCI ведущее устройство и удаленное устройство были разными микросхемами, установленными на печатной плате. PCIE также позволяет устройству конечной точки интегрироваться на микросхему или на матрицу с устройством корневого комплекса вместо того, чтобы находиться на отдельной удаленной микросхеме. Такое интегрированное устройство также иногда упоминается в технике как интегрированное устройство конечной точки корневого комплекса. Устройство корневого комплекса и интегрированное устройство конечной точки корневого комплекса интегрируются вместе на микросхеме или на матрице. В случае интегрированной логики конечной точки корневого комплекса PCIE процессор ведущего устройства может даже не знать или не быть осведомленным о вступлении в процесс канала связи LLI, а скорее может осуществлять связь с интегрированным устройством конечной точки корневого комплекса, как если бы оно был интегрирован процессором на микросхему или на матрицу.

В некоторых вариантах осуществления транзакции 110 PCIE и/или транзакции 124 PCIE могут использоваться для перечисления и/или конфигурации ведомого устройства 120 LLI. В случае конфигурации, транзакции 124 PCIE могут быть выполнены с возможностью модификации регистров конфигурации и/или структур возможностей на основе PCIE (или других на основе PCI) ведомого устройства. В некоторых вариантах осуществления, например, в случае некоторого перечисления, транзакции 124 PCIE могут вызывать или приводить в результате к логике конечной точки PCIE, формирующей ответные транзакции 124 PCIE 124 в обратном направлении, которые должны передаваться ведущему устройству LLI. Эти транзакции 124 PCIE могут предоставляться контроллеру 121 LLI ведомым устройством, передаваться логикой стека LLI как символы MIPI по каналу связи 115 связи LLI, приниматься как символы MIPI стеком LLI контроллера 106 LLI ведущего устройства, эффективно переходить на обратное направление к описанному ранее. Логика 123 преобразования PCIE-LLI ведомого устройства может преобразовать пакеты PCIE или транзакции 124 в соответствующие пакеты LLI. Символы 116 MIPI, которые осуществляют или представляют транзакции 124 PCIE, могут передаваться по каналу связи LLL Логика 107 преобразования PCIE-LLI ведущего устройства может преобразовывать пакеты LLI, восстановленные из этих символов MIPI, полученных через канал связи LLI, в соответствующие транзакции 110 PCIE 110. Эти транзакции 110 PCIE могут быть идентичными или, по меньшей мере, по существу, идентичными (например, функционально эквивалентными) первоначально посланным транзакциям 124 PCIE.

На фиг. 2 представлена блок-схема последовательности выполнения операций варианта осуществления способа 230, который может выполняться ведущим устройством LLI. В некоторых вариантах осуществления операции и/или способ, показанные на фиг. 2, могут выполняться ведущим устройством 101 LL1 или внутри ведущего устройства 101 LL1, показанного на фиг. 1. Компоненты, признаки и конкретные необязательные детали, описанные здесь для ведущего устройства 101 LL1, также необязательно применяются к операциям и/или способу 230, которые могут выполняться в вариантах осуществления и/или в рамках ведущего устройства 101 LLI. Альтернативно, операции и/или способ, показанные на фиг. 2, могут выполняться аналогичным и/или полностью другим ведущим устройством LLI, чем то, которое показано на фиг. 1. Кроме того, ведущее устройство LLI, показанное на фиг. 1, может выполнять операции и/или способы точно также, подобно или полностью иначе, чем на фиг. 2.

Способ содержит формирование в блоке 231 транзакции, выполненной по протоколу, отличному от LLI, внутри ведущего устройства LLI. В некоторых вариантах осуществления транзакций может выполняться по протоколу PCI, протоколу PCIE, другому протоколу на основе PCI или другому протоколу, отличному от LLI. В некоторых вариантах осуществления транзакция может быть частью по меньшей мере перечисления ведомого устройства LLI, связанного с каналом связи LLI, или и конфигурации ведомого устройства LLI, связанного с каналом связи LLI.

Способ содержит преобразование в блоке 232 транзакции, которая выполнена по протоколу межсоединений, отличному от LLI, в пакет LLI или транзакцию. В некоторых вариантах осуществления пакет LLI может осуществлять или представлять сформированную транзакцию на основе PCI. В некоторых вариантах осуществления преобразование может содержать отображение битов или полей сформированной транзакции на основе PCI, в соответствующие биты или поля пакета LLI. В некоторых вариантах осуществления пакет LLI может обеспечиваться для уровня транзакций необязательно стандартного стека LLI.

Способ также содержит передачу в блоке 233 символов MIPI, полученных из пакета LLI через канал связи LLI. В некоторых вариантах осуществления символы MIPI могут осуществляться или представляться и могут использоваться, чтобы передавать первоначально сформированную транзакцию на основе PCI или другую транзакцию, выполненную по протоколу межсоединений, отличному от LLI.

На фиг. 3 представлена блок-схема последовательности выполнения операций варианта осуществления способа 335, который может выполняться ведомым устройством LLI. В некоторых вариантах осуществления операции и/или способ, показанные на фиг. 3, могут выполняться ведомым устройством 120 LLI, показанным на фиг. 1, или внутри него. Компоненты, признаки и конкретные необязательные подробности, описанные здесь для ведомого устройства 120 LL1 также необязательно применяются к операциям и/или к способу 335, который в вариантах осуществления может выполняться ведомым устройством 120 LLI или внутри него. Альтернативно, операции и/или способ, показанные на фиг. 3, могут быть выполнены подобным или полностью другим ведомым устройством LLI, чем то, которое показано на фиг. 1, или внутри него. Кроме того, ведомое устройство LLI, показанное на фиг. 1, может выполнить операции и/или способы, такие же, подобные, или полностью отличающиеся от тех, которые показаны на фиг. 2.

Способ содержит прием в блоке 336 символа MIPI, который был получен из пакета LLI, по каналу связи LLI ведомого устройства LLI. В некоторых вариантах осуществления принятый символ MIPI может осуществлять или представлять и может использоваться для передачи транзакции, выполненной по протоколу на основе PCI или другому протоколу межсоединений, отличному от LLI.

Способ содержит в блоке 337 преобразование пакета LLI, который соответствует и/или получен из принятого символа MIPI, в транзакцию, которая имеет другой протокол межсоединений, отличный от LLI. В некоторых вариантах осуществления пакет LLI может быть преобразован в транзакцию по протоколу PCI, по протоколу PCIE или другому протоколу, отличному от LLI. В некоторых вариантах осуществления преобразование может содержать отображение битов или полей пакета LLI в соответствующие биты или поля транзакции.

Способ содержит в блоке 338 обслуживание транзакции, которая выполнена по протоколу межсоединений, отличному от LLI. В некоторых вариантах осуществления транзакция может обслуживаться логикой конечной точки PCI или логикой конечной точки PCIE. В некоторых вариантах осуществления, обслуживание транзакции может выполняться в сочетании по меньшей мере с конфигурированием ведомого устройства LLI или перечислением ведомого устройства LLI ведущему устройству LLI.

На фиг. 2-3 показаны способы, в которых ведущее устройство формирует транзакции и передает символы, представляющие эти транзакции, ведомому устройству. Альтернативно, как упоминалось ранее, рассматриваются также аналоговые обратные способы, в которых ведомое устройство формирует транзакции и передает символы, представляющие эти транзакции, ведущему устройству. В некоторых вариантах осуществления это может делаться, по существу, как описано выше для фиг. 1.

На фиг. 4 представлена блок-схема примерных вариантов осуществления примера соответствующих преобразований 440 PCIE-LLI. Показаны вариант осуществления логики 407 преобразования PCIE-LLI ведущего устройства и вариант осуществления логики 423 преобразования PCIE-LLI ведомого устройства. В некоторых вариантах осуществления логика 407 преобразования PCIE-LLI ведущего устройства и/или логика 423 преобразования PCIE-LLI ведомого устройства, показанные на фиг. 4, соответственно, могут быть введены в ведущее устройство 101 LLI и/или в ведомое устройство 120 LLI, показанные на фиг. 1. Альтернативно, логика 407 преобразования PCIE-LLI ведущего устройства и/или логика 423 преобразования PCIE-LLI ведомого устройства 423, показанных на фиг. 4, соответственно, может быть введена в подобные или разные ведущие и ведомые устройства LLI, отличные от показанных на фиг. 1. Кроме того, ведущее устройство 101 LLI и/или ведомое устройство 120, показанные на фиг. 1, могут быть подобны или отличаться от другой логики преобразования PCIE-LLI, показанной на фиг. 4.

Процессор 402 ведущего устройства может передавать отображаемую в памяти транзакцию 441 в нисходящем потоке дальше в транзакцию, отображаемую в памяти, логике 442 преобразования пакета транзакций LLI логики преобразования PCIE-LLI ведущего устройства. Термин "в нисходящем потоке" используется здесь как относящийся к направлению от ведущего устройства к ведомому устройству. Напротив, термин "в восходящем потоке" используется здесь как относящийся к направлению от ведомого устройства к ведущему устройству. Логика 442 преобразования может быть выполнена с возможностью преобразования отображаемой в памяти транзакции 441 нисходящего потока в соответствующий пакет 443 транзакции LLI нисходящего потока. Пакет 443 транзакции LLI нисходящего потока может передаваться логике 423 преобразования PCIE-LLI ведомого устройства.

Пакет транзакции LLI в логике 444 преобразования отображаемой в памяти транзакции логики преобразования PCIE-LLI ведомого устройства может принимать в нисходящем потоке пакет 443 транзакции LLI. Логика 444 преобразования может быть выполнена с возможностью преобразования пакета 443 транзакции LLI нисходящего потока в соответствующую отображаемую в памяти транзакцию 445 в нисходящем потоке. Отображаемая в памяти транзакция 445 нисходящего потока может передаваться логике 425 конечной точки PCIE ведомого устройства.

Логика 425 конечной точки PCIE ведомого устройства может передавать отображаемую в памяти транзакцию 446 в восходящем потоке в направлении отображаемой в памяти транзакции в логику 447 преобразования пакета транзакции LLI логики преобразования PCIE-LLI ведомого устройства. Логика преобразования 447 может быть выполнена с возможностью преобразования отображаемой в памяти транзакции 446 в восходящем потоке в соответствующий пакет 448 транзакции LLI 448в восходящем потоке. Пакет 448 транзакции LLI в восходящем потоке может быть передан в направлении логики преобразования PCIE-LLI ведущего устройства.

Логика 449 преобразования пакета транзакции LLI в отображаемую в памяти транзакцию логики преобразования PCIE-LLI ведущего устройства может принимать пакет 448 транзакции LLI в восходящем потоке. Логика 449 преобразования может быть выполнена с возможностью преобразования пакета 448 транзакции LLI в восходящем потоке в соответствующую отображаемую в памяти транзакцию 450 в восходящем потоке. Отображаемая в памяти транзакция 450 в восходящем потоке может быть передана процессору 402 ведущего устройства.

Процессор 402 ведущего устройства может передавать в нисходящем потоке транзакцию 451 конфигурации PCIE в направлении транзакции конфигурации PCIE в логику 452 преобразования пакета обслуживания LLI логики преобразования PCIE-LLI ведущего устройства. LLI в настоящий момент не поддерживает транзакции конфигурации. В некоторых вариантах осуществления транзакции конфигурации PCIE могут отображаться в пакеты обслуживания LLI, которые могут передаваться по каналу связи LLI. Логика 452 преобразования может быть выполнена с возможностью преобразования транзакции 451 конфигурации PCIE в нисходящем потоке в соответствующий пакет 453 обслуживания LLI в нисходящем потоке. Пакет 453 обслуживания LLI в нисходящем потоке может быть передан в направлении логики преобразования PCIE-LLI ведомого устройства.

Логика 454 преобразования пакета обслуживания LLI в транзакцию конфигурации PCIE логики преобразования PCIE-LLI ведомого устройства может принять пакет 453 обслуживания LLI в нисходящем потоке. Логика 454 преобразования может быть выполнена с возможностью преобразования пакета 453 обслуживания LLI в нисходящем потоке в соответствующую транзакцию 455 конфигурации PCIE в нисходящем потоке. Транзакция 455 конфигурации PCIE в нисходящем потоке может быть передана в направлении логики 425 конечной точки PCIE ведомого устройства.

Логика 425 конечной точки PCIE ведомого устройства может передавать сообщенное прерывание 456 сообщения в восходящем потоке в направлении сообщенного прерывания сообщения логике 457 преобразования транзакции обслуживания LLI логики преобразования PCIE-LLI ведомого устройства. Логика 457 преобразования может быть выполнена с возможностью преобразования сообщенного прерывания 456 сообщения в восходящем потоке в соответствующий пакет 458 обслуживания LLI в восходящем потоке. Пакет 458 обслуживания LLI в восходящем потоке может быть передан в направлении логики преобразования PCIE-LLI ведущего устройства.

Транзакция обслуживания LLI в логику 459 преобразования сообщенного прерывания сообщения логики преобразования PCIE-LLI ведущего устройства может принять транзакцию 458 обслуживания LLI в восходящем потоке. Логика 459 преобразования может быть выполнена с возможностью преобразования транзакции 458 обслуживания LLI в восходящем потоке в соответствующее сообщенное прерывание 460 сообщения в восходящем потоке. Сообщенное прерывание 460 сообщения в восходящем потоке может быть передано в направлении процессора 402 ведущего устройства.

Чтобы дополнительно проиллюстрировать, как транзакции PCIE могут быть преобразованы в пакеты уровня транзакции LLI, может быть полезным рассмотреть несколько иллюстративных примеров. Отображаемые в памяти считывания и другие отображаемые в памяти транзакции могут не иметь полезной загрузки данных. В таких случаях большинство полей пакета LLI (например, 73-разрядного пакета запроса команды LLI) может быть заполнен