Устройство для поиска минимального значения интенсивности размещения в полносвязных матричных системах при двунаправленной передаче информации

Иллюстрации

Показать всеИзобретение относится к области моделирования комбинаторных задач при проектировании вычислительных систем (ВС). Технической результат заключается в расширении области применения устройства за счет введения средств для поиска минимального значения интенсивности размещения в полносвязных матричных системах при двунаправленной передаче информации по критерию минимизации интенсивности процессов и данных. Устройство содержит блок минимального значения, содержащий счетчик столбцов, счетчик номера слоя, дешифратор номера, дешифратор номера столбца, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой регистр инцидентной дуги, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой SR-триггер, промежуточный блок сумматоров, итоговый блок сумматоров, элемент И объединения, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элемент И. 1 з.п. ф-лы, 9 ил.

Реферат

Изобретение относится к области цифровой вычислительной техники и предназначено для моделирования комбинаторных задач при проектировании вычислительных систем (ВС).

Известен элемент однородной среды, включающий блок обработки входных сигналов, блок запоминания признака конечной точки, блок выходной логики, триггер записи трасс, блок оценки текущего размещения, блок передачи информации, входы, выходы, управляющий вход, информационные входы, информационные выходы, индикаторный выход (АС 1291957 СССР кл. G06F 7/00, опубл. 23.02.87, БИ №7).

Недостатком указанного элемента является узкая область применения, обусловленная ограниченным числом критериев оценки степени оптимальности размещения.

Наиболее близкой к предлагаемому устройству по технической сущности является устройство для формирования субоптимального размещения и его оценки, содержащая блок формирования перестановок, блок постоянной памяти, коммутатор, арифметико-логическое устройство (АЛУ), блок запоминания лучшего варианта, введены дешифратор выбора дуги, реверсивный счетчик ячеек, блок оперативной памяти, счетчик топологии, первый и второй счетчики расстояний, умножитель, сумматор, регистр минимальной длины связей, первый элемент сравнения, вычитатель, триггер начала счета, триггер режима, триггер задания топологии, регистр длины связей, второй элемент сравнения, счетчик дуг, дешифратор блокировки дуги, регистр номера дуги, регистр минимального веса, группа элементов И, первый и второй элементы И, второй блок элементов ИЛИ, третий элемент И, первый и второй одновибраторы, первый, второй и третий элементы задержки, два регистра сдвига, элемент ИЛИ и группу элементов ИЛИ, электронную модель графа (ЭМГ) содержащую m электронных моделей дуги, причем l-я электронная модель дуги (l = 1, 2, …, m) содержит триггер блокировки дуги, регистр веса дуги, регистр блокировки дуги, первый элемент И, второй элемент И, элемент ИЛИ (Патент РФ №2193796, кл. G06F 17/10, 7/38, опубл. 27.11.2002, БИ №33).

Недостатком указанного устройства является узкая область применения, обусловленная отсутствием средств для поиска минимального значения интенсивности размещения в полносвязных матричных системах (МС) при двунаправленной передаче информации.

Технической задачей изобретения является расширение области применения устройства за счет введения средств для поиска минимального значения интенсивности размещения в полносвязных МС при двунаправленной передаче информации по критерию минимизации интенсивности процессов и данных.

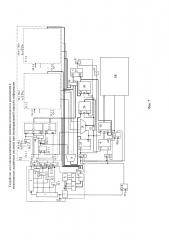

Техническая задача решается тем, что в устройство для поиска минимального значения интенсивности размещения в полносвязных матричных системах при двунаправленной передаче информации, содержащее матрицу из m строк и n столбцов элементов однородной среды, n блоков подсчета единиц, блок нахождения максимума, сумматор, блок памяти, причем входы управления перестановкой столбцов матрицы элементов однородной среды соединены с входом управления перестановкой столбцов устройства, входы управления перестановкой строк матрицы элементов однородной среды соединены с входом управления перестановкой строк устройства, входы установки матрицы элементов однородной среды соединены с входом установки устройства, информационные входы матрицы элементов однородной среды соединены с входом записи устройства, индикаторные выходы элементов j-го столбца (j = 1,2, …, n) матрицы элементов однородной среды соединены с входом j-го блока подсчета единиц, выход которого соединен с j-м входом блока нахождения максимума и j-м входом сумматора, выходы которых соединены с выходом максимальной длины ребра устройства и выходом суммарной длины ребер устройства соответственно, вход управления записью блока памяти соединен с входом управления записью устройства, информационные выходы элементов i-й строки (i = 1,2, …, m) матрицы элементов однородной среды соединены с i-м информационным входом блока памяти, выход которого соединен с информационным выходом устройства, дополнительно введен дополнительно введенный блок минимального значения, содержащий счетчик столбцов, счетчик номера слоя, дешифратор номера слоя, дешифратор номера столбца, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой регистр инцидентной дуги, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой SR-триггер, промежуточный блок сумматоров, итоговый блок сумматоров, элемент И объединения, первый, второй, третий, четвертый, пятый, шестой, седьмой и восьмой элемент И, отличающийся тем, что тактовый вход устройства соединен со счетным входом счетчика столбцов, выход которого подключен ко входу дешифратора номера столбца, выход переполнения счетчика столбцов подсоединен к счетному входу счетчика номера слоя, выход которого соединен с входом дешифратора номера слоя, выход переполнения счетчика номера слоя подключен к выходу переполнения, выходы с первого по m-й дешифратора номера слоя подсоединены к соответствующим вторым входам из i.j ( ) элементов объединения, выходы с первого по n-й дешифратора номера столбца соединены с соответствующими первыми входами из i.j ( ) элементов объединения, выход которого подключен к соответствующим вторым входам элементов первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого элементов И соответственно, выходы которых соединены с соответствующими s-входами первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого регистров инцидентной дуги, обратные е-входы которых подключены к соответствующим обратным выходам первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого SR-триггеров, а также к соответствующим первым входам первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого элемента И, D-входы первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого регистра инцидентной дуги соединены с соответствующим выходом блока оперативной памяти, выход первого, второго, третьего, четвертого, пятого, шестого, седьмого и восьмого регистров инцидентной дуги подключены к соответствующим входам промежуточного сумматора, выход которого подсоединен к соответствующим входам итогового блока сумматоров, выход которого соединен с выходом суммы устройства, R-вход восьмого SR-триггера подключен к ое-выходу восьмого регистра инцидентной дуги, ое–выходы первого, второго, третьего, четвертого, пятого, шестого и седьмого регистра инцидентной дуги соединены с соответствующими R-входами первого, второго, третьего, четвертого, пятого, шестого и седьмого SR-триггеров, прямой выход первого SR-триггера подсоединен к выходу единицы устройства, прямые выходы второго, третьего, четвертого, пятого, шестого, седьмого и восьмого SR-триггеров соединены с соответствующими выходами устройства.

Электронная модель графа содержит m электронных моделей дуги, причем l-я электронная модель дуги (l = 1, 2, …, m) содержит триггер блокировки дуги, регистр веса дуги, регистр блокировки дуги, первый элемент И, второй элемент И, элемент ИЛИ, причем входы первого элемента И соединены с соответствующими входами задания графа устройства, выход первого элемента И соединен с синхровходом регистра веса дуги и с установочным входом триггера блокировки дуги, вход сброса которого соединен с l-м входом блокировки дуги электронной модели графа, вход данных регистра веса дуги соединен с l-м входом веса дуги устройства, первый вход элемента ИЛИ соединен с l-м управляющим входом электронной модели графа, а второй вход элемента ИЛИ соединен с выходом второго элемента И, первый вход которого соединен с прямым выходом триггера блокировки дуги и с разрешающим входом регистра блокировки дуги, второй вход второго элемента И соединен с l-м входом выбора дуги электронной модели графа, вход сброса регистра блокировки дуги соединен с l-м входом сброса устройства, выход регистра блокировки дуги соединен с l-м выходом веса дуги электронной модели графа, который также соединен с выходом регистра веса дуги, выход элемента ИЛИ подключен к разрешающему входу регистра веса дуги.

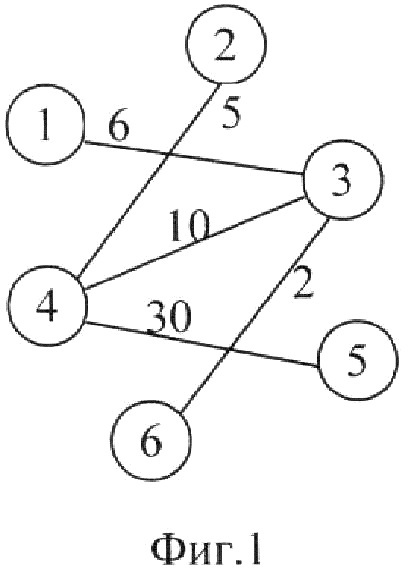

Сущность изобретения поясняется чертежами, где на фиг. 1 показан пример исходного графа задачи; фиг. 2 показывает пример описания матрицы смежности для исходного графа задачи, показанного на фиг. 1; на фиг. 2 показана матрица смежности W, соответствующая графу, представленному на фиг.1; на фиг. 3 представлена матрица расстояний для ТС, состоящей из шести процессоров; фиг. 4 показывает топологическую организацию полносвязной тороидальной системы в трех видах: общий вид (фиг. 4а), вид сверху (фиг. 4б) и вид сбоку (фиг. 4в); фиг 5 и 6 показывает пример гипотетического варианта размещения; фиг.7,8,9 представляет устройство для поиска минимального значения интенсивности размещения в полносвязных тороидальных системах при двунаправленной передаче информации.

Общие особенности изобретения состоят в следующем.

Предлагаемое устройство может использоваться в области проектирования вычислительных систем (ВC), например, при размещении процессов (алгоритмов, задач, данных, файлов и т.п.). Устройство дополнительно позволяет осуществлять поиск минимального значения интенсивности размещения в полносвязных ТС при двунаправленном передаче информации.

Исходная задача (процесс, алгоритм, программа) представляется в виде направленного взвешенного графа G=<Х,E> (фиг. 1), вершины которого соответствуют подзадачам (подалгоритмам, подпрограммам и т.п.), а дуги задают управляющие и/или информационные связи между подзадачами и фактически являются каналами передачи данных. Граф G может быть описан матрицей смежности , где ; – объем передаваемых данных между i-м и j-м процессорным модулем (фиг. 2).

Топологическая модель ТС (область размещения) задается матрицей расстояний D. Элементы матрицы расстояний D = ||di,j||n×n для полносвязной тороидальной системы образуются по формуле Минимальное значение интенсивности размещения для графа G вычисляется по формуле:

| , | (1) |

где , – векторы, содержащие ненулевые элементы матрицы W и D, расположенные по убыванию и возрастанию соответственно; k – порядковый номер элемента; m= - мощность множества дуг E.

Для удобства дальнейшего описания будем считать, что однородная среда содержит m×n элементов, при этом m=n (где m и n – число процессов). Функционирование однородной среды аналогично прототипу. При поступлении сигнала от внешнего устройства управления (ВУУ) происходит перестановка двух вершин графа и получение нового варианта размещения. Предлагаемое устройство вычисляет значения критериев оценки и выдает указанные значения ВУУ. Последнее анализирует принятые значения и либо фиксирует полученное размещение как более оптимальное, если значения критериев улучшают ранее найденные значения, либо игнорирует его.

Предлагаемое устройство дополнительно реализует поиск минимального значения интенсивности в полносвязных тороидальных системах при двунаправленной передаче информации по критерию минимизации интенсивности взаимодействия процессов и данных.

Сущность предлагаемого критерия поясняется фиг. 1-6. На фиг. 1 представлен гипотетический направленный граф задачи (программы, алгоритма, процесса), а на фиг. 2 – соответствующая ему матрица смежности. На фиг. 3 показан пример матрицы расстояний для МС, состоящей из 6 процессоров. На фиг. 4 показан пример полносвязной матричной системы с двунаправленной организацией межпроцессорных связей.

При поиске минимального значения интенсивности размещения предполагается, что наиболее интенсивно взаимодействующие участки исходной задачи (веса дуг с наибольшим объемом передаваемых данных) назначаются на смежные процессорные модули без учета топологии исходного графa G. Таким образом, реальное значение интенсивности размещения должно быть как можно ближе к ранее найденному минимальному значению.

На фиг. 5 представлен вариант размещения для графа G, представленного на фиг. 1. Данный вариант размещения не является минимальным значением, так как все вершины слоя МС имеют разные значения интенсивности, либо не обладают ими вовсе. Используя (1) получаем количественное значение минимального значения интенсивности:

;

;

.

В примере для вектора приведены только начальные значения, влияющие на коэффициент

Таким образом, при поиске минимального значения интенсивности размещения веса дуг графа G назначаются в порядке убывания соответствующих значений. На фиг. 6 представлен вариант размещения одновременно являющийся минимальным значением интенсивности размещения. При «реальном» размещении (процессов, данных и т.д.), значение интенсивности размещения приближается к минимальному значению. Таким образом можно оценить его качество.

Устройство для поиска минимального значения интенсивности размещения в полносвязных матричных системах при двунаправленной передаче информации содержит матрицу 1 из m строк и n столбцов элементов однородной среды, блоки 2.1, 2.2,…, 2.n подсчета единиц, блок 3 нахождения максимума, сумматор 4, блок 5 памяти, причем входы управления перестановкой столбцов матрицы 1 элементов однородной среды соединены с входом 7 управления перестановкой столбцов устройства, входы управления перестановкой строк матрицы 1 элементов однородной среды соединены с входом 8 управления перестановкой строк устройства, входы установки матрицы 1 элементов однородной среды соединены с входом 13 установки устройства, информационные входы матрицы 1 элементов однородной среды соединены с входом 6 записи устройства, индикаторные выходы элементов j-го столбца (j = 1,2, …, n) матрицы 1 элементов однородной среды соединены с входом блока 2.j подсчета единиц, выход которого соединен с j-м входом блока 3 нахождения максимума и j-м входом сумматора 4, выходы которых соединены с выходом 10 максимальной длины ребра устройства и выходом 11 суммарной длины ребер устройства соответственно, вход управления записью блока 5 памяти соединен с входом 9 управления записью устройства, информационные выходы элементов i-й строки (i = 1,2, …, m) матрицы 1 элементов однородной среды соединены с i-м информационным входом блока 5 памяти, выход которого соединен с информационным выходом 12 устройства, а также дополнительно введенный блок 58 минимального значения, содержащий счетчик 59 столбцов, счетчик 60 номера слоя, дешифратор 61 номера, дешифратор 62 номера столбца, первый 63.1.1, второй 64.1.1, третий 65.1.1, четвертый 66.1.1, пятый 67.1.1, шестой 68.1.1, седьмой 69.1.1 и восьмой 70.1.1 регистр инцидентной дуги, первый 71.1.1, второй 72.1.1, третий 73.1.1, четвертый 74.1.1, пятый 75.1.1, шестой 76.1.1, седьмой 77.1.1 и восьмой 78.1.1 SR-триггер, промежуточный 79 блок сумматоров, итоговый 80 блок сумматоров, элемент 81.1.1 И объединения, первый 82.1.1, второй 83.1.1, третий 84.1.1, четвертый 85.1.1, пятый 86.1.1, шестой 87.1.1, седьмой 88.1.1 и восьмой 89.1.1 элемент И, отличающийся тем, что тактовый 57 вход устройства соединен со счетным входом счетчика 59 столбцов, выход которого подключен ко входу дешифратора 62 номера столбца, выход переполнения счетчика 59 столбцов подсоединен к счетному входу счетчика 60 номера слоя, выход которого соединен с входом дешифратора 61 номера слоя, выход переполнения счетчика 60 номера слоя подключен к выходу 92 переполнения, выходы с первого по m-й дешифратора 61 номера слоя подсоединены к соответствующим вторым входам элементов 81.i.j ( ) объединения, выходы с первого по n-й дешифратора 62 номера столбца соединены с соответствующими первыми входами элементов 81.i.j ( ) объединения, выход которого подключен к соответствующим вторым входам элементов первого 82.1.1, второго 83.1.1, третьего 84.1.1, четвертого 85.1.1, пятого 86.1.1, шестого 87.1.1, седьмого 88.1.1 и восьмого 89.1.1 элементов И соответственно, выходы которых соединены с соответствующими s-входами первого 63.1.1, второго 64.1.1, третьего 65.1.1, четвертого 66.1.1, пятого 67.1.1, шестого 68.1.1, седьмого 69.1.1 и восьмого 70.1.1 регистров инцидентной дуги, обратные е-входы которых подключены к соответствующим обратным выходам первого 71.1.1, второго 72.1.1, третьего 73.1.1, четвертого 74.1.1, пятого 75.1.1, шестого 76.1.1, седьмого 77.1.1 и восьмого 78.1.1 SR-триггеров, а также к соответствующим первым входам первого 82.1.1, второго 83.1.1, третьего 84.1.1, четвертого 85.1.1, пятого 86.1.1, шестого 87.1.1, седьмого 88.1.1 и восьмого 89.1.1 элемента И, D-входы первого 63.1.1, второго 64.1.1, третьего 65.1.1, четвертого 66.1.1, пятого 67.1.1, шестого 68.1.1, седьмого 69.1.1 и восьмого 70.1.1 регистра инцидентной дуги соединены с соответствующим выходом блока 10 оперативной памяти, выход первого 63.1.1, второго 64.1.1, третьего 65.1.1, четвертого 66.1.1, пятого 67.1.1, шестого 68.1.1, седьмого 69.1.1 и восьмого 70.1.1 регистров инцидентной дуги подключены к соответствующим входам промежуточного 79 сумматора, выход которого подсоединен к соответствующим входам итогового 80 блока сумматоров, выход которого соединен с выходом 93 суммы устройства, R-вход восьмого 78.1.1 SR-триггера подключен к ое-выходу восьмого 70.1.1 регистра инцидентной дуги, ое–выходы первого 63.1.1, второго 64.1.1, третьего 65.1.1, четвертого 66.1.1, пятого 67.1.1, шестого 68.1.1 и седьмого 69.1.1 регистра инцидентной дуги соединены с соответствующими R-входами первого 71.1.1, второго 72.1.1, третьего 73.1.1, четвертого 74.1.1, пятого 75.1.1, шестого 76.1.1 и седьмого 77.1.1 SR-триггеров, прямой выход первого 71.1.1 SR-триггера подсоединен к выходу 91 единицы устройства, прямые выходы второго 72.1.1, третьего 73.1.1, четвертого 74.1.1, пятого 75.1.1, шестого 76.1.1, седьмого 77.1.1 и восьмого 78.1.1 SR-триггеров соединены с соответствующими выходами устройства.

Электронная модель 31 графа (фиг. 8) содержит m электронных моделей дуги, причем электронная модель 31.l дуги (l = 1, 2, …, m) содержит триггер 20.l блокировки дуги, регистр 21.l веса дуги, регистр 22.l блокировки дуги, первый элемент И 38.l, второй элемент И 39.l, элемент ИЛИ 40.l, причем входы элемента И 38.l соединены с соответствующими входами 56.y и 56.z задания графа устройства (где y и z – номера соответственно начальной и конечной вершины l-й дуги графа), выход элемента И 38.l соединен с синхровходом регистра 21.l веса дуги и с установочным входом триггера 20.l блокировки дуги, вход сброса которого соединен с l-м входом блокировки дуги модели 31, вход данных регистра 21.l веса дуги соединен с входом 54.l веса дуги устройства, первый вход элемента ИЛИ 40.l соединен с l-м управляющим входом модели 31, а второй вход элемента ИЛИ 40.l соединен с выходом элемента И 39.l, первый входкоторого соединен с прямым выходом триггера 20. l блокировки дуги и с разрешающим входом регистра 22.l блокировки дуги, второй вход элемента И 39.l соединен с l-м входом выбора дуги модели 31, вход сброса регистра 22.l блокировки дуги соединен с входом 55.l сброса устройства, выход регистра 22.l блокировки дуги соединен с l-м выходом веса дуги модели 31, который также соединен с выходом регистра 21.l веса дуги, выход элемента ИЛИ 40.l подключен к разрешающему входу регистра 21.l веса дуги.

Назначение элементов и блоков устройства для поиска минимального значения интенсивности размещения (фиг. 7) в матричных системах состоит в следующем:

Первый и второй регистры 1 и 2 сдвига необходимы для реализации последовательного перебора пар вершин орграфа G.

Блок 3 формирования перестановок осуществляет перебор всех возможных размещений вершин графа G по позициям заданной топологической модели.

Блок 4 постоянной памяти хранит двоичные коды номеров позиций.

Блок 5 запоминания лучшего варианта служит для запоминания лучшего на настоящий момент варианта размещения.

Коммутатор 6 обеспечивает последовательное списывание из блока 4 кодов номеров выбираемых позиций для передачи их в АЛУ 7.

Арифметико-логическое устройство 7 необходимо для определения расстояния между позициями, в которые помещены выбранные вершины графа, и расчета длины связей L для формируемого варианта размещения. Данное устройство способно определять расстояния между позициями как для взвешенных графов, так и для невзвешенных.

Дешифратор 8 выбора дуги вместе со счетчиком 27 дуг предназначены для выбора из ЭМГ 31 дуги с номером, записанным в счетчике 27.

Реверсивный счетчик 9 ячеек служит для организации последовательного перебора адресов блока 10 оперативной памяти в прямом и обратном порядке соответственно при записи информации и ее считывании.

Блок 10 оперативной памяти служит для хранения весов wi,j дуг орграфа G в порядке возрастания их значений.

Счетчик 11 топологии необходим для подсчета и передачи счетчику 12 количества обрабатываемых элементов вектора с заданным значением (для кольцевой топологической модели общее число таких элементов постоянно и составляет n, для линейной это число уменьшается от n-1 для =1 до 1 для =n-1).

Первый счетчик 12 расстояний и второй счетчик 13 расстояний предназначены для организации перебора в возрастающем порядке ненулевых элементов матрицы расстояний D (таким образом на выходе счетчика 13 формируется вектор ).

Умножитель 14 необходим для умножения веса дуги из блока 10 оперативной памяти на расстояние между позициями топологической модели (элемент вектора ) из счетчика 13 расстояний.

Сумматор 15 предназначен для суммирования значений с умножителя 14 и регистра 16.

Регистр 16 минимальной длины связей хранит значение минимально возможной длины связей L* для заданного графа.

Первый элемент 17 сравнения служит для сравнения веса текущей дуги с наименьшим на данный момент весом, записанным в регистре 30.

Вычитатель 18 служит для нахождения степени оптимальности размещения ξ. Значение L* поступает с выхода регистра 16 минимальной длины связей, L поступает с выхода регистра 25 длины связей.

Триггер 19 начала счета служит для индикации перехода из режима формирования размещения в режим его оценки.

Триггер 23 режима служит для хранения признака текущей операции. Если триггер 23 установлен в ноль – это означает запись весов дуг по возрастанию в блок 10 оперативной памяти, а в единицу – нахождение минимально возможной длины L*.

Триггер 24 задания топологии предназначен для задания вида топологической модели: если триггер 24 установлен в единицу – это означает выбор линейной модели, в ноль – кольцевой модели.

Дешифратор 28 блокировки дуги предназначен для выбора дуги, которую необходимо заблокировать в текущем цикле работы устройства.

Регистр 29 номера дуги служит для хранения номера дуги с минимальным весом, выбранной в текущем цикле работы устройства.

Регистр 30 минимального веса необходим для хранения значения минимального на данный момент веса дуги.

Группа элементов ИЛИ 32.1 – 32.n необходима для объединения соответствующих сигналов с регистров 1 и 2.

Группа элементов И 33.1 – 33.m предназначена для выбора соответствующих дуг графа G по сигналам с элементов ИЛИ 32.1 – 32.n.

Первый и второй элементы И 34 и 35 необходимы для блокировки передачи импульсов с тактового входа 57 устройства на элементы и блоки, обеспечивающие упорядочение весов дуг графа в блоке 10.

Второй блок элементов ИЛИ 36 необходим для подключения веса текущей дуги к элементу 17 сравнения и регистру 30.

Третий элемент И 37 предназначен для блокировки прохождения импульсов на входы синхронизации регистров 29 и 30.

Электронная модель 31 графа служит для моделирования топологии графа G, представляющего размещаемый объект (фиг. 8).

Первый и второй одновибраторы 41 и 42 необходимы для формирования импульсов, управляющих записью информации в регистр 25 и счетчик 12 соответственно.

Первый элемент 43 задержки служит для задержки импульса переполнения со счетчика 27 дуг на время, достаточное для обеспечения блокировки дуги дешифратором 28 и записи минимального веса из регистра 30 в блок 10 оперативной памяти.

Второй элемент 44 задержки необходим для задержки тактового импульса на время, достаточное для обеспечения выбора очередной дуги и сравнения ее веса с минимальным весом, записанным в регистре 30.

Третий элемент 45 задержки обеспечивает задержку импульса, поступающего на регистр 16 минимальной длины связей, на время, достаточное для подсчета и добавления очередного слагаемого формулы (1) умножителем 14 и сумматором 15.

Первый блок элементов ИЛИ 46 необходим для подачи в АЛУ 7 веса текущей дуги.

Электронная модель 31.l дуги служит для моделирования l-й дуги орграфа G, l = 1,2, …, m.

Триггер 20.l блокировки дуги служит для выдачи сигнала блокировки повторного выбора соответствующей дуги во время работы устройства.

Регистр 21.l веса дуги и регистр 22.l блокировки дуги предназначены для хранения веса текущей дуги и нулевого кода соответственно. Регистры 21.l и 22.l имеют выходы с тремя состояниями; перевод выходов в третье (высокоимпедансное) состояние обеспечивается соответственно единичным и нулевым сигналом на входах разрешения (oe).

Первый элемент И 38.l необходим для формирования сигнала наличия l-й дуги в графе.

Второй элемент И 39.l служит для формирования сигнала выбора/блокировки дуги.

Элемент ИЛИ 40.l служит для объединения сигналов с элемента И 39.l и с элемента И 33.l.

Назначение элементов блока 58 минимального значения (фиг. 7) состоит в следующем.

Счетчик 59 столбцов предназначен для подсчета количества столбцов выбранного слоя ТС.

Счетчик 60 номера слоя предназначен для выбора номера обрабатываемого в данный момент слоя ТС.

Дешифратор 61 номера служит для выбора номера строки МС.

Дешифратор 62 номера столбца необходим для выбора номера столбца слоя МС, установленной дешифратором 61 номера.

Первый 63.1.1, второй 64.1.1, третий 65.1.1, четвертый 66.1.1, пятый 67.1.1, шестой 68.1.1, седьмой 69.1.1 и восьмой 70.1.1 регистр инцидентной дуги служит для хранения объема информации, передаваемой по смежным данному процессору связям.

Первый 71.1.1, второй 72.1.1, третий 73.1.1, четвертый 74.1.1, пятый 75.1.1, шестой 76.1.1, седьмой 77.1.1 и восьмой 78.1.1 SR-триггер предназначен для активации работы соответствующих регистров инцидентной дуги.

Промежуточный 79 блок сумматоров необходим для промежуточного суммирования значений интенсивности, сохраненных в первом 63.1.1, втором 64.1.1, третьем 65.1.1, четвертом 66.1.1, пятом 67.1.1, шестом 68.1.1, седьмом 69.1.1 и восьмом 70.1.1 регистрах инцидентной дуги.

Итоговый 80 блок сумматоров предназначен для накопления значения интенсивности размещения в полносвязных тороидальных системах.

Элемент 81.1.1 И объединения предназначен для объединения сигналов с первого выхода дешифратора 62 номера столбца и первого выхода дешифратора 61 номера слоя.

Первый 82.1.1, второй 83.1.1, третий 84.1.1, четвертый 85.1.1, пятый 86.1.1, шестой 87.1.1, седьмой 88.1.1 и восьмой 89.1.1 элемент И необходим для подачи единичного импульса на соответствующие s-входы первого 63.1.1, второго 64.1.1, третьего 65.1.1, четвертого 66.1.1, пятого 67.1.1, шестого 68.1.1, седьмого 69.1.1 и восьмого 70.1.1 регистра инцидентной дуги.

Вход 90 установки необходим для установки восьмого 78.1.1 SR-триггера в единичное состояние.

Выход 91 единицы служит для выдачи на ВУУ единичного импульса, который свидетельствует о единичном состоянии первого 71.1.1 SR-триггера.

Выход 92 переполнения свидетельствует о переполнении счетчика 60 номера слоя, одновременно говорящего о завершении работы устройства.

Выход 93 суммы необходим для выдачи на ВУУ минимального значении интенсивности размещения в полносвязных тороидальных системах при двунаправленной передаче информации.

Первый 94, второй 95, третий 96, четвертый 97, пятый 98, шестой и седьмой 100 S-входы первого 71.1.1, второго 72.1.1, третьего 73.1.1, четвертого 74.1.1, пятого 75.1.1, шестого 76.1.1 и седьмого 77.1.1 SR-триггеров соответственно необходимы установки их в единичное состояние.

Первый 101, второй 102, третий 103, четвертый 104, пятый 105, шестой 106 и седьмой 107 прямые выходы соответствующих второго 72.1.1, третьего 73.1.1, четвертого 74.1.1, пятого 75.1.1, шестого 76.1.1, седьмого 77.1.1 и восьмого 78.1.1 SR-триггеров служат для подачи единичного импульса на ВУУ.

Матрица 108.i.j ( ) процессоров ТС моделирует процессорные модули многопроцессорной тороидальной системы.

Рассмотрим работу предлагаемого устройства.

Первоначально в счетчике 60 хранится код единицы («0…01»), а в счетчике 59 – код нуля («0…00»). В следствие этого, на вход дешифратора 61 поступает код единицы, из-за чего на его первом выходе появляется единичный импульс, который по ступает на второй вход элемента 81.1.1 И. В регистрах 63.1.1, 64.1.1, 65.1.1, 66.1.1, 67.1.1, 68.1.1, 69.1.1 и 70.1.1 хранится код значения нуль. Триггеры 71.1.1, 72.1.1, 73.1.1, 74.1.1, 75.1.1, 76.1.1 и 77.1.1 находятся в состоянии единица. Из-за этого, на их прямых выходах присутствует единичный потенциал, а на обратных – нулевой. Триггер 78.1.1 находится в нулевом состоянии, из-за чего на его прямом выходе присутствует нулевой потенциал, а на обратном единичный, который поступает на второй вход элемента 82.1.1 И. В сумматорах 79 и 80 хранятся коды нулей.

Предлагаемое устройство способно решать следующие задачи: размещение невзвешенных графов в линейную топологическую модель, размещение взвешенных графов в линейную и кольцевую модель и оценка степени близости сформированного размещения к оптимальному. Дополнительно предлагаемое устройство позволяет осуществлять поиск минимального значения интенсивности размещения в МС по критерию минимизации интенсивности процессов и данных.

Задача размещения невзвешенных графов с топологической моделью в виде линейки решается в устройстве аналогично прототипу. В данном случае работает только так называемая «верхняя» часть схемы, в которую входит ЭМГ 31, регистры 1 и 2, группа элементов ИЛИ 32.1 – 32.n, группа элементов И 33.1 – 31.m, блок элементов ИЛИ 46, регистр 25, элемент 26 сравнения, одновибратор 41, а также БФП 3, блок 4 постоянной памяти, БЗЛВ 5, коммутатор 6 и АЛУ 7.

Регистр 1 и регистр 2 последовательно выбирают пары вершин по мере поступления импульсов с входа 57 устройства. Сигналы выбранной пары вершин проходят через два соответствующих элемента группы элементов ИЛИ 32.1 – 32.n и далее формируют единичный сигнал на выходе соответствующего элемента И группы 33.1 – 33.m (допустим элемента 33.l). Единичный сигнал с элемента И 33.l поступает на элемент ИЛИ 40.l (модели 31.l дуги) и, попадая далее на разрешающий вход (oe) регистра 21.l, разрешает тем самым появление данных (веса l-й дуги) на выходе этого регистра. Поскольку размещаемый граф невзвешен, в регистре 21.l содержится либо код «00…01» либо код «00…00» (отсутствие дуги). Будем считать данный код ненулевым. Код «00…01» с выхода регистра 21.l поступает на блок элементов ИЛИ 46 и далее через него – в АЛУ 7. В это же время блок 3 формирования перестановок определяет для выбираемых вершин позиции, а АЛУ 7 вырабатывает команду определения расстояния между позициями, в которые следует поместить выбранные вершины графа. Это расстояние определяется по формуле . Одновременно в АЛУ 7 происходит и накопление суммарной длины связей L. Подсчет суммарной длины связей для текущего варианта размещения завершается, когда на выходе переполнения регистра 2 появляется сигнал переполнения. Одновременно этот же сигнал поступает на БФП 3, подготавливая его к формированию новой перестановки.

Перестановки формируются в пространственно-временной форме, то есть в каждый тактовый момент времени единичный сигнал инициируется только на одном (q-м) выходе БФП 3, а их последовательность задает соответствующую перестановку. Например, перестановка (3 1 2) означает, что первый тактовый импульс появляется на втором выходе БФП, второй – на третьем, третий – на первом. В соответствии с этим из блока 4 постоянной памяти (в блок 4 постоянной памяти заносятся двоичные коды номеров позиций) через коммутатор 6 в АЛУ 7 будут последовательно списываться коды второй позиции, третьей и первой. Это, в свою очередь, означает, что первая вершина помещается во вторую позицию, вторая в третью и третья в первую. Лучший вариант размещения переписывается в блок 5 и соответствующее ему значение длины связей L – в регистр 25. Появление сигнала на сигнализирующем выходе БФП 3 свидетельствует о том, что все перестановки сформированы, а лучший вариант размещения зафиксирован в БЗЛВ 5.

Задача размещения взвешенных и невзвешенных графов в линейной и/или кольцевой топологических моделях, а также задача оценки степени близости сформированного размещения к оптимальному решается так как в прототипе и поэтому здесь не рассматривается.

Задача оценки степени близости сформированного размещения к оптимальному решается следующим образом (в данном случае работает только «нижняя» часть схемы, включающая дешифраторы 8 и 28, элемент 17 сравнения, счетчики 27, 9, 11, 12 и 13, блок 10 оперативной памяти, регистры 16, 25, 29 и 30, триггеры 19, 23 и 24, умножитель 14, сумматор 15, вычитатель 18, блок элементов ИЛИ 36, элементы И 34, 35 и 37, элементы 43, 44 и 45 задержки и одновибратор 42).

При появлении единичного сигнала на сигнализирующем выходе БФП 3 триггер 19 устанавливается в единицу. Единичный сигнал с прямого выхода триггера 19 поступает на вторые входы элемента И 34 и элемента И 35. Так как триггер 23 режима находится в нулевом состоянии, элемент 35 по-прежнему остается закрытым, а элемент 34 открывается для прохождения тактовых импульсов.

Первый тактовый импульс проходит через элемент И 34, откуда этот импульс поступает на счетный вход счетчика 27 и передним фронтом устанавливает его в значение «00…01». Код с выхода счетчика 27 поступает на вход данных регистра 29 и на вход дешифратора 8, инициируя появление единицы на его первом выходе. Эта единица поступает на второй вход элемента И 39.1 (модели 31.1). Если на первом входе элемента 39.1 присутствует единица (триггер 20.1 находится в единичном состоянии), то на выходе элемента 39.1 появляется единичный сигнал выбора дуги. С выхода элемента И 39.1 этот сигнал проходит через элемент ИЛИ 40.1, поступает на разрешающий вход регистра 21.1 и открывает его выход. В результате вес дуги с регистра 21.1 проходит через блок элементов ИЛИ 36, откуда попадает на первый вход элемента 17 сравнения, на втором входе которого присутствует код из регистра 30 (первоначально «11…1»). Если код с блока элементов ИЛИ 36 (вес выбранной дуги) меньше уже имеющегося в регистре 30, на выходе элемента 17 образуется единичный сигнал. Этот единичный сигнал поступает на первый вход элемента И 37 и обеспечивает прохождение тактового импульса с элемента И 34, задержанного на элементе 44 задержки. Импульс с элемента И 37 поступает на синхровходы регистра 29 и регистра 30 и по переднему фронту записывает в них значение с выхода счетчика 27 (номер текущей дуги) и код веса выбранной