Параллельный логический мультиконтроллер

Иллюстрации

Показать всеИзобретение относится к построению коммутационных средств мультипроцессорных вычислительных и управляющих систем, абонентских систем связи с децентрализованным управлением и информационно-измерительных систем. Технический результат заключается в повышении скорости выполнения барьерной синхронизации участков параллельных программ, выполняющихся в различных модулях логического мультиконтроллера, контроллерах, за счет увеличения скорости переключения между слоями синхронизации путем параллельного распространения «волн» тактовых импульсов от одного углового модуля через всю структуру к другому угловому модулю и одновременно в обратном направлении. 6 ил.

Реферат

Изобретение относится к автоматике и вычислительной технике и может найти применение при построении распределенных систем программного управления и многопроцессорных систем широкого класса.

Известна микроконтроллерная сеть, содержащая М*N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры сети, М - число строк, каждый модуль которой включает блок памяти программ, регистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, с первого по третий элементы ИЛИ, регистр вектора соответствия, буферный регистр, первый и второй дешифраторы номера вершины синхронизации, блок элементов ИЛИ, первый и второй одновибраторы, элемент задержки, группу блоков модулей управления синхронизацией, мультиплексор каналов синхронизации, регистр конфигурации, первый и второй мультиплексоры, дешифратор каналов синхронизации, генератор сигналов управления синхронизацией, первую и вторую группы элементов И (патент РФ №2336556, МПК9 G06F 9/28, G06F 15/173, G06F 1/10; заявл. 17.04.2007, опубл. 20.10.2008. Бюл. №29).

Недостатком данной сети является невысокая скорость выполнения барьерной синхронизации (и, как следствие, недостаточное ее быстродействие при реализации параллельных алгоритмов управления) из-за последовательного характера активизации групп блоков модулей управления синхронизацией (групп барьеров).

Наиболее близкой к предлагаемому параллельному логическому мультиконтроллеру по технической сущности является логический мультиконтроллер с распределенным параллельно-конвейерным барьерным синхронизатором, содержащий М*N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры, М - число строк, включающий блок памяти программ, регистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, с первого по третий элементы ИЛИ, регистр вектора соответствия, буферный регистр, первый и второй дешифраторы номера вершины синхронизации, блок элементов ИЛИ, первый и второй одновибраторы, первый элемент задержки, первую и вторую группы элементов И, группу блоков управления синхронизацией (патент РФ №2450328, МКП9 G06F 9/00; заявл. 15.02.2010, опубл. 10.05.2012. Бюл. №13).

Недостатком данного устройства является невысокое число синхронизируемых параллельных барьеров, а также низкая скорость барьерной синхронизации участков параллельных программ.

Технической задачей заявляемого изобретения является расширения области целесообразного применения устройства, за счет увеличения максимально возможного числа синхронизируемых параллельных барьеров, а также повышение скорости выполнения барьерной синхронизации участков параллельных программ, выполняющихся в различных модулях логического мультиконтроллера (контроллерах), за счет сокращения времени переключения между слоями синхронизации путем параллельного распространения «волн» тактовых импульсов от одного углового модуля через всю структуру к другому угловому модулю и одновременно в обратном направлении.

Техническая задача решается тем, что в каждый модуль параллельного логического мультиконтроллера, содержащей М*N однотипных модулей, объединенных в матричную структуру, где N - число модулей в строке матричной структуры параллельного логического мультиконтроллера, М - число строк, включающий блок памяти программ, регистр адреса, регистр команд, мультиплексор логических условий, коммутатор адреса, блок синхронизации, первый и второй элементы ИЛИ, буферный регистр, блок элементов ИЛИ, первый и второй одновибраторы, элемент задержки, модуль синхронизатора, причем вход кода операции модуля соединен с первым информационным входом коммутатора адреса, выход которого подключен к информационному входу регистра адреса, выход которого соединен с адресным входом блока памяти программ, выход которого подключен к информационному входу регистра команд, первый выход которого соединен с адресным входом мультиплексора логических условий, а второй выход со вторым информационным выходом мультиплексора логических условий, первый информационный выход которого подключен к входу логических условий модуля, третий выход регистра команд объединен с выходом мультиплексора логических условий и подключен к первому входу блока элементов ИЛИ и к информационному входу буферного регистра, выход которого подключен ко второму входу блока элементов ИЛИ, выход которого соединен со вторым информационным входом коммутатора адреса, четвертый выход регистра команд подключен к выходу микроопераций модуля, пятый, шестой, седьмой и восьмой выходы регистра команд подключены к восьмому, двенадцатому, девятому и пятнадцатому входам модуля синхронизатора соответственно, девятый выход регистра команд подключен к третьему входу модуля синхронизатора, а также к входу первого одновибратора, выход которого соединен с третьим входом блока синхронизации, первый выход которого подключен к первому входу первого элемента ИЛИ, выход которого соединен с синхровходом регистра адреса, второй выход блока синхронизации подключен к входу сброса буферного регистра и второму входу второго элемента ИЛИ, выход которого соединен с синхровходом регистра команд, десятый выход регистра команд подключен к управляющим входам коммутатора адреса, первые информационные входы с первого по d-й (d - количество измерений контроллера) модуля синхронизатора соединены первыми выходами модулей синхронизаторов соседних модулей с первого по d-й, вторые тактовые входы с первого по d-й подключены к пятым выходам модулей синхронизаторов соседних модулей с первого по d-й, пятый и шестой вход модуля синхронизатора подключены к координатным входам модуля, седьмые информационные входы модуля синхронизатора с первого по d-й подключены к третьим выходам модулей синхронизаторов соседних модулей с первого по d-й, десятый информационный вход соединен со входом вектора соответствия модуля, одиннадцатый информационный вход подключен к входу максимального количества барьеров модуля, тринадцатые управляющие входы модуля синхронизатора с первого по d-й подключены к четвертым выходам модулей синхронизаторов соседних модулей с первого по d-й, четырнадцатый вход модуля синхронизатора соединен со входом тактовых импульсов модуля, первые выходы модуля синхронизатора с первого по d-й подключены к первым информационным входам модулей синхронизаторов соседних модулей с первого по d-й, второй выход модуля синхронизатора подключен к входу второго одновибратора и синхровходу буферного регистра, выход которого соединен с входом сброса регистра команд и вторым входам блока синхронизации, третьи выходы модуля синхронизатора с первого по d-й подключены к седьмым информационным входам модулей синхронизаторов соседних модулей с первого по d-й, пятые выходы модуля синхронизатора с первого по d-й соединены со вторыми входами модулей синхронизаторов соседних модулей с первого по d-й, четвертые выходы модуля синхронизатора с первого по d-й соединены с тринадцатыми входами модулей синхронизаторов соседних модулей с первого по d-й, первый вход блока синхронизации подключен к входу пуска модуля, вход настройки модуля соединен со вторым входом первого элемента ИЛИ, четвертым входом модуля синхронизатора, а также со входом элемента задержки, выход которого подключен к второму входу второго элемента ИЛИ, модуль синхронизатора содержит с первого по четвертый блоки элементов И, группу блоков элементов ИЛИ-НЕ с первого по d-й, первый и второй блок элементов ИЛИ-НЕ, первый и второй блок элементов ИЛИ, блок элементов И-НЕ, с первого по шестой элемент И, с первого по четвертый элемент ИЛИ, группа блоков буферных элементов с первого по р-й (р=q/n, где q - максимальное число барьеров в реализуемых программах, а n - число физических разрядов параллельного логического мультиконтроллера), блок буферных элементов, с первого по третий триггер, первый и второй блок мультиплексоров, первый и второй блок демультиплексоров, с первого по третий дешифраторы, первый и второй одновибраторы, первый и второй регистр текущего физического разряда параллельного логического мультиконтроллера, регистр максимального количества барьеров в одном физическом разряде, первый и второй регистр текущего барьера, первый и второй счетчики, регистр вектора соответствия, первый и второй компараторы, блок монтажного ИЛИ с первого по р-й, первая и вторая группа регистров значений функций, причем любой блок содержит с первого по n-й элемент, кроме блоков демультиплексоров, которые содержат с первого по n+1 демультиплексоров, первые входы элементов И из первого блока подключены к первым входам модуля синхронизатора таким образом, что первый разряд первого входа из группы первых входов модуля синхронизатора подключен к первому входу из группы первых входов первого элемента И в первом блоке, второй разряд первого входа из группы первых входов модуля синхронизатора подключен к первому входу из группы первых входов второго элемента И в первом блоке, и так далее до n-ого разряда первого входа из группы первых входов модуля синхронизатора, который подключен к первому входу из группы первых входов n-ого элемента И в первом блоке, аналогично подключены остальные разряды по n-й с первого по n-й вход группы первых входов модуля синхронизатора, который подключен к n-м входам из группы первых входов блока элементов И, выходы которого соединены с информационными входами первого блока демультиплексоров таким образом, что выход первого элемента И из первого блока подключен к информационному входу первого демультиплексора из первого блока, выход второго элемента И из первого блока подключен к информационному входу второго демультиплексора из первого блока, а выход n-ого элемента И из первого блока подключен к информационному входу n-ого демультиплексора из первого блока, первые разряды выходов демультиплексоров из первого блока подключены к информационному входу первого регистра из первой группы регистров значений функций, вторые разряды выходов демультиплексоров из первого блока подключены к информационному входу второго регистра из первой группы регистров значений функций и так далее до р-ого разряда выходов демультиплексоров из первого блока, который подключен к информационному входу р-ого регистра из первой группы регистров значений функций, первый разряд n+1-ого демультиплексора из первого блока подключен к синхровходу первого регистра из первой группы регистров значений функций, второй выход n+1-ого демультиплексора из первого блока подключен к синхровходу второго регистра из первой группы регистров значений функций и так далее до р-ого разряда n+1-ого демультиплексора из первого блока, который подключен к синхровходу р-ого регистра из первой группы регистров значений функций, с первого по n-й разряды выхода первого регистра первой группы регистров значений функций соединены с первыми разрядами информационных входов с первого по n-й мультиплексоров первого блока соответственно, с первого по n-й разряды выхода второго регистра первой группы регистров значений функций соединены со вторыми разрядами информационных входов с первого по n-й мультиплексоров первого блока соответственно и так далее до с первого по n-й разряды выхода р-ого регистра первой группы регистров значений функций, которые соединены с р-ми разрядами информационных входов с первого по n-й мультиплексоров первого блока соответственно, выходы с первого по n-й мультиплексоров подключены к первым входам с первого по n-й элементов И второго блока соответственно, а также к первому и второму входам с первого по n-й элементов ИЛИ-НЕ первого блока соответственно, выходы которых подключены к информационным входам с первого по n-й буферных элементов первого блока, выходы которого подключены к первым и вторым входам всех элементов ИЛИ-НЕ из группы блоков элементов ИЛИ-НЕ, группа вторых входов третьего элемента И соединена с группой вторых входов модуля синхронизатора, выход третьего элемента И подключен к входу первого одновибратора, выход которого подключен к информационному входу n+1-ого демультиплексора первого блока демультиплексоров, к входу инкремента первого счетчика, а также к второму входу третьего элемента ИЛИ, выход которого подключен ко всем выходам пятой группы выходов модуля синхронизатора, третий вход модуля синхронизатора подключен к синхровходу третьего триггера, четвертый вход модуля синхронизатора подключен ко всем входам сброса первой и второй группы всех регистров значений функций, первого триггера, второго триггера, первого и второго регистра текущего физического разряда параллельного логического мультиконтроллера, регистра максимального количества барьеров в одном физическом разряде, первого и второго регистра текущего барьера, первого и второго счетчика, регистра вектора соответствия, а также к первому входу первого элемента ИЛИ, выход которого подключен к входу сброса третьего триггера, прямой выход которого подключен к первым входам всех элементов И третьего блока элементов И, к первому входу второго элемента И, а также к первому входу первого элемента И, выход которого подключен к управляющему входу второго дешифратора, вход установки первого триггера подключен к пятому входу модуля синхронизатора, прямой выход первого триггера соединен со всеми управляющими входами буферных элементов блока буферных элементов, а также с первым входом шестого элемента И, выход которого подключен к первому входу четвертого ИЛИ, выход которого подключен ко всем четвертым выходам модуля синхронизатора, вход установки второго триггера подключен к шестому входу модуля синхронизатора, прямой выход второго триггера соединен с вторыми входами всех элементов И четвертого блока элементов И, а также первого входа пятого элемента И, выход которого соединен с первым входом третьего элемента ИЛИ, группа блоков элементов ИЛИ-НЕ подключена к группе седьмых входов таким образом, что первый блок в группе блоков элементов ИЛИ-НЕ подключен к первому входу из группы седьмых входов, причем первый разряд входа подключен к первому и второму входу первого элемента в первом блоке группы блоков элементов ИЛИ-НЕ, второй разряд входа подключен к первому и второму входу второго элемента в первом блоке группы блоков элементов ИЛИ-НЕ, и так далее до n-ого разряда входа, который подключен к первому и второму входу n-ого элемента в первом блоке группы блоков элементов ИЛИ-НЕ, остальные входы блоков по n-й блок элементов ИЛИ-НЕ подключаются аналогично, выходы группы блоков элементов ИЛИ-НЕ соединяются с блоком элементов И-НЕ таким образом, что выходы с первого по n-й первого блока в группе блоков элементов ИЛИ-НЕ подключены к первым входам с первого по n-й элементов И-НЕ в блоке элементов И-НЕ, выходы с первого по n-й второго блока в группе блоков элементов ИЛИ-НЕ подключены ко вторым входам с первого по n-й элементов И-НЕ в блоке элементов И-НЕ и так далее, до n-ого блока в группе блоков элементов ИЛИ-НЕ, у которого выходы с первого по n-й подключены к n-м входам с первого по n-й элементов И-НЕ в блоке элементов И-НЕ, выходы которого соединены с информационными входами второго блока демультиплексоров таким образом, что выход первого элемента И-НЕ из блока подключен к информационному входу первого демультиплексора из блока, выход второго элемента И-НЕ из блока подключен к информационному входу второго демультиплексора из второго блока, а выход n-ого элемента И-НЕ из блока подключен к информационному входу n-ого демультиплексора из блока, первые разряды выходов демультиплексоров из второго блока подключены к информационным входам первого регистра из второй группы регистров значений. функций, вторые разряды выходов демультиплексоров из второго блока подключены к информационным входам второго регистра из второй группы регистров значений функций и так далее до р-ого разряда выходов демультиплексоров из второго блока, который подключен к информационным входам р-ого регистра из второй группы регистров значений функций, первый разряд n+1-ого демультиплексора из второго блока подключен к синхровходу первого регистра из второй группы регистров значений функций, второй n+1-ого демультиплексора из второго блока подключен к синхровходу второго регистра из второй группы регистров значений функций и так далее до р-ого разряда n+1-ого демультиплексора из второго блока, который подключен к синхровходу р-ого регистра из второй группы регистров значений функций, с первого по n-й разряды выхода первого регистра второй группы регистров значений функций соединены с первыми разрядами информационных входов с первого по n-й мультиплексоров второго блока соответственно, с первого по n-й разряды выхода второго регистра второй группы регистров значений функций соединены со вторыми разрядами информационных входов с первого по n-й мультиплексоров второго блока соответственно и так далее до с первого по n-й разряды выхода р-ого регистра второй группы регистров значений функций, которые соединены с р-ми разрядами информационных входов с первого по n-й мультиплексоров второго блока соответственно, выходы с первого по n-й мультиплексоров второго блока мультиплексоров подключены ко вторым входам с первого по n-й элементов третьего блока элементов И, ко всем третьим выходам модуля синхронизатора, к первым и вторым входам с первого по n-й элементов второго блока элементов ИЛИ-НЕ, выходы которых подключены к первым входам с первого по n-й элементов четвертого блока элементов И, выходы которых подключены к первым входам с первого по n-й элементов первого блока элементов ИЛИ, выходы которого подключены к третьим входам с первого по n-й элементов первого блока элементов И, инверсный выход второго триггера соединен со вторыми входами с первого по n-й элементов первого блока элементов ИЛИ, а также к первому входу третьего элемента И, информационный вход первого регистра текущего физического разряда параллельного логического мультиконтроллера соединен с восьмым входом модуля синхронизатора, причем старший разряд восьмого входа модуля синхронизатора подключен к синхровходу первого регистра текущего физического разряда параллельного логического мультиконтроллера, выход которого подключен к информационному входу второго дешифратора, выходы которого с первого по n-й соединены со вторыми входами с первого по n-й элементов второго блока элементов ИЛИ, выходы которого подключены к вторым входам с первого по n-й элементов первого блока элементов И, информационный вход второго регистра текущего физического разряда параллельного логического мультиконтроллера соединен с девятым входом модуля синхронизатора, причем старший разряд восьмого входа модуля синхронизатора подключен к синхровходу второго регистра текущего физического разряда параллельного логического мультиконтроллера, выход которого подключен к информационному входу третьего дешифратора, выходы которого с первого по n-й соединены с третьими входами с первого по n-й элементов третьего блока элементов И, выходы которого соединены со входами второго элемента ИЛИ, выход которого подключен к второму выходу модуля синхронизатора, а также к входу первого элемента ИЛИ, информационный вход регистра вектора соответствия соединен с десятым входом модуля синхронизатора, причем старший разряд десятого входа модуля синхронизатора подключен к синхровходу регистра вектора соответствия, выходы которого подключены к информационным входам группы блоков буферных элементов таким образом, что с первого по n-й разряд первого выхода регистра вектора соответствия подключается к информационным входам с первого по n-й буферным элементам первого блока группы блоков буферных элементов, с второго по р-й выходы регистра вектора соответствия подключаются к информационным входам с второго по р-й блоков группы блоков буферных элементов аналогично, выходы группы блоков буферных элементов коммутируются блоком монтажного ИЛИ, выходы которого с первого по n-й подключаются ко вторым входам с первого по n-й элемент первого блока элементов И, информационный вход регистра максимального количества барьеров в одном физическом разряде соединен с одиннадцатым входом модуля синхронизатора, причем старший разряд одиннадцатого входа модуля синхронизатора подключен к синхровходу регистра максимального количества барьеров в одном физическом разряде, выход которого подключен к информационному входу второго счетчика, а также информационному входу первого счетчика, выход которого подключен к информационному входу первого дешифратора, управляющим входам с первого по n+1-й демультиплексоров первого блока демультиплексоров, к управляющим входам с первого по n-й мультиплексоров первого блока мультиплексоров, а также к первому информационному входу первого компаратора, выход которого подключен ко второму входу первого элемента И, с первого по р-й выход первого дешифратора соединены с управляющими входами с первого по р-й блоков группы блоков буферных элементов, выход второго счетчика подключен к управляющим входам с первого по n+1-й демультиплексоров второго блока демультиплексоров, к управляющим входам с первого по n-й мультиплексоров второго блока мультиплексоров, а также к второму информационному входу второго компаратора, выход которого подключен ко второму входу второго элемента И, выход которого подключен к управляющему входу третьего дешифратора, информационный вход первого регистра текущего барьера соединен с двенадцатым входом модуля синхронизатора, причем старший разряд восьмого входа модуля синхронизатора подключен к синхровходу первого регистра текущего барьера, выход которого подключен к второму информационному входу первого компаратора, группа вторых входов четвертого элемента И соединена с группой тринадцатых входов модуля синхронизатора, выход четвертого элемента И подключен к входу второго одновибратора, выход которого подключен к информационному входу n+1-ого демультиплексора второго блока демультиплексоров, к входу инкремента второго счетчика, а также к второму входу четвертого элемента ИЛИ, инверсный выход первого триггера подключен к первому входу четвертого элемента И, а также к вторым входам с первого по n-й элемент второго блока элементов И, выходы которого подключены ко всем первым выходам модуля синхронизатора, вторые входы пятого и шестого элемента И подключены к четырнадцатому входу модуля синхронизатора, информационный вход второго регистра текущего барьера соединен с пятнадцатым входом модуля синхронизатора, причем старший разряд пятнадцатого входа модуля синхронизатора подключен к синхровходу второго регистра текущего барьера, выход которого подключен первому информационному входу второго компаратора, к информационному входу третьего триггера подключен сигнал логической единицы.

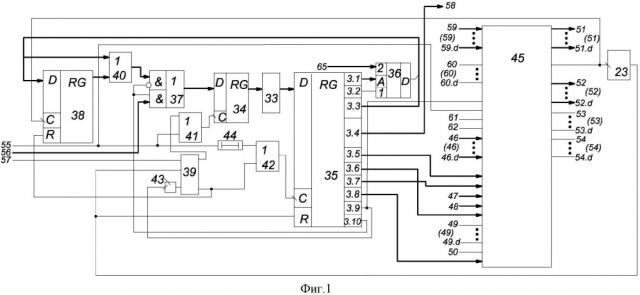

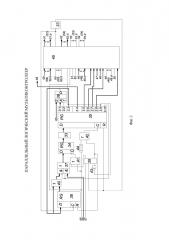

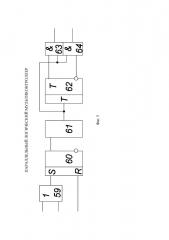

Сущность изобретения поясняется чертежами, где на фиг. 1 представлена функциональная схема модуля параллельного логического мультиконтроллера (ПЛМК), на фиг. 2 изображена функциональная схема модуля синхронизатора, на фиг 3 представлена схема блока синхронизации, на фиг. 4 дана структурная схема ПЛМК, на фиг. 5 приведены форматы (микро)команд, реализуемые ПЛМК, на фиг. 6 представлен иллюстративный пример, поясняющий принципы реализации параллельных алгоритмов (программ) в ПЛМК.

Модуль ПЛМК (фиг. 1) включает блок 33 памяти программ, регистр 34 адреса, регистр 35 команд, мультиплексор 36 логических условий, коммутатор 37 адреса, блок 39 синхронизации, первый 41, второй 42 элементы ИЛИ, буферный регистр 38, блок элементов ИЛИ 40, первый 43 и второй 23 одновибраторы, элемент 44 задержки, модуль 45 синхронизатора, причем вход 56 кода операции модуля соединен с первым информационным входом коммутатора 37 адреса, выход которого подключен к информационному входу регистра 34 адреса, выход которого подключен к адресному входу блока 33 памяти программ, выход которого соединен с информационным входом регистра 35 команд, выходы 3.1 кода логического условия и 3.2 модифицируемого разряда адреса регистра 35 команд подключены к адресному и первому информационному входам мультиплексора 36 логических условий, второй информационный вход которого соединен со входом 65 логических условий модуля, выход 3.3 регистра 35 команд объединен с выходом мультиплексора 36 логических условий и подключен к первому входу блока элементов ИЛИ 40 и к информационному входу буферного регистра 38, выход которого подключен ко второму входу блока элементов ИЛИ 40. выход которого соединен со вторым информационным входом коммутатора 37 адреса, выход 3.4 регистра команд подключен к выходу 58 микроопераций модуля, выходы 3.5, 3.6, 3.7 и 3.8 регистра 35 команд подключены к восьмому, двенадцатому, девятому и пятнадцатому входам модуля 45 синхронизатора соответственно, выход 3.9 регистра команд подключен к третьему входу модуля 45 синхронизатора, а также к входу одновибратора 43, выход которого соединен с третьим входом блока 39 синхронизации, первый выход которого подключен к первому входу элемента ИЛИ 41, выход которого соединен с синхровходом регистра 34 адреса, второй выход блока 39 синхронизации подключен к входу сброса буферного регистра 38 и второму входу элемента ИЛИ 42, выход которого соединен с синхровходом регистра 35 команд, выход 3.10 регистра 35 команд подключен к управляющим входам коммутатора 37 адреса, информационные входы 59 с первого по d-й модуля 45 синхронизатора соединены выходами 51 модулей синхронизаторов соседних модулей с первого по d-й, тактовые входы 60 с первого по d-й подключены к выходам 54 модулей синхронизаторов соседних модулей с первого по d-й, входы 61 и 62 модуля 45 синхронизатора подключены к координатным входам модуля, информационные входы 46 модуля 45 синхронизатора с первого по d-й подключены к выходам 52 модулей синхронизаторов соседних модулей с первого по d-й, информационный вход 47 модуля 45 синхронизатора соединен со входом вектора соответствия модуля, информационный вход 48 модуля 45 синхронизатора подключен к входу максимального количества барьеров модуля, управляющие входы 49 модуля 45 синхронизатора с первого по d-й подключены к выходам 53 модулей синхронизаторов соседних модулей с первого по d-й, вход 50 модуля синхронизатора соединен со входом тактовых импульсов модуля, выходы 52 модуля 45 синхронизатора с первого по d-й подключены к информационным входам 59 модулей синхронизаторов соседних модулей с первого по d-й, второй выход модуля 45 синхронизатора подключен к входу одновибратора 23, выход которого соединен с входом сброса регистра 35 команд и вторым входам блока 39 синхронизации, и синхровходу буферного регистра 38, выходы 52 модуля 45 синхронизатора с первого по d-й подключены к информационным входам 46 модулей синхронизаторов соседних модулей с первого по d-й, выходы 54 модуля 45 синхронизатора с первого по d-й соединены со входами 60 модулей 45 синхронизаторов соседних модулей с первого по d-й, выходы 53 модуля 45 синхронизатора с первого по d-й соединены со входами 49 модулей синхронизаторов соседних модулей с первого по d-й, первый вход блока 39 синхронизации подключен к входу 57 пуска модуля, вход 55 настройки модуля соединен со вторым входом элемента ИЛИ 41, четвертым входом модуля 45 синхронизатора, а также со входом элемента задержки 44, выход которого подключен к второму входу элемента ИЛИ 42.

Модуль синхронизатора (фиг. 2) содержит блоки 13, 10, 11, 12 элементов И, блок 21 элементов И-НЕ, элементов группу 22 блоков элементов ИЛИ-НЕ, блоки 19, 20 элементов ИЛИ-НЕ, блоки 11, 16 элементов ИЛИ, элементы 14.1, 14.2, 29, 27, 31, 28 И, элементы 18, 24, 15, 25 ИЛИ, группа 8 блоков буферных элементов, блок 9 буферных элементов, триггеры 7.1, 7.2, 7.3, блоки 3.1, 3.2 мультиплексоров, блоки 2.1, 2.2 демультиплексоров, дешифраторы 5.1, 5.2, 5.3, одновибраторы 30, 26, регистры 1.6, 1.7 текущего физического разряда ПЛМК, регистр 1.4 максимального количества барьеров в одном физическом разряде, регистры 1.5, 1.8 текущего барьера, счетчики 4.1, 4.2, регистр 1.3 вектора соответствия, компараторы 6.1, 6.2, блок 32 монтажного ИЛИ, группы 1.1, 1.2 регистров значений функций, первые входы элементов И из первого блока 13 элементов И подключены к первым входам модуля синхронизатора таким образом, что первый разряд входа из группы первых входов модуля синхронизатора подключен к первому входу из группы первых входов элемента И 13.1 в блоке 13, второй разряд первого входа из группы первых входов модуля синхронизатора подключен к первому входу из группы первых входов элемента И 13.2 в блоке 13, и так далее до n-ого разряда первого входа из группы первых входов модуля синхронизатора, который подключен к первому входу из группы первых входов элемента И 13.n в блоке 13, аналогично подключены остальные разряды по n-й с первого по d-й вход группы первых входов модуля синхронизатора, который подключен к d-м входам из группы первых входов блока 13 элементов И, выходы которого соединены с информационными входами блока 2.1 демультиплексоров таким образом, что выход элемента И 13.1 из блока 13 подключен к информационному входу демультиплексора 2.1.1 из блока 2.1, выход элемента И 13.2 из блока 13 подключен к информационному входу демультиплексора 2.1.2 из блока 2.1, а выход элемента И 13.п из блока 13 подключен к информационному входу демультиплексора 2.1.п из блока 2.1, первые разряды выходов демультиплексоров из блока 2.1 подключены к информационному входу регистра 1.1.1 из группы 1.1 регистров значений функций, вторые разряды выходов демультиплексоров из блока 2.1 подключены к информационному входу регистра 1.1.2 из группы 1.1 регистров значений функций и так далее до р-ого разряда выходов демультиплексоров из блока 2.1, который подключен к информационному входу регистра 1.1.р из группы 1.1 регистров значений функций, первый разряд демультиплексора 2.1.n+1 из блока 2.1 подключен к синхровходу регистра 1.1.1 из группы 1.1 регистров значений функций, второй выход демультиплексора 2.1.n+1 из блока 2.1 подключен к синхровходу регистра 1.1.2 из группы 1.1 регистров значений функций и так далее до р-ого разряда демультиплексора 2.1.n+1 из блока 2.1, который подключен к синхровходу регистра 1.1.р из группы 1.1 регистров значений функций, с первого по n-й разряды выхода регистра 1.1.1 группы 1.1 регистров значений функций соединены с первыми разрядами информационных входов с 3.1.1 по 3.1.п мультиплексоров блока 3.1 соответственно, с первого по n-й разряды выхода регистра 1.1.2 группы 1.1 регистров значений функций соединены со вторыми разрядами информационных входов с 3.1.1 по 3.1.п мультиплексоров блока 3.1 соответственно и так далее до с первого по n-й разряды выхода регистра 1.1.р группы 1.1 регистров значений функций, которые соединены с р-ми разрядами информационных входов с 3.1.1 по 3.1.п мультиплексоров блока 3.1 соответственно, выходы с 3.1.1 по 3.1.п мультиплексоров подключены к первым входам элементов И с 10.1 по 10.п блока 10 соответственно, а также к первому и второму входам элементов ИЛИ-НЕ с 19.1 по 19.п блока 19 соответственно, выходы которых подключены к информационным входам буферных элементов с 9.1 по 9.п блока 9, выходы которого подключены к первым и вторым входам всех элементов ИЛИ-НЕ из группы 22 блоков элементов ИЛИ-НЕ, группа вторых входов элемента И 29 соединена с группой вторых входов модуля синхронизатора, выход элемента И 29 подключен к входу одновибратора 30, выход которого подключен к информационному входу демультиплексора 2.1.п блока 2.1 демультиплексоров, к входу инкремента счетчика 4.1, а также к второму входу элемента ИЛИ 15, выход которого подключен ко всем выходам пятой группы выходов модуля синхронизатора, третий вход модуля синхронизатора подключен к синхровходу триггера 7.3, четвертый вход модуля синхронизатора подключен ко всем входам сброса группы 1.1, 1.2 регистров значений функций, триггера 7.1, триггера 7.2, регистров 1.6, 1.7 текущего физического разряда ПЛМК, регистра 1.4 максимального количества барьеров в одном физическом разряде, регистров 1.5, 1.8 текущего барьера, счетчиков 4.1, 4.2, регистра 1.3 вектора соответствия, а также к первому входу элемента ИЛИ 18, выход которого подключен к входу сброса триггера 7.3, прямой выход которого подключен к первым входам всех элементов И блока 11 элементов И, первому входу элемента И 14.2, а также к первому входу элемента И 14.1, выход которого подключен к управляющему входу дешифратора 5.2, вход установки триггера 7.1 подключен к пятому входу модуля синхронизатора, прямой выход триггера 7.1 соединен со всеми управляющими входами буферных элементов блока 9 буферных элементов, а также с первым входом элемента И 28, выход которого подключен к первому входу элемента ИЛИ 25, выход которого подключен ко всем четвертым выходам модуля синхронизатора, вход установки триггера 7.2 подключен к шестому входу модуля синхронизатора, прямой выход триггера 7.2 соединен с вторыми входами всех элементов И блока 12 элементов И, а также первого входа элемента И 31, выход которого соединен с первым входом элемента ИЛИ 15, группа 22 блоков элементов ИЛИ-НЕ подключена к группе седьмых входов таким образом, что блок 22.1 в группе 22 блоков элементов ИЛИ-НЕ подключен к первому входу из группы седьмых входов, причем первый разряд входа подключен к первому и второму входу элемента 22.1.1 в блоке 22.1 группы 22 блоков элементов ИЛИ-НЕ, второй разряд входа подключен к первому и второму входу элемента 22.1.2 в блоке 22.1 группы 22 блоков элементов ИЛИ-НЕ, и так далее до n-ого разряда входа, который подключен к первому и второму входу элемента 22.1.n в первом блоке 22.1 группы 22 блоков элементов ИЛИ-НЕ, остальные входы блоков по блок 22.а1 элементов ИЛИ-НЕ подключаются аналогично, выходы группы 22 блоков элементов ИЛИ-НЕ соединяются с блоком 21 элементов И-НЕ таким образом, что выходы с первого по n-й блока 22.1 в группе 22 блоков элементов ИЛИ-НЕ подключены к первым входам элементов И-НЕ в блоке 21 элементов И-НЕ с 21.1 по 21.n, выходы с первого по n-й блока 22.2 в группе блоков элементов ИЛИ-НЕ подключены к вторым входам элементов И-НЕ в блоке 21 элементов И-НЕ с 21.1 по 21.п и так далее, до блока 22.й в группе 22 блоков элементов ИЛИ-НЕ, у которого выходы с первого по n-й подключены к d-м входам элементов И-НЕ с 21.1 по 21.n в блоке 21 элементов И-НЕ, выходы которого соединены с информационными входами блока 2.2 демультиплексора таким образом, что выход элемента И-НЕ 21.1 из блока 21 подключен к информационному входу демультиплексора 2.2.1 из блока 2.2, выход элемента И-НЕ 21.2 из блока подключен к информационному входу демультиплексора 2.2.2 из блока 2.2, а выход элемента И-НЕ 21.n из блока 21 подключен к информационному входу демультиплексора 2.2.n из блока 2.2, первые разряды выходов демультиплексоров из блока 2.2 подключены к информационным входам регистра 1.2.1 из группы 1.2 регистров значений функций, вторые разряды выходов демультиплексоров из блока 2.2 подключены к информационным входам регистра 1.2.2 из группы 1.2 регистров значений функций и так далее до р-ого разряда выходов демультиплексоров из блока 2.2, который подключен к информационным входам регистра 1.2.р из группы 1.2 регистров значений функций, первый разряд демультиплексора 2.2.n+1 из блока 2.2 подключен к синхровходу регистра 1.2.1 из группы 1.2 регистров значений функций, второй демультиплексора 2.1.n+1 из блока 2.1 подключен к синхровходу регистра 1.2.2 из группы 1.2 регистров значений функций и так далее до р-ого разряда демультиплексора 2.2.n из блока 2.2, который подключен к синхровходу регистра 1.2.р из группы 1.2 регистров значений функций, с первого по n-й разряды выхода регистра 1.2.1 группы 1.2 регистров значений функций соединены с первыми разрядами информационных входов мультиплексоров с 3.2.1 по 3.2.n блока 3.2 соответственно, с первого по n-й разряды выхода регистра 1.2.2 группы 1.2 регистров значений функций соединены со вторыми разрядами информационных входов мультиплексоров с 3.2.1 по 3.2.п блока 3.2 соответственно и так далее до с первого по n-й разряды выхода регистра 1.2.р группы 1.2 регистров значений функций, которые соединены с р-ми разрядами информационных входов мультиплексоров с 3.2.1 по 3.2.п второго блока соответственно, выходы мультиплексоров с 3.2.1 по 3.2.п подключены ко вторым входам элементов с 11.1 по 11.n блока 11 элементов И, ко всем третьим выходам модуля синхронизатора, к первым и вторым входам с элементов 20.1 по 20.n блока 20 элементов ИЛИ-НЕ, выходы которых подключены к первым входам элементов с 12.1 по 12.n блока 12 элементов И, выходы которых по