Режим слежения в устройстве обработки в системах трассировки команд

Иллюстрации

Показать всеИзобретение относится к области процессорных устройств. Техническим результатом является недопущение ошибок и сбоев при изменении режима выполнения в процессе выполнения команд за счет трассировки команд с учетом режима выполнения. Устройство обработки для трассировки команд содержит: модуль трассировки команд (IT), выполненный с возможностью: приема указания на изменение текущего режима выполнения в устройстве обработки; определения, что текущий режим выполнения, соответствующий принятому указанию, отличен от значения режима выполнения, содержащегося в первом пакете режима выполнения (ЕМ), ранее сгенерированном IT-модулем; и генерации, на основе определения отличия текущего режима выполнения, второго ЕМ-пакета, предоставляющего значение текущего режима выполнения в устройстве обработки, для указания изменения режима выполнения команды на трассе, генерируемой IT-модулем. 2 н. и 10 з.п. ф-лы, 17 ил.

Реферат

Область техники, к которой относится изобретения

Варианты настоящего изобретения относятся в общем случае к процессорным устройствам и, более конкретно, относятся к режиму слежения в процессорных устройствах в системе трассировки команд.

Уровень техники

Система трассировки команд (instruction tracing system (ITS)) представляет собой средство трассировки, формирующее трассу потока управления выполнением программы. Трасса передается на выход в форме пакетов переменного размера. Декодер может использовать эти пакеты вместе с байтами ассоциированных команд для восстановления потока исполнения отслеживаемой программы.

Краткое описание чертежей

Настоящее изобретение будет более полно понятно из приведенного ниже описания и из прилагаемых чертежей различных вариантов изобретения. Эти чертежи, однако, следует рассматривать не как ограничение изобретения конкретными вариантами, а только как средство для лучшего разъяснения и понимания.

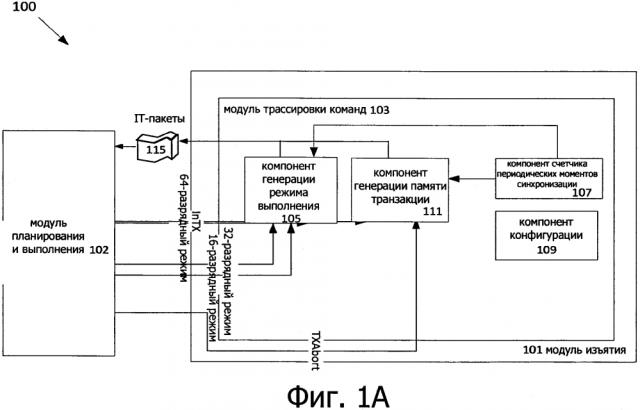

Фиг. 1А иллюстрирует пример архитектуры системы трассировки команд (instruction tracing system (ITS)) в процессорном устройстве, в соответствии с которой могут работать варианты настоящего изобретения.

Фиг. 1В иллюстрирует таблицу примеров последовательности команд, выполняемой системой ITS, и пакетов трассировки команд (instruction tracing (IT)), генерируемых системой ITS для отслеживания режима выполнения программы в трассе команд.

Фиг. 1С иллюстрирует таблицу примеров последовательности команд, выполняемой системой ITS, и IT-пакетов, генерируемых системой ITS для отслеживания режима выполнения операций памяти транзакций в трассе команд.

Фиг. 2А представляет блок-схему, иллюстрирующую пример конвейера с выполнением команд по порядку, а также пример конвейера с внеочередной выдачей/выполнением команд и переименованием регистров согласно рассматриваемым вариантам.

Фиг. 2В представляет блок-схему, иллюстрирующую пример архитектуры ядра с выполнением команд по порядку, а также пример архитектуры ядра с внеочередной выдачей/выполнением команд и переименованием регистров для включения в состав процессора согласно рассматриваемым вариантам.

Фиг. 3 представляет логическую схему, иллюстрирующую пример способа прослеживания режима выполнения в трассе команд в системе ITS.

Фиг. 4 представляет логическую схему, иллюстрирующую пример способа прослеживания выполнения операций памяти транзакций в трассе команд в системе ITS.

Фиг. 5 представляет блок-схему, иллюстрирующую процессор согласно одному из вариантов.

Фиг. 6А иллюстрирует пример альтернативной архитектуры, в соответствии с которой могут работать варианты настоящего изобретения.

Фиг. 6В показывает схематичное представление системы, в соответствии с которой варианты настоящего изобретения могут работать, быть инсталлированы, интегрированы или конфигурированы.

Фиг 7 иллюстрирует блок-схему компьютерной системы согласно одному из вариантов.

Фиг. 8 представляет блок-схему системы на кристалле (system on chip (SoC)) согласно одному из вариантов настоящего изобретения.

Фиг. 9 представляет блок-схему одного из вариантов системы на кристалле (SOC).

Фиг. 10 иллюстрирует блок-схему компьютерной системы согласно одному из вариантов.

Фиг. 11 иллюстрирует блок-схему компьютерной системы согласно одному из вариантов.

Фиг. 12 иллюстрирует блок-схему планшетного вычислительного устройства, смартфона или другого мобильного устройства, в котором использованы соединители интерфейса сенсорного экрана.

Фиг. 13 иллюстрирует схематичное представление машины в форме примера компьютерной системы, где может выполняться набор команд, в соответствии с которыми машина может осуществлять один или несколько рассматриваемых здесь способов.

Подробное описание

Здесь рассмотрены варианты режима слежения в процессорных устройствах в системе трассировки команд (instruction tracing (IT)). Режим слежения предоставляет информацию, позволяющую отладить исполняемое программное обеспечение в процессе трассировки команд. В одном из вариантов эта информация содержит индикацию события в выполняемой программе, которое изменило режим выполнения в процессорном устройстве, включая индикацию измененного режима. В другом варианте эта информация содержит изменение состояния операции трансакции с памятью в этом процессорном устройстве.

В IT-системе IT-пакеты указывают поток управления программы, выполняемой процессорным устройством. В таком случае IT-пакеты могут показывать информацию о разрешении для всех трассируемых ветвей и событий, так что при соединении с информацией об исходных командах можно воспроизвести поток управления программы. Для отслеживания режима выполнения IT-пакетов декодер должен знать состояние режима выполнения для каждой команды в трассе. Режим выполнения диктует, каким образом процессор интерпретирует байты команд, и может быть изменен программой в любой момент. Поэтому осведомленность о режиме выполнения позволяет декодеру правильно интерпретировать байты команд на основе двоичных файлов программы. Прослеживая и сохраняя трассу режима выполнения в процессоре для каждой команды, декодер может точно дезассемблировать байты команды для получения такой же самой команды, которую выполнял процессор, с целью воспроизведения точного потока управления.

В одном из вариантов предложен IT-модуль для генерации пакета режима выполнения (execution mode (ЕМ)), представленного двухбитовой структурой в пакете в выходном журнале (логе), генерируемом этим IT-модулем. Такой ЕМ-пакет создает индикацию текущего режима выполнения в процессорном устройстве и может быть сформирован каждый раз, когда режим выполнения изменяется. Этот ЕМ-пакет должен тогда указывать величину нового режима выполнения в процессоре.

Применительно к ЕМ-пакетам указанный IT-модуль может использовать компонент счетчика периодических моментов синхронизации из состава процессора, чтобы определить, когда передавать на выход ЕМ-пакеты, указывающие текущий режим выполнения в процессоре. В одном из вариантов ЕМ-пакеты указывают событие в программе, которое изменяет режим выполнения в процессоре, а также дают индикацию измененного режима. В одном из вариантов IT-модуль может содержать компонент для генератора режима выполнения, который генерирует ЕМ-пакеты, содержащие двухбитовую структуру. Этот ЕМ-пакет может предоставлять индикацию изменения в режиме выполнения в процессоре для команды, отслеживаемой IT-модулем. Например, различные сочетания битов в двухбитовой структуре представляют разные режимы выполнения в процессоре. В одном из вариантов компонент генератора режима выполнения также генерирует пакет указателя команды режима выполнения (execution mode instruction pointer (EMIP)) вместе с ЕМ-пакетом. Этот EMIP-пакет содержит указатель команды (instruction pointer (IP)), соответствующей первой команде, выполняемой в измененном режиме выполнения, ассоциированном с ЕМ-пакетом. В одном из вариантов указатель IP обозначает адрес выполнения в начале трассы команд.

Для правильного декодирования трассы IT-декодер, который принимает выходной IT-журнал, должен знать режим выполнения для каждой команды в трассе. Таким образом, для точного декодирования команд из статических двоичных файлов IT-декодер должен знать первоначальный режим и начальный указатель команды (IP), соответствующий началу журнала трассировки. Затем декодер переходит к «прогулке» по двоичному изображению, декодируя команды и определяя их результат (выход) на основе IT-журнала. Когда программа выполняет операцию изменения режима, измененный режим необходимо сообщить IT-декодеру. Процессор начинает применять информацию измененного режима к процессу декодирования записанных в процессоре команд в двоичной форме и, аналогично, декодер обязан также применить эту информацию режима к декодированию команд, хранящихся в статических двоичных файлах. Если процессор и декодер становятся несинхронизированными один с другим с точки зрения информации режима, эти процессор и декодер могут интерпретировать байты команд по-разному и, вследствие этого выполнять и просматривать разные команды, соответственно. В таком случае, IT-журнал, генерируемый процессором, скорее всего, будет несогласован с интерпретацией байтов команд, осуществляемой декодером, что вероятно приведет к ошибкам и сбоям процесса декодирования. Наконец, поскольку иногда бывает желательно начать декодирование с середины выходного журнала, IT-модуль может периодически вставлять индикатор состояния режимы и указатель IP в выходной журнал для создания дополнительных жизнеспособных начальных точек декодирования.

Как обсуждается выше, IT-пакеты служат индикаторами потока управления программы. Эти IT-пакеты используются декодером для реконструкции потока выполнения трассируемой программы. Во избежание сбоев декодера из-за передачи пакетов для команд, которые реально не «завершили» (не зафиксировали) свое состояние, генерация пакетов происходит в периоды «изъятия». Это позволяет избежать генерации пакетов для спекулятивных операций (операций по предположению), которые могут быть отброшены процессорным устройством, такие как команды, выполняемые по пути, соответствующему неверному предположению. Благодаря операциям памяти транзакций (transactional memory (ТМХ)) команды теперь изымаются спекулятивно, так что их результаты (состояние регистров, записи в памяти и т.п.) завершаются (фиксируются) только в более поздний момент. В ходе транзакции команды изымаются обычным путем, но состояние фиксируется только в том случае, когда транзакция завершается фиксацией. Если транзакция отбрасывается, все изменения состояния, произведенные спекулятивными (по предположению) командами, включая уже изъятые команды, «откатываются» назад. В такой ситуации полезно предоставить IT-декодеру информацию о том, какие команды зафиксировали (завершили) свое состояние, а какие не зафиксировали свое состояние, и о ТМХ-командах, ассоциированных с этими состояниями.

В одном из вариантов IT-модуль может также генерировать пакеты памяти транзакций (ТМХ), представленные двухбитовой структурой указания режима в пакете в выходном журнале, генерируемом IT-модулем. Один бит может указывать, находится ли ТМХ-транзакция в процессе выполнения, так что изъятия команд (и пакеты, ассоциированные с этими командами) являются спекулятивными. В одном из вариантов этот бит следует задать, когда транзакция начинается, и сбрасывать, когда эта транзакция завершается или фиксируется. Другой бит может указывать, что произошло отбрасывание команды, так что все состояния, модифицированные спекулятивными ТМХ-командами, следует «откатить» назад.

В одном из вариантов настоящего изобретения IT-модуль может содержать компонент генератора памяти транзакций, который генерирует пакеты памяти транзакций (ТМХ) на основе двухбитовых структур указания режима, которые указывают начальную точку транзакции ТМХ и все точки, где происходило изменение состояния, в выходном IT-журнале. В одном из вариантов такая точка изменения состояния указывает, что произошло состояние отбрасывания в ТМХ-операции. Это состояние отбрасывания означает, что команды между начальной точкой ТМХ-операции и точкой отбрасывания не зафиксировали свое состояние. Ранее, декодер мог не знать, что команды выполняются спекулятивно, в рамках транзакции, и, если транзакция была отброшена, что результаты следует откатить назад. В такой ситуации, не зная об изменении в состоянии ТМХ-операции, процессор может неправильно представить поток выполнения в процессоре и обновления состояния процессора. Более того, состояние отбрасывания в ТМХ-операции может вызвать переход потока управления. В такой ситуации, если не иметь индикации об отбрасывании ТМХ-операции, включая указатели команд (IT) источника и адресата этого события отбрасывания, декодер может оказаться несинхронизированным с реальным потоком управления выполнением, вследствие чего генерируемые пакеты IT-журнала могут оказаться несогласованными с тем, как декодер выполняет трассировку.

В другом варианте процессор может исключать пакеты, генерируемые отброшенными и потому незафиксированными спекулятивно выполненными командами. Однако для процессора может быть затруднительно сохранять выходные пакеты в буфере, если только процессор не отбрасывает или не фиксирует ТМХ-область команд. В альтернативном варианте процессор может попытаться создать резервную копию указателя записи в выходном журнале трассировки, удаляя, таким образом, эти пакеты из журнала трассировки. Но это может быть затруднительно в случае больших ТМХ-областей с большим числом пакетов, где системный компонент периодически архивирует выходной журнал пакетов на энергонезависимом носителе для хранения информации, так что начальная точка отбрасываемой области уже была архивирована. Наконец, для отладчика может оказаться полезным и ценным проанализировать поток выполнения в отбрасываемой области, что поможет определить причины отбрасывания.

Аналогично ЕМ-пакетам декодеру желательно определить ТМХ-состояние процессора в момент начала трассировки. Столкнувшись с ТМХ-состоянием отбрасывания, декодер может засомневаться, не «видел» ли он начальное ТМХ-состояние. В таком случае декодер может не знать, какие выполненные и обработанные пакетированные результаты нужно исключить вследствие отбрасывания. Также аналогично ЕМ-пакетам, ТМХ-пакеты могут быть вставлены в выходной журнал в качестве ТМХ-событий, происходящих во время выполнения в процессоре. И наконец, аналогично ЕМ-пакетам, IT-модуль может вставить информацию ТМХ-состояния как часть периодических моментов синхронизации для создания дополнительных стартовых точек декодера, которые содержат все состояния процессора, необходимые для декодирования выходного журнала.

Следует отметить, что другие типы информации о режимах процессора могут обрабатываться аналогично в том смысле, что пакеты состояния в выходном журнале записывают в начале трассы и затем в периодические моменты синхронизации, равно как пакеты событий, указывающие на изменения режима, вставляют в выходной журнал в моменты времени, когда происходят соответствующие события. Информация о режиме может содержать информацию, необходимую для правильного декодирования двоичного кода, и может содержать информацию, полезную, чтобы охарактеризовать поведение различных компонентов. Такая информация о режимах содержит, не ограничиваясь, правила упорядочения памяти, указание строгого или приблизительного следования правилам IEEE округления чисел с плавающей запятой, указатель на основание таблицы страниц, частоту процессора, частоту системы, базовый (начальный) адрес сегмента кода, базовый адрес сегмента данных, указатель на основание структуры управления виртуальной машиной, напряжение питания процессора, состояние питания процессора, состояние питания системы, сведения о снижении питания/выключении компонентов и т.п.

В последующем описании приведены многочисленные конкретные подробности (например, различные варианты реализации логических IT-устройств, форматы IT-пакетов, подробности секционирования аппаратуры/встроенного программного обеспечения, подробности секционирования/интеграции логических устройств, конфигурации процессора, подробности микро-архитектуры, последовательности операций, типы и взаимоотношения компонентов системы и т.п.). Однако понятно, что варианты настоящего изобретения могут быть осуществлены на практике и без этих конкретных подробностей. В других случаях хорошо известные схемы, структуры и способы не были показаны подробно, чтобы не затемнять понимание настоящего изобретения.

Фиг. 1А иллюстрирует пример архитектуры 100 процессорного устройства согласно тому, какие варианты могут работать с использованием IT-архитектуры, генерирующей пакеты 115 трассировки команд (instruction trace (IT)). В одном из вариантов устройство обработки представляет собой центральный процессор (CPU).

Более конкретно, модуль 101 изъятия содержит IT-модуль 103, который принимает информацию от модуля 102 планирования и исполнения и пакетирует эту информацию (например, значение текущего режима выполнения, ассоциированное с командами в трассе) для вывода в форме IT-пакетов 115, передаваемых в модуль 102 планирования и выполнения. Указанный IT-модуль 103 может содержать компонент 105 генератора режима выполнения (EMGC), который принимает значения текущего режима выполнения от модуля 102 планирования и выполнения. Как обсуждается выше, совокупность значений режима выполнения может содержать, не ограничиваясь, 8-разрядный режим, 16-разрядный режим, 32-разрядный режим, 48-разрядный режим и 64-разрядный режим. В одном из вариантов компонент EMGC 105 выделяет значения текущего режима выполнения из сигнала от модуля 102 планирования и выполнения. В других вариантах компонент EMGC 105 принимает значения текущего режима выполнения от модуля 102 планирования и исполнения по запросу. В следующих вариантах компонент EMGC 105 автоматически принимает значения текущего режима выполнения от модуля 102 планирования и выполнения.

Указанный IT-модуль 103 может также содержать компонент 107 счетчика периодических моментов синхронизации, соединенный с компонентом EMGC 105. Этот компонент 107 счетчика периодических моментов синхронизации передает компоненту EMGC 105 командный сигнал для записи ЕМ-пакета, в качестве периодического обновления состояния режима, в поток выходных IT-пакетов 115. Как обсуждается выше, ЕМ-пакет несет информацию о текущем режиме выполнения в процессоре, включая индикацию любых изменений режима выполнения в процессоре. В одном из вариантов компонент EMGC реализован в виде последовательности выполняемых команд или микроопераций (также называемых μops), которые выполняет машина для генерации ЕМ-пакетов.

В одном из вариантов ЕМ-пакет содержит двухбитовую структуру из журнала пакетов, которая указывает текущий режим выполнения в процессоре для IT-пакетов 115. Варианты настоящего изобретения двухбитовыми структурами не ограничиваются, так что ЕМ-пакет может содержать структуры, имеющие больше двух битов или меньше двух битов в зависимости от конкретного варианта архитектуры. В одном из вариантов такая двухбитовая структура может отражать величины архитектурных битов. Например, когда величины обоих битов в двухбитовой структуре равны нулю, это может обозначать значение режима выполнения, соответствующее 16-разрядному режиму. В другом примере, когда один бит в двухбитовой структуре равен нулю, а другой бит равен единице, это может обозначать значение режима выполнения, соответствующее 32-разрядному режиму или 64-разрядному режиму в зависимости от архитектуры процессорного устройства.

Например, компонент EMGC 105 может принять индикацию 16-разрядного режима в качестве значения текущего режима выполнения от модуля 102 планирования и выполнения и позднее этот компонент может принять индикацию 32-разрядного режима в качестве значения текущего режима выполнения от этого модуля 102 планирования и выполнения. После приема индикации 32-разрядного режима компонент EMGC 105 распознает изменение значения текущего режима выполнения и генерирует ЕМ-пакет, которые задает момент изменения значения режима выполнения для ассоциированного IT-пакета 115.

Указанный IT-модуль 103 может также содержать компонент 109 конфигурации, соединенный с компонентом EMGC 105. Этот компонент 109 конфигурации позволяет программе конфигурировать частоту периодических моментов синхронизации под управлением компонента 107 счетчика периодических моментов синхронизации и может также позволить программе конфигурировать включение/исключение конкретных ЕМ-пакетов в IT-пакетах 115.

Компонент EMGC 105 генерирует также пакет указателя команд режима выполнения (EMIP), ассоциированный с ЕМ-пакетом в составе IT-пакетов 115. В одном из вариантов EMIP-пакет следует за ассоциированным с ним ЕМ-пакетом. Этот EMIP-пакет содержит указатель IP для первой команды, выполняемой в измененном режиме выполнения.

Используя принимаемые ЕМ-пакеты и EMIP-пакеты, декодер может знать, когда изменяется режим выполнения для команды в трассе. Кроме того, декодер может точно знать, в каком месте двоичного кода происходит изменение режима, чтобы правильно дизассемблировать байты команды. В результате поток команд в трассе совпадает с потоком выполнения в процессоре.

В одном из вариантов декодер может пытаться узнать, какой был режим выполнения в начале трассировки, т.е. до первого изменения режима выполнения. Компонент EMGC 105 передает ЕМ-пакет в последовательности пакетов состояния. Эти пакеты состояния передают информацию о текущем состоянии процессорного устройства. В таком ситуации информацию о текущем режиме выполнения в ЕМ-пакете передают пакеты состояния. Поскольку декодер начинает декодирование с пакета состояния, он точно декодирует пакеты состояния в начале трассы. Введение последовательности пакетов состояния в периодические точки в выходном журнале создает дополнительные моменты, когда декодер может начать декодирование.

В одном из вариантов последовательность IT-пакетов 115 в журнале пакетов в выходном потоке, может содержать, не ограничиваясь, граничный пакет, после чего следуют разнообразные пакеты состояния, среди которых могут быть ЕМ-пакет и EMIP-пакет, и далее - конечный пакет состояния. Эта последовательность может повторяться в другой точке в журнале пакетов в выходном потоке. За граничным пакетом в журнале пакетов следует первый байт другого пакета, так что этот байт служит стартовой точкой декодирования пакетов. В одном из вариантов конечный пакет состояния служит индикатором конца последовательности пакетов состояния. Пакет вне области пакетов, ограниченной с одной стороны граничным пакетом и с другой стороны конечным пакетом состояния, являются пакетами событий, которые вставляют в выходной журнал в точке изменения режима.

Фиг. 1В иллюстрирует таблицу IT-пакетов 115, генерируемых IT-модулем 103, когда трассировка активизирована, в ходе потока 116 выполнения, например. Как показано, пока процессор выполняет программную последовательность, в журнал пакетов вводят IT-пакеты 115, генерируемые IT-модулем 103. В качестве примера, совокупность IT-пакетов 115 содержит граничный пакет 120, за который следуют пакеты 121 состояния и следующий за ними ЕМ-пакет 122, имеющий 32-разрядный режим выполнения. В такой ситуации трассировка активизирована в 32-разрядном режиме. За ЕМ-пакетом 122 следует EMIP-пакет 123, которые предоставляет указатель IT 32-разрядного режима выполнения в выходной журнал. За EMIP-пакетом 123 следует другая группа пакетов 124 состояния, за которыми следует конечный пакет 125 состояния.

В этом примере посреди потока управления может произойти изменение режима выполнения в потоке 116 выполнения. Это изменение в режиме выполнения представлено в совокупности пакетов 126 событий в выходном журнале пакетов 115, что вызывает генерацию другого ЕМ-пакета 127 с измененным режимом выполнения в выходном журнале пакетов 115. В приведенном примере, в потоке выполнения происходит изменение режима выполнения от 32-разрядного режима к 64-разрядному режиму. Кроме того, указатель IP этого изменения режима выполнения представлен в выходном журнале посредством EMIP-пакета 128, который следует сразу же после ЕМ-пакета 127. За EMIP-пакетом 128 следует группа пакетов 129 событий.

В одном из примеров в потоке 116 выполнения создана периодическая точка синхронизации, генерирующая другой граничный пакет 130, за которым следует группа пакетов 131 состояния, и после этого пакета следует ЕМ-пакет, имеющий 64-разрядный режим выполнения. В такой ситуации активизирована трассировка в 64-разрядном режиме. За ЕМ-пакетом 132 следует EMIP-пакет 133, представляющий указатель IP 64-разрядного режима выполнения в выходном журнале. За этим EMIP-пакетом следует другая группа пакетом 134 состояния, за которой следует конечный 135 пакет состояния.

Возвращаясь к Фиг. 1А, как обсуждается выше, IT-модуль 103 принимает информацию от модуля 102 планирования и управления и пакетирует эту информацию для передачи на выход IT-пакетов 115. В одном из вариантов эта информация содержит указание состояния транзакции в процессоре. Такое ТМХ-состояние может, не ограничиваясь, представлять собой «Начало транзакции», «Завершение (фиксация) транзакции» и «Отбрасывание транзакции». Указанный IT-модуль 103 может содержать компонент 111 генератора памяти транзакции (transactional memory generation component (TMXGC)), который принимает указание ТМХ-состояния от модуля 102 планирования и выполнения. В одном из вариантов компонент TMXGC 111 выделяет информацию о ТМХ-состоянии из сигнала от модуля 102 планирования и выполнения. В другом варианте компонент TMXGC 111 принимает информацию о ТМХ-состоянии от модуля 102 планирования и выполнения по запросу. В следующих вариантах компонент TMXGC 111 автоматически получает информацию о ТМХ-состоянии от модуля 102 планирования и выполнения.

Компонент 107 счетчика периодических моментов синхронизации в составе IT-модуля 103 также связан с компонентом TMXGC 111, который в свою очередь генерирует пакеты памяти транзакций (ТМХ) для вставки в совокупность пакетов состояния, генерируемых в периодические моменты синхронизации в совокупности IT-пакетов 115. Этот компонент 107 счетчика периодических моментов синхронизации передает командный сигнал компоненту TMXGC 111 для генерации ТМХ-пакетов в качестве части периодических пакетов состояния, записываемых в потоке выходных IT-пакетов. В одном из вариантов компонент TMXGC реализован в виде последовательности выполняемых команд или микроопераций (также называемых μops), которые выполняет машина для генерации ТМХ-пакетов. Как обсуждается выше, ТМХ-пакет представляет собой двухбитовую структуру указания режима в журнале пакетов. Эта двухбитовая структура указания режима может обозначать момент изменения ТМХ-состояния для IT-пакета 115. Варианты настоящего изобретения не ограничиваются двухбитовой структурой указания режима, так что ТМХ-пакет может содержать структуры, имеющие больше двух битов или меньше двух битов в зависимости от используемого варианта архитектуры.

Компонент 109 конфигурации в составе IT-модуля также связан с компонентом TMXGC 111. Этот компонент 109 конфигурации позволяет программе конфигурировать частоту периодических моментов синхронизации, которой управляет компонент 107 счетчика периодических моментов синхронизации, и может также позволить программе конфигурировать включение/исключение конкретных ТМХ-пакетов в совокупность IT-пакетов 115.

В одном из вариантов двухбитовая структура указания режима в ТМХ-пакете содержит бит индикации режима InTX и бит индикации режима TXAbort. Бит режима InTX обозначает, что процессор выполняет транзакцию и, следовательно, изменение этого бита обозначает начало или конец ТМХ-операции. В одном из примеров бит режима InTX может быть установлен (например, сделан равным 1), когда ТМХ-операция начинается, и сброшен или очищен (например, сделан равным 0), когда эта ТМХ-операция завершена (зафиксирована) или отброшена. Бит режима TXAbort предоставляет IT-декодеру извещение, соответствующая ТМХ-операция была отброшена. Это извещение об отбрасывании информирует IT-декодер, что все пакеты между моментом установления бита режима InTX и моментом установления бита режима TXAbort представляют команды, которые не зафиксировали свое состояние. В одном из вариантов IT-декодер отбрасывает все команды, ассоциированные с этими пакетами. В одном из вариантов декодер маркирует эти пакеты, чтобы позднее использовать команды, ассоциированные с этими пакетами. В одном из примеров бит режима TXAbort может быть установлен (например, сделан равным 1), когда бит режима InTX изменяется от 1 к 0 в момент отбрасывания.

В одном из примеров, когда процессор выполняет ТМХ-команду «Начало транзакции», компонент TMXGC 111 генерирует ТМХ-пакет, в котором бит режима InTX установлен равным 1, а бит режима TXAbort установлен равным 0, что обозначает начало транзакции, т.е. ТМХВ. В другом примере, когда процессор выполняет ТМХ-команду «Завершение (фиксация) транзакции», компонент TMXGC 111 генерирует ТМХ-пакет, в котором бит режима InTX установлен равным 0 и бит режима TXAbort установлен равным 0, что указывает на завершение (фиксацию) транзакции, т.е. ТМХС. В следующем пример, когда компонент TMXGC 111 принимает индикацию отбрасывания транзакции, этот компонент TMXGC 111 генерирует ТМХ-пакет, в котором бит режима InTX установлен равным 0, а бит режима TXAbort установлен равным 1, что обозначает отбрасывание транзакции, т.е. ТМХА.

В одном из вариантов компонент TMGC 111 также генерирует пакет указателя исходной команды памяти транзакции (source transactional memory instruction pointer (STMXIP)) и или пакет указателя целевой команды транзакции (target transactional memory instruction pointer (TTMXIP)), ассоциированные с каждым ТМХ-пакетом в совокупности IT-пакетов 115. Указанный STMXIP-пакет предоставляет указатель IP команды, ассоциированной с изменением ТМХ-состояния. В одном из вариантов STMXIP-пакет генерируют вместе с ТМХВ-пакетом для предоставления указателя IP ассоциированной команды в начале ТМХ-операции. В другом варианте STMXIP-пакет генерируют вместе с ТМХА-пакетом для предоставления указателя IP ассоциированной команды при отбрасывании ТМХ-операции. В следующем варианте STMXIP-пакет генерируют вместе с ТМХС-пакетом для предоставления указателя IP ассоциированной команды при завершении (фиксации) ТМХ-операции.

Указанный TTMXIP-пакет предоставляет указатель IP следующей команды, которую нужно выполнить при отбрасывании ТМХ-операции, что требуется, если операция отбрасывания вызывает переход потока управления. В таком случае декодер может знать, где начинается ТМХ-операция, где эта операция отбрасывается, где она завершается (фиксируется) и откуда продолжается выполнение после какого-либо отбрасывания. В одном из вариантов декодер может отбрасывать байты команд для всех пакетов между началом ТМХ-операции и моментом отбрасывания ТМХ-операции. В другом варианте декодер может маркировать байты команд для всех пакетов между началом ТМХ-операции и отбрасыванием этой ТМХ-операции.

Как обсуждается выше, декодер начинает декодирование с пакетов состояния, так что эти пакеты состояния предоставляют информацию о текущем состоянии процессорного устройства. Компонент TMXGC 111 передает ТМХ-пакет в последовательности пакетов состояния. За граничным пакетом в журнале пакетов всегда следует первый байт какого-либо пакета, так что этот байт служит стартовой точкой декодирования пакетов. В такой ситуации IT-декодер может искать этот граничный пакет и точно декодировать пакеты состояния после граничного пакета. Благодаря вставке ТМХ-пакета среди пакетов состояния, следующих сразу же после граничного пакета, декодеру обеспечено знание состояния транзакции от стартовой точки декодирования.

Фиг. 1С иллюстрирует таблицу примеров IT-пакетов 115, генерируемых IT-модулем 103, когда активизирована трассировка в процессе потока 118 выполнения, например. Как показано, когда трассировка активизирована во время выполнения последовательности 118 команд компонент TMGC 111 генерирует журнал пакетов на основе IT-пакетов 115. Совокупность IT-пакетов 115 содержит граничный пакет 140, за которым следует группа пакетов 141 состояния, и за ними следует ТМХ-пакет 142. Этот ТМХ-пакет 142 может содержать описанную выше двухбитовую структуру указания режима, которая содержит бит режима InTX и бит режима TXAbort. Бит режима InTX предоставляет декодеру извещение о начале ТМХ-операции, а бит режима TXAbort предоставляет извещение, что ТМХ-операция отброшена. В этом примере двухбитовая структура указания режима в составе ТМХ-пакетов 142 содержит бит режима InTX, установленный равным 0, и бит режима TXAbort, установленный равным 0. В таком случае поток 118 выполнения не находится в транзакции. Пакет 143 указателя исходной команды памяти транзакций (STMXIP) генерируют после ТМХ-пакета 142. Указанный STMXIP-пакет 143 предоставляет указатель IP ассоциированной команды из состава ТМХ-операции. В одном из вариантов STMXIP-пакет 143 может быть сформирован перед ТМХ-пакетом 142. За этим STMXIP-пакетом 143 следует группа пакетов 144 состояния и конечный 145 пакет состояния.

В одном из примеров посреди потока управления начинается ТМХ-операция в потоке 118 выполнения. Начало этой ТМХ-операции представлено группой пакетов 146 событий в выходном журнале пакетов 115, которые вызывают генерацию пакета начала транзакции ТМХ (ТМХВ) 147 в качестве ТМХ-пакета в начале ТМХ-операции. Этот ТМХВ-пакет 147 может представлять собой описанную выше двухбитовую структуру указания режима, которая содержит бит режима InTX и бит режима TXAbort. Бит режима InTX предоставляет декодеру извещение о начале ТМХ-операции, а бит режима TXAbort предоставляет извещение, что ТМХ-операция отброшена. Например, когда ТМХВ-пакет 147 указывает появление ТМХ-команды «Начало транзакции», двухбитовая структура указания режима в составе ТМХВ-пакета 147 может содержать бит режима InTX, установленный равным 1, и бит режима TXAbort, установленный равным 0. После ТМХВ-пакета 147 генерируют первый пакет указателя исходной команды памяти транзакций (STMXIP) 148. Этот первый STMXIP-пакет 148 предоставляет указатель IP ассоциированной команды в начале ТМХ-операции. В одном из вариантов первый STMXIP-пакет 148 может быть сформирован прежде ТМХВ-пакета 147.

В одном из примеров ТМХ-операция отбрасывает поток выполнения, что представлено ТМХ-пакетом 150 отбрасывания (ТМХА) в качестве ТМХ-пакета. Этот ТМХА-пакет 150 может также следовать за двухбитовой структурой указания режима, описанной выше. Например, когда ТМХА-пакет 150 указывает появление отбрасывания транзакции, тогда двухбитовая структура указания режима в составе ТМХА-пакета 150 может содержать бит режима InTX, установленный равным 0, и бит режима TXAbort, установленный равным 1. Второй STMXIP-пакет 151 генерируют после ТМХА-пакета 150. Этот второй STMXIP-пакет 151 предоставляет указатель IP ассоциированной команды, которая должна быть выполнена при отбрасывании ТМХ-операции. В одном из вариантов второй STMXIP-пакет 151 может быть сформирован перед ТМХА-пакетом 150. За вторым STMXIP-пакетом 151 следует пакет 152 указателя целевой команды памяти транзакций (TTMXIP), который предоставляет указатель IP следующей команды, которая должна быть выполнена после отбрасывания ТМХ-операции. В одном из вариантов TTMXIP-пакет 152 генерируют перед ТМХА-пакетом 150. За TTMXIP-пакетом 152 может следовать другая группа пакетов 153 событий.

В этом примере в потоке 118 выполнения создают периодическую точку синхронизации, генерирующую другой граничный пакет 154, за которым следует группа пакетов 155 состояния, после чего следует другой ТМХ-пакет 156. Аналогично описанному выше, двухбитовая структура указания режима в составе ТМХ-пакета 156 содержит бит режима InTX, установленный равным 0, и бит режима TXAbort, установленный равным 0. Другой STMXIP-пакет 157 генерируют после ТМХ-пакета 156. В одном из вариантов этот STMXIP-пакет 157 может быть сформирован прежде ТМХ-пакета 156. За этим STMXIP-пакетом 157 следует другая группа пакетов 158 состояния и конечный пакет 159 состояния.

Хотя это и не показано, результатом ТМХ-команд может быть также завершение (фиксация) ТМХ-операции, куда входит также генерация пакета завершения (фиксации) ТМХ-операции (ТМХС). При использовании двухбитовой структуры указания режима этот ТМХС-пакет содержать бит режима InTX, установленный равным 0, и бит режима TXAbort, установленный равным 0.

Возвращаясь к Фиг. 1А, в одном из вариантов пользователь может пожелать трассировать команды, выполняемые в конкретном диапазоне указателей IP. В этом сценарии компонент TMXGC 111 может генерировать и передавать на выход ТМХ-пакеты на основе команд, которые как попадают в конкретный диапазон указателей IP, так и находятся вне этого диапазона указателей IP. Однако компонент TMXGC 111 не должен генерировать и передавать на выход STMXIP-пакет и TTMXIP-пакет, ассоциированные с ТМХ-пакетом, если указатель IP находится вне указанного конкретного диапазона указателей IP. В результате декодер имеет возможность должным образом обрабатывать пакеты, генерируемые либо ТМХ-операциями, начинающимися в этой области указателей IP, но заканчивающимися вне этой области указателей IP, либо ТМХ-операциями, начинающимися вне указанной области указателей IP, но заканчивающимися в этой области указателей IP.

Фиг. 2А представляет блок-схему, иллюстрирующую