Высокопроизводительная вычислительная платформа на базе процессоров с разнородной архитектурой

Иллюстрации

Показать всеИзобретение относится к вычислительным комплексам и может быть использовано для параллельной обработки больших объемов информации от специальных систем в режиме реального времени. Технический результат заключается в повышении надежности системы при формировании вычислительных задач и повышении эффективности при их выполнении на центральном компьютере. Указанный результат достигается за счет применения вычислительной платформы на базе процессоров с разнородной архитектурой, содержащей установочный блок высотой 4U, предназначенный для установки в телекоммуникационную стойку и выполненный в виде корпуса, разделенного на две секции. В одной из секций смонтирована система питания, а во второй - размещена объединительная плата со слотами, для размещения в них помещаемых через указанный проем модуля коммутации и вычислительных модулей на базе разнородных процессоров, объединенными через высокоскоростную шину стандарта CompactPCI Serial для образования многопроцессорной конфигурации. Система охлаждения корпуса в зоне каждого слота содержит теплосъемные кассеты для отвода тепла от модуля коммутации и вычислительных модулей на корпус установочного блока, который выполнен с дополнительным корпусом или кожухом, охватывающим разделенный на две секции корпус. 7 з.п. ф-лы, 5 ил.

Реферат

Изобретение относится к вычислительным комплексам и может быть использовано для параллельной обработки больших объемов информации от специальных систем в режиме реального времени. Изобретение может быть применено в различных областях техники, где требуется обеспечить высокую вычислительную производительность, используя возможности одновременного задействования модулей с разной архитектурой для решения общей прикладной задачи.

Известен патент US 9037833, G06F 15/80, G06F 9/50, опубл. 19.05.2015 г. (ЕР 1814029, US 20050235092), в котором высокопроизводительная вычислительная система имеет множество объединенных узлов для выполнения общей задачи. Узел состоит из системной платы, включающей, по крайней мере, два процессора для выполнения высокопроизводительных вычислений и интегрированный коммутатор, имеющий восемь и больше портов, и предназначенный для связи узлов вычислительной системы между собой. Процессоры попарно соединены между собой посредством интерфейса Hyper Transport. Каждый из процессоров на системной плате через HYPERTRANSPORT™/PCI-MOCT соединен с НСА-адаптером (Host Channel Adapter), который, в свою очередь, связан с коммутатором. Интерфейс HYPERTRANSPORT™ может иметь пропускную способность 6.4 Гбайт/с, 12.8 Гбайт/с или больше в зависимости от того, какая используется шина PCI (PCI или PCI-X). HYPERTRANSPORT™ с PCI-Express и НСА может создать полнодуплексный канал ввода/вывода для каждого процессора, работающий со скоростью 2 Гбайт/с.

В системе могут использоваться узлы с различным конструктивным исполнением, которые могут включать интерфейс InfiniBand, а также нестандартные интерфейсы, реализуемые через дополнительно устанавливаемую дочернюю плату с FPGA (Field Programmable Gate Array) модулями.

Узлы высокопроизводительной системы связаны между собой в сеть по одной из следующих топологий: 3D-Тор, гиперкуб, ячеистая (mesh) топология. Для управления работой вычислительной системы в кластере один узел является управляющим, в его задачи входит мониторинг состояния системы (обнаружение неисправных узлов), планирование задач между узлами кластера, управление правами доступа пользователей. Между управляющим узлом и вычислительными узлами системы может использоваться коммуникационная сеть Gigabit Ethernet или 10 Gigabit Ethernet.

Известен патент США №8433816, G06F 15/16, G06F 15/173, G06F 9/02, опубл. 30.04.2013 г., в котором описана сетевая топология для масштабирования многопроцессорных систем, позволяющая объединять локальные процессорные узлы в сеть с минимальными нарушениями первоначальной организации вычислительной системы.

Топология позволяет объединять в сеть локальные процессорные узлы, где каждый локальный узел включает, по меньшей мере, один процессор и память. В основе представленной топологии масштабирования вычислительных систем лежит принцип использования маршрутизаторов первого уровня, объединяющих локальные узлы в небольшие кластеры и использование метамаршрутизаторов для объединения кластеров в сеть. Комплект маршрутизаторов первого уровня в масштабируемой коммуникационной сети передает данные между множеством локальных процессорных узлов, образуя своего рода локальный кластер. Метамаршрутизаторы, согласно данной топологии, позволяют в масштабируемой коммуникационной сети обмениваться данными между комплектом маршрутизаторов первого уровня, так что каждый из маршрутизаторов в первом кластере соединен со всеми другими кластерами через один или более метамаршрутизаторов.

Для каждого кластера в масштабируемой многопроцессорной системе может применяться топология 2D-гиперкуб или 3D-гиперкуб. Каждый метамаршрутизатор системы имеет 4 или 8 портов для подключения маршрутизаторов. В рассмотренных в патенте конструктивных исполнениях сети локальные процессорные узлы включают 4 процессора. Представленная в патенте топология позволяет создавать масштабируемые вычислительные сети, включающие до 512 процессоров.

Известен патент США №6230252, G06F 13/00, опубл. 08.05.2001 г., в котором заявлена гибридная архитектура гиперкуб/тор, позволяющая объединять локальные процессорные узлы в многопроцессорные системы. Масштабируемые многопроцессорные системы, построенные по гибридной топологии гиперкуб/тор, состоят из локальных процессорных узлов, объединенных физическими каналами связи через маршрутизаторы (роутеры) в n-мерную топологию. Каждый локальный процессорный узел включает в себя два или четыре процессора. Общее количество процессоров в многопроцессорной системе может варьироваться от 128 до 2048.

Маршрутизаторы в системе используются для передачи сообщений между локальными процессорными узлами по каналам связи. Маршрутизаторы способны передавать сообщения в суперкуб-топологиях, где размерность суперкуба может достигать 6 измерений, и, в дальнейшем, способны передавать сообщения в топологии n-мерный тор, одна из размерностей которого имеет основание больше 4, как, например, в топологии тор размерности 4×8×4. Каждый маршрутизатор имеет не менее 8 портов. К двум портам подсоединены локальные процессорные узлы, к шести портам подсоединены физические каналы связи. Каждый маршрутизатор включает также таблицы поиска на каждом порту маршрутизатора для обеспечения направления порта для исходящего из ближайшего маршрутизатора в данном маршруте в систему. Таблицы поиска в каждом порту включают в себя локальную таблицу маршрутизатора, имеющую направления для маршрутизации между локальными процессорными узлами внутри локальной подсети и глобальную таблицу маршрутизатора, имеющую направления для маршрутизации между локальными процессорными узлами в двух подсетях.

Известна полезная модель РФ №90241, G06F 19/00, опубл. 27.12.2009, в которой вычислительная система предназначена для научно-технических расчетов. Эта вычислительная система относится к системам обработки данных, предназначенным для проведения научно-технических расчетов, в том числе суперкомпьютерным системам. Техническим результатом является повышение надежности системы при формировании вычислительных задач и повышение эффективности при их выполнении на центральном компьютере.

Эта вычислительная система состоит из центрального компьютера высокой производительности и компьютеров пользователей, соединенных каналами связи с центральным компьютером, причем центральный компьютер содержит блок памяти вычислительных заданий, блок памяти исходных данных, блок памяти результатов, вычислительный блок, блок передачи данных, блок приема данных, а компьютер пользователя содержит блок ввода данных, блок ввода заданий, блок памяти вычислительных заданий, блок памяти исходных данных, блок формирования вычислительных заданий, блок передачи данных, блок приема данных, блоки памяти результатов и блок отображения результатов. Центральный компьютер дополнительно снабжен блоком вычислительных функций, подключенным к выходу блока памяти вычислительных заданий и к дополнительному входу вычислительного блока, а компьютер пользователя дополнительно снабжен блоком памяти шаблонов вычислительных функций, подключенным к дополнительному входу блока формирования вычислительных заданий.

Известная система позволяет исключить некорректные вычислительные задания за счет формирования вычислительных заданий на базе шаблонов вычислительных функций как перечня связей между вычислительными функциями и свойств этих функций, причем структура и свойства шаблонов вычислительных функций идентичны структуре и свойствам вычислительных функций на центральном компьютере.

Известные системы вычислительных комплексов имеют разветвленную архитектуру, что создает неудобства при проведении комплексных работ повышенной сложности из-за удаленности вычислителей и сложности их связывания. Поскольку на рынке промышленных встраиваемых систем по-прежнему наблюдается быстрый рост, продолжает увеличиваться эффективность, надежность, производительность и качество систем, применяемых в разных приложениях и сегментах этого рынка. Растет и спрос на более современные технологии, которые учитывают новые тенденции, например технологии облачных вычислений и мобильной связи на основе сетей IP/Ethernet с более широкой полосой пропускания.

В качестве наглядного примера такой востребованности можно привести современные системы технического зрения, которые не только позволяют эффективнее организовывать процесс производства, но и осуществлять мониторинг и управление ресурсами наряду со сбором данных и их совместным использованием для проведения тщательного и эффективного анализа. Системы технического зрения применяются в автомобильной промышленности, производстве электроники, в сборочных цехах и медицине, а также в автоматизированном управлении дорожным движением. Эти системы выполняют функции по определению местоположения и распознаванию, осуществляют задачи по измерению и осмотру различных объектов.

Естественным развитием появления сложных вычислительных комплексов стала необходимость ухода от разнесенных серверов и от удаленности их расположения с целью сокращения путей и организации единого процессорного центра или единой вычислительной платформы как единого процессора или набора процессоров. Разрешение этой проблемы стало возможным с выходом на рынок нового стандарта CompactPCI. Аппаратное устройство в стандарте Compact PCI представляет собой шину с компонентами (платами), предназначенную для использования в широком диапазоне приложений, включая телекоммуникации, компьютерную телефонию, контроль в реальном масштабе времени, автоматизацию промышленности, сбор данных (в реальном времени), инструментальное производство, военные системы и т.д. Очевидный приоритет при выборе этой шины - ее использование в качестве высокоскоростного устройства передачи данных в системах с модульным построением и компоновкой, обеспечивающей высокую надежность при наличии неблагоприятных внешних воздействий самого разного плана - от электромагнитных помех до механических ударов, вибрации и влияния агрессивной среды. По сути, стандарт - это и есть технология обеспечения совместимости модулей разных производителей для создания целостной системы. Очень часто успех того или иного нового технического решения основан на поддержке наследственных технологий. Яркий пример - успех х86-архитектуры процессоров, поддерживающей работу написанного ранее программного кода. В семействе CompactPCI новая спецификация CompactPCI Serial предоставляет разработчикам систем широкие возможности по интегрированию наследственных модулей PICMG 2.0, 2.30 и 2.16 в рамках одной системы. Периферийные или прикладные модули CompactPCI 2.30 (PICMG 2.30) используют одинаковые разъемы и полностью совместимы с CompactPCI Serial. Системные контроллеры и периферийные модули 3U можно применять в системах 6U. Спецификация CompactPCI Serial позволяет создавать гибридные системы - такие, в которых периферия базируется как на последовательных интерконнектах, так и на наследственных шинах PCI 32-го или 64-го разряда.

В аппаратном исполнении вычислительная платформа представляет собой установочный блок (крейт, шасси) высотой 4U для установки в стандартную 19-дюймовую телекоммуникационную стойку, как правило, разделенный на две секции. В первой секции расположена система питания, а вторая секция представляет собой бокс с параллельно смонтированными на объединительной плате слотами, объединенными через высокоскоростную шину стандарта CompactPCI Serial. Как правило, первый слот используется для установки модуля коммуникации, а остальные слоты - для размещения съемных процессорных модулей. Для возможности установки модулей по типу кассет в бокс крейта каждый модуль выполнен в виде стандартизированной по размерам и группам контактов платы, на которой монтируется конкретная процессорная система.

С помощью платформы CompactPCI Serial можно, например, создавать системы сначала с одной процессорной платой, а затем параллельно ей устанавливать несколько других, чтобы реализовать новые гибкие и более мощные конфигурации. Эти преимущества полностью реализуются с помощью контактной группы разъема, который позволяет передавать данные с большей плотностью сигнала и поддерживает более высокие частоты передачи в системах с новейшими интерфейсами двухточечной связи, такими как PCI Express, SATA, Ethernet и USB. Эта спецификация позволяет вместо 2-мм соединителя типа Hard-Metric применять соединители с большей плотностью контактов, обеспечивающих передачу сигналов с частотой 12 Гбит/с, а также необходимую экранировку и управление импедансом. В одном новом соединителе имеется от 72 до 96 выводов, а одна плата в формате 3U поддерживает до шести соединителей с общим числом выводов, равным 600 или 184 дифференциальных пар, при реализации разных каналов связи на объединительной плате (US 6166902, US 6185110). ("Крейты", http://www.rtsoft.ru/catalog/int/compactpci/krate/detail/382/).

Говоря о вычислительных устройствах, созданных на базе шины стандарта CompactPCI Serial, можно отметить, что среди них превалируют одноплатные модули на базе самых известных процессоров, включая семейство Intel Pentium с самыми высокими частотами. Компания Motorola (http://www.motorola.com), например, выпускает ряд модулей cPCI, в которых используются процессоры 7410 и Pentium III, предлагая, в частности, такие области их применения, как телекоммуникации, автоматизация промышленности, обработка изображений в медицине.

В настоящее время считается, что наиболее очевидной и неоспоримой областью применения технологии стандарта CompactPCI Serial с самого начала была цифровая телефонная связь, по природе своей имеющая коммутационную структуру и использующая современные методы передачи информации по разнородным каналам. Но если уж говорить о роли шины как самостоятельной магистрали передачи данных на том уровне, где уже не имеет значения, какой источник или приемник скрывается за стандартным интерфейсом и протоколом, то знаменитый простой критерий - произведение количества разрядов на тактовую частоту, рассматриваемый в контексте конструктивного исполнения, доведен в случае применения стандарта CompactPCI Serial до максимально возможного значения.

Из уровня техники известна высокопроизводительная вычислительная система, разработанная компанией Kontron на базе высокоскоростных интерфейсов CompactPCI (ст. "Kontron внедряет поддержку стандартов CPCI-S.0 и CompactPCI Serial Mesh", выложенная 03.04.2013 г. на сайте "DATASHEET.SU" (электротехнический портал) в сети Интернет в режиме он-лайн доступа по адресу: http://datasheet.su/news/2078:2013-04-04).

Разработка компании Kontron на базе шины стандартов CompactPCI Serial (CPCI-S.0) реализована для форм-факторов с размером 3U и поддержкой интерфейсов PCIe, GbE, USB и SATA, CompactPCI Serial Mesh (на базе PICMG 2.20) для форм-факторов с размером 6U и 10-гигабитным (10 GbE) интерфейсом.

Новая архитектура платформы на базе шины CompactPCI обеспечивает прирост производительности для высокопроизводительных схем с огромными пропускными способностями. Под высокопроизводительными схемами понимаются системы, где используется 3U-модули с системной шиной CompactPCI: от многопроцессорных систем для вычислений и сложной обработки изображения до высокопроизводительных систем записи видео и данных радаров посредством гибких SATA/RAID-архитектур, от беспроводного телекоммуникационного оборудования с большой пропускной способностью и параллельно-работающими радиомодулями WLAN, UMTS, LTE до мощных многомониторных систем в комнатах управления.

Kontron представляет пять 3U- и одну 6U-плату, а также все соответствующие платформы. Для 3U-платы с шиной CompactPCI Kontron запустил процессорную плату CPS3003-SA с процессорами 3-го поколения Intel Core i7, жестким диском CPS3101, внешним микроконтроллером ХМС CPS3105, а также сетевыми картами CPS3402 с двумя интерфейсами 10GbE и CPS3410 с четырьмя интерфейсами 1GbE. Новые продукты для 6U систем с шиной CompactPCI Serial Mesh: процессорная плата CP6004X-SA с процессором Intel Core i7 3-го поколения и шасси CP-RAPID3 с полноценным интерфейсом 10GbE и PCIe.

О разработке продукции на базе спецификаций CompactPCI 2.30 и CompactPCI Serial объявили многие компании. По состоянию на начало 2012 года это Schroff и Elma (кросс-платы и шасси), MEN Micro, FASTWEL, ADLINK (системные контроллеры и периферийные модули).

В настоящее время особое внимание направлено на создание отечественных образцов вычислительной техники, не уступающих по характеристикам зарубежным аналогам. При этом фундаментальными требованиями к аппаратным и программным средствам в таких случаях являются применение изделий отечественного производства, отвечающих тенденциям развития мировой электронной компонентной базы, обеспечение повышенной надежности при приемлемых затратах. Однако современное состояние отечественной радиоэлектронной отрасли позволяет говорить о том, что вычислительная компонентная база по ряду параметров (производительность, стоимость, выход годных изделий) все еще уступает своим зарубежным аналогам, а по ряду позиций аналоги вовсе отсутствуют. В связи с этим разработчикам вычислительной техники в борьбе за конкурентоспособность создаваемых образцов приходится использовать импортные компоненты.

Так, компания "ДОЛОМАНТ" разработала на базе шины стандарт CompactPCI Serial высокопроизводительную гетерогенную вычислительную платформу «ГРИФОН», предназначенную для решения задач обработки сигналов, потокового видео, трафика сетей связи, СУБД РВ и иных приложений с высокими требованиями к вычислительной мощности и большими объемами анализируемой информации с возможностью организации параллельно-конвейерных вычислений в реальном времени. Позволяет создавать высокопроизводительные БИУС, в т.ч. многоканальные системы обработки видео на подвижных средствах ВТ. «ГРИФОН» построен на основе стандарта CompactPCI® Serial и сконфигурирован в крейте с кассетным размещением процессорных модулей, имеет модульную структуру и состоит из слотовых блоков 3U на 9 посадочных мест. «ГРИФОН» позволяет создавать конфигурации с одновременным использованием вычислителей различной архитектуры, включая х86, GPU NVIDIA, FPGA (ПЛИС), GPU AMD, FPGA, с возможностью межмодульного взаимодействия каждый с каждым (ст. "ГРИФОН - конфигурируемая платформа БИУС", выложенная в 2015 г. на сайте компании "ДОЛОМАНТ" в сети Интернет в режиме он-лайн доступа по адресу: http://www.dolomant.ru/services/development/506722/506773/). Данное решение принято в качестве прототипа.

Особенностью построения высокопроизводительной гетерогенной вычислительной платформы «ГРИФОН" является использование стандартного по конструкции крейта, разделенного на две секции, в одном из которых организована система питания (установлен модуль источника питания PS510RC, возможна установка двух источников питания для организации резервирования), а другая выполнена в виде бокса со слотами для размещения стандартизированных по контактным группам и размерам съемных процессорных модулей. Слоты смонтированы на объединительной плате с использованием коммуникационной шины стандарта CompactPCI Serial, что обеспечивает широкие возможности выбора конфигурации: произвольное количество вычислительных модулей разных архитектур, возможность построения единой системы на базе нескольких блоков, соединенных оптическими линиями связи.

В первом слоте размещен модуль KIC551RC (модуль коммутатора PCIe и GbEthernet) - коммутационный, а в остальных слотах могут быть размещены в требуемом сочетании KIC552RC (модуль интерфейсный оптический PCIe), и/или CPC510RC (модуль процессора х86), и/или CPC512RC (модуль процессора х86), и/или VIM556RC (модуль графического процессора NVIDIA/AMD), и/или VIM554RC (модуль видеоввода), и/или DIC551RC (модуль ввода/вывода), и/или KIC550RC (носитель диска 2.5'').

Для данной платформы стандарт CompactPCI Serial предоставляет возможности для реализации резервирования. Например, периферийные модули могут быть дублированы или троированы, и замена вышедшего из строя модуля возможна без выключения системы («горячая» замена). Полное внутрисистемное дублирование может быть организовано при синхронизации работы двух сегментов CompactPCI Serial через каналы Ethernet (для систем 3U и 6U) или с участием внутрисистемных коммутаторов (только для 6U). Правда, внутрисистемное полное резервирование в настоящее время используется редко. Существенно чаще применяется распределенное резервирование, которое позволяет повысить работоспособность системы за счет расположения ее элементов в разных местах на объекте с питанием от различных источников и использованием распределенных линий связи.

Каждый процессорный модуль выполнен на отдельной плате, на которой на достаточно большой площади платы размещен плоский радиатор для теплотвода с поверхности процессора (ст. "Стандарт CompactPCI Serial для простой и гибкой реализации двухточечных систем связи с повышенными скоростями обмена данными", МКА: ВКС №1/2014, автор Сандра Корсинек (Sandra Korsinek), компания Kontron, выложенная на сайте "RTSoft" в сети Интернет в режиме он-лайн доступа по адресу: http://www.rtsoft.ru/press/articles/detail.php?ID=2456). Сам корпус крейта выполнен тонкостенным для обеспечения кондуктивного теплоотвода от размещенных в нем модулей, согласно стандарту PICMG CPCI-S.0 R1.0. Спецификация CompactPCI Serial предлагает разработчикам систем простой вариант реализации систем с кондуктивным охлаждением. Он предполагает упаковку стандартной платы в металлическую кассету, которая вставляется в систему с шагом 5HP между модулями. А новые разъемы в слотах и в модулях позволили усовершенствовать систему питания. CompactPCI Serial требует всего одного напряжения питания +12 В с максимальной подводимой мощностью в 79,8 Вт для каждого модуля 3U и 171 Вт для модуля 6U, необходимого для обеспечения питанием высокопроизводительных модулей шириной 8НР или 12НР для питания модулей с кондуктивным охлаждением.

Кондуктивное охлаждение наиболее часто применяется как метод локального охлаждения. Однако в последнее время кондуктивное охлаждение часто используется в блоках с очень высокой плотностью монтажа как способ общего охлаждения. Принцип кондуктивного охлаждения блока или микросхемы заключается в том, что они находятся в хорошем тепловом контакте с металлическими шинами (радиаторами), выполняющими роль теплостоков. При кондуктивном охлаждении теплота переносится теплопроводностью и излучением.

Технология Diamond заключается в разработке одноплатных компьютеров с тем, чтобы элементы с наибольшим тепловыделением (ЦПУ, графическое ядро, системы питания) располагались на нижней части платы, вместо более традиционного расположения их на верхней части платы. Затем на нижней части одноплатного компьютера устанавливается радиатор в виде пластины, где он в том числе служит и в качестве монтажной пластины системы. Такой радиатор эффективно отводит тепло от данных компонентов во внешнюю среду и напрямую на стенку корпуса, без циркуляции воздуха внутри корпуса. Результаты тестов показывают, что данное конструктивное решение способствует снижению температуры ЦПУ и других компонентов в большей степени, чем применение традиционных радиаторов, позволяя использовать устройство при более высокой температуре окружающей среды, одновременно с этим обеспечивая снижение количества отказов по причине перегрева. Результаты проведенных компанией Diamond тестов с одноплатным компьютером Aurora в закрытом корпусе Pandora показали, что использование кондуктивного охлаждения привело к понижению температуры воздуха внутри корпуса на 5°С, а температуры в районе ЦПУ на 23°С (ст. "Технология кондуктивного охлаждения в одноплатных компьютерах компании Diamond Systems", 2014, выложена на сайте "MicroMax" в сети Интернет по адресу: http://www.maxnews.ru/site/htm/mn/14-05/conduction_cooling.html).

Однако такие конструктивные решения разработаны для одноплатных процессорных систем с учетом их расположения в корпусе. Для вычислительных платформ на базе шины стандарта CompactPCI Serial используются до 9 модулей, каждый из которых представляет собой одноплатную процессорную систему. При этом все модули расположены в общем отсеке (секции) с небольшим промежуточным расстоянием между платами. В связи с этим в полости отсека находятся до 9 модулей с кондуктивным отводом тепла в полость отсека. Естественно, что в данной ситуации сами радиаторы на платах передают тепло в пространство отсека (секции), а корпус секции должен отвести это суммарное тепло в окружающую среду. Естественно, что применение только кондуктивного охлаждения за счет использования радиаторов и теплоотводящих материалов для таких крейтов неэффективно ввиду слабого отвода тепла. Для решения этой проблемы применяют либо жидкостное охлаждение, что сложно, увеличивает габариты платформы и требует специальной циркуляционной системы, или вентиляторы в верхней части крейта (US 6456498). Использование вентиляторов оправдано для масштабируемых телекоммуникационных стоек, так как требует пространства, что оказывает влияние на габариты.

Высокопроизводительные платформы на базе шины стандарта CompactPCI Serial строятся на основе соединения с этой шиной разнородных и/или однородных процессоров, которые в силу своей архитектуры каждый и особенностей исполнения имеют свой температурный диапазон нормальной производительности. Перегрев приводит к потере производительности или к выходу процессора из строя. Кроме того, на некоторых процессорах установлены блоки принудительной остановки процессора при переходе через границу критической температуры. Если обратиться к широко используемым в компьютерной технике процессорам, то в спецификации для таких процессоров написано, что в режиме простоя нормальной температурой считается до 45°С, а под нагрузкой до 65°С, температура свыше 70°С считается критической. Например, разные производители процессоров устанавливают свою температуру, но если говорить обобщенно, то температура должна быть в пределах 7-25°С, в пределах 45-60°С считается еще нормальной, максимум 65°С. Критические температуры - это когда процессор греется от 65°С до 78°С (для разных процессоров своя), а при температуре 90°С и выше может сгореть плата, но опять же некоторые производители процессоров, такие как, например, Core Duo, считают 100°С максимальной температурой, но пока еще не критической.

Таким образом, под корпусом крейта могут находиться процессорные модули, для которых температура среды для нормальной работы могут сильно отличаться. Естественно, что в такой многопроцессорной платформе применение только кондуктивного охлаждения не обеспечит нормальную работу платформы. Для таких платформ могут использоваться только системы охлаждения с принудительной циркуляцией охлаждающего агента при соблюдении условия обеспечения температуры внешней среды на заданном уровне (например, на уровне 18-20°С или ниже).

Настоящее изобретение направлено на достижение технического результата, заключающегося в повышении эксплуатационной надежности и долговечности производительного цикла вычислительной платформы, построенной на основе объединения процессорных модулей с разнородной архитектурой на базе шины стандарта CompactPCI Serial, за счет обеспечения кондуктивно-конвективного отвода тепла.

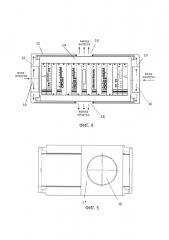

Указанный технический результат достигается тем, что в высокопроизводительной вычислительной платформе на базе процессоров с разнородной архитектурой, содержащей установочный блок высотой 4U, предназначенный для установки в телекоммуникационную стойку и выполненный в виде корпуса, разделенного на две секции, в одной их которых смонтирована система питания, а во второй, выполненной с открытым проемом с одной боковой стороны, размещена объединительная плата со слотами, для размещения в них помещаемых через указанный проем модуля коммутации и вычислительных модулей на базе разнородных процессоров, объединенными через высокоскоростную шину стандарта CompactPCI Serial для образования многопроцессорной конфигурации, а также система охлаждения корпуса, в зоне каждого слота размещены теплосъемные кассеты для отвода тепла от модуля коммутации и вычислительных модулей на корпус установочного блока, который выполнен с дополнительным корпусом или кожухом, охватывающим разделенный на две секции корпус, при этом между стенками разделенного на две секции корпуса и дополнительного корпуса или кожуха образована межстеночная полость, а система охлаждения корпуса включает в себя два центробежных вентилятора, установленные в отдельном кожухе каждый у противоположно расположенных боковых стенок корпуса в межстеночной полости напротив впускных отверстий или технологических окон в стенке дополнительного корпуса или кожуха для формирования идущих навстречу друг другу воздушных потоков, а в других стенках дополнительного корпуса или кожуха выполнены технологические окна для выхода воздуха из межстеночной полости.

Вычислительные модули могут быть выполнены на базе процессоров Эльбрус, Байкал, х86, графических процессоров и на базе программируемых логических интегральных схем (ПЛИС) или процессоров цифровой обработки сигналов (ПЦОС). В корпусе на объединительной плате смонтировано девять слотов, первый из которых является системным для установки модуля коммутации, а остальные слоты предназначены для установки вычислительных модулей в произвольном порядке. Например, в корпусе на объединительной плате смонтировано девять слотов, в первом из которых установлен модуль коммутации, а в остальные слоты установлены четыре вычислительных модуля на базе процессоров х86 и четыре вычислительных модуля на базе графических процессоров. Или в корпусе на объединительной плате смонтировано девять слотов, в первом из которых установлен модуль коммутации, а в остальные слоты установлены один вычислительный модуль на базе процессора "Эльбрус" или "Байкал", два вычислительных модуля на базе процессоров х86, один вычислительный модуль на базе ПЛИС или ПЦОС и один вычислительный модуль на базе графического процессора.

Для межмодульного взаимодействия может использоваться объединительная плата с заведенными линиями последовательной шины PCI Express 3-го поколения в составе двух х8 и шести х4 в реализации 3U, или для межмодульного взаимодействия может быть использован модуль коммутации PCI Express, который позволяет задействовать для коммутации все линии PCI Express на объединительной плате.

А в качестве топологии объединения вычислительных модулей внутри корпуса на физическом уровне может применяться сетевая топология «звезда», а на логическом уровне вычислительные модули связаны между собой в режиме прямого доступа к памяти с поддержкой взаимообмена по принципу «каждый с каждым».

При этом система питания может быть выполнена с источником резервного питания в виде резервируемого блока питания.

Указанные признаки являются существенными и взаимосвязаны между собой с образованием устойчивой совокупности существенных признаков, достаточной для получения требуемого технического результата.

Настоящее изобретение иллюстрируется примерами, которые представлены на следующих чертежах:

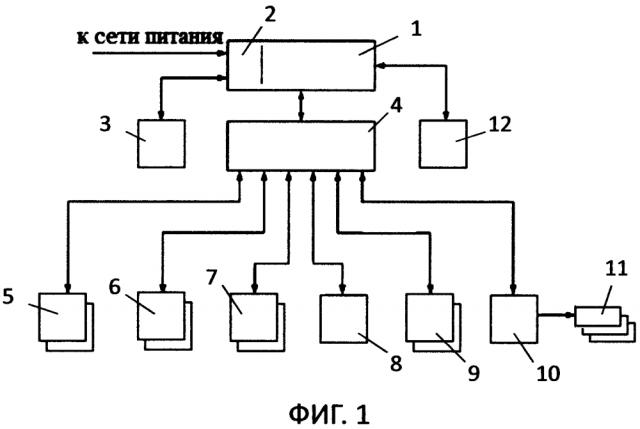

фиг. 1 - структурная схема модульной вычислительной платформы (базовая конфигурация);

фиг. 2 - структурная схема модульной вычислительной платформы (конфигурация на базе модулей процессора х86 и модулей графического процессора);

фиг. 3 - структурная схема модульной вычислительной платформы, ориентированная на использование в режиме совместимости в вычислительных комплексах ответственного назначения;

фиг. 4 - показано изделие в корпусе с гибридным (кондуктивно-конвективным) отводом тепла, вид спереди;

фиг. 5 - то же, что на фиг. 4, вид слева.

Согласно настоящего изобретения рассматривается вычислительный комплекс для параллельной обработки больших объемов информации от специальных систем в режиме реального времени.

Изобретение касается разработки гетерогенных реконфигурируемых вычислительных платформ, в которых в составе одного корпусного блока можно использовать модули с разными архитектурами в различных конфигурациях. В такие вычислительные платформы могут входить микропроцессоры общего назначения (х86, Эльбрус, Байкал), графические процессоры, вычислительные модули на базе программируемых логических интегральных схем (ПЛИС). Создание проблемно-ориентированной конфигурации на базе такой платформы достигается за счет выбора и установки в вычислительную платформу необходимого набора модулей, исходя из максимальной эффективности выполнения алгоритмов. Применение модулей на базе отечественных и зарубежных процессоров в рамках одной вычислительной платформы позволит не только создавать аппаратуру современного уровня уже сейчас, но и стимулирует разработку отечественной элементной базы, аналоги которой на данный момент отсутствуют.

Сущность предлагаемого изобретения заключается в том, что высокопроизводительная вычислительная платформа на базе процессоров с разнородной архитектурой позволяет задействовать вычислительные модули на базе процессоров Эльбрус, Байкал-Т1, Байкал-М, х86, графических процессоров, а также вычислительные модули на базе ПЦОС (процессоры цифровой обработки сигналов), а также вычислительные модули на базе ПЛИС (программируемые логические интегральные схемы), объединяя их через высокоскоростную шину стандарта CompactPCI Serial. Такая платформа позволяет создавать многопроцессорные конфигурации под задачу для эффективного ее решения.

В общем случае, высокопроизводительная вычислительная платформа на базе процессоров с разнородной архитектурой, содержащая установочный блок высотой 4U, предназначенный для установки в телекоммуникационную стойку и выполненный в виде корпуса, разделенного на две секции, в одной их которых смонтирована система питания, а во второй, выполненной с открытым проемом с одной боковой стороны, размещена объединительная плата со слотами, для размещения в них помещаемых через указанный проем модуля коммутации и вычислительных модулей на базе разнородных процессоров, объединенными через высокоскоростную шину стандарта CompactPCI Serial для образования многопроцессорной конфигурации с вычислительными модулями, выполненными на базе процессоров Эльбрус, Байкал, х86, графических процессоров и на базе ПЛИС или ПЦОС. Для этого в корпусе на объединительной плате смонтировано девять слотов, первый из которых является системным для установки модуля коммутации, а остальные слоты предназначены для установки вычислительных модулей в произвольном порядке.

х86 - это архитектура процессора с одноименным набором команд, впервые реализованная в процессорах компании Intel. Широкая известность архитектуры и привычный для разработчиков набор команд, наличие большого числа библиотек и средств программирования позволяют эффективно задействовать потенциал процессоров данной архитектуры для широкого спектра задач.

В архитектуре «Эльбрус» при поступлении потока команд на процессор основную работу по анализу зависимостей и оптимизации порядка выполнения операций осуществляет компилятор, в то время как в суперскалярных процессорах х86 архитектуры определение независимых друг от друга операций, их параллельный запуск или изменение порядка исполнения операций осуществляет процессор. Такой динамический анализ зависимостей и поддержка внеочередного исполнения инструкций позволяет анализировать и запускать на исполнение до 4-х команд за такт, в то время как в процессорах «Эльбрус» за счет более тщательного анализа исходного кода компилятором количество независимых операций, которые могут быть выполнены за 1 такт, может быть больше. Поэтому в архитектуре Эльбрус больше параллельно работающих исполнительных устройств и в ряде случаев такие архитектурные особенности дают существенный прирост скорости при выполнении программ. Другой особенностью процессоров «Эльбрус» является реализация защищенного режима исполнения программ, заключающаяся в работе программ только с инициализированными данными и аппаратной проверке обращений в память на принадлежность к допустимому диапазону адресов. Вычислительные модули на базе отечественных процессоров «Эльбрус» позволяют создавать конфигурации вычислительных систем, где требуется обеспечить высокую производительность на вычислениях с действительными числами (системы обработки изображений, суперкомпьютеры, радиолокационные и гидроакустические системы), а также в системах, к которым предъявляются повышенные требования информационной безопасности (информационные системы государственных структур, военные и другие системы ответственного назначения).

В архитектуре ARM, на базе которой создае