Генератор случайной последовательности

Иллюстрации

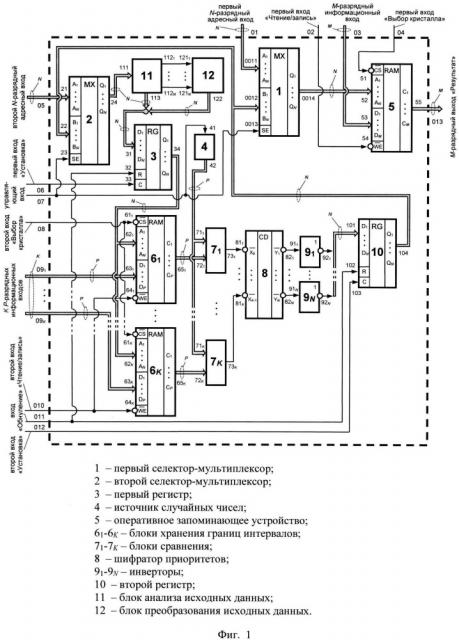

Показать всеИзобретение относится к вычислительной технике и предназначено для генерации случайной последовательности значений из заданного множества значений с требуемыми характеристиками генерируемой последовательности. Технический результат заключается в повышении достоверности генерируемой последовательности. Генератор случайной последовательности содержит первый селектор-мультиплексор 1, второй селектор-мультиплексор 2, первый регистр 3, источник случайных чисел 4, оперативное запоминающее устройство 5, K≥2 блоков хранения границ интервалов 61-6K, K блоков сравнения 71-7K, шифратор приоритетов 8, N≥1 инверторов 91-9N, второй регистр 10, блок анализа исходных данных 11, блок преобразования исходных данных 12. 2 з.п. ф-лы, 4 ил.

Реферат

Изобретение относится к вычислительной технике и предназначено для генерации случайной последовательности значений из заданного множества значений с требуемыми характеристиками генерируемой последовательности.

Известен генератор случайной последовательности по патенту РФ №2250489 «Генератор случайной последовательности» МПК G06F 7/58, H0K 3/84 опубликованный 20.04.2005 бюл. №11, включающий источник случайных чисел, N-разрядный селектор-мультиплексор, оперативное запоминающее устройство, блок контроля интервалов, блок контроля количества генераций, J-входовый элемент ИЛИ, блок элементов И. Этот аналог обеспечивает формирование конечной последовательности заданных значений набора данных по заданному в интервальном виде закону распределения со случайной частостью появления значений в пределах интервалов.

Недостатком данного устройства является формирование ограниченной последовательности заданных значений набора данных, что обусловлено реализованным в устройстве подходе к заданию закона распределения, который предполагает указание абсолютных значений требуемого числа наблюдений элементов заданного набора данных на выходе устройства для каждого из интервалов.

Известен генератор случайной последовательности по патенту РФ №2313125 «Генератор случайной последовательности» МПК G06F 7/58, H03K 3/84, G07C 15/00 опубликованный 20.12.2007, бюл. №35. Это устройство содержит источник случайных чисел, оперативное запоминающее устройство, N-разрядный селектор-мультиплексор, K P-разрядных регистров, K блоков сравнения, шифратор приоритетов, N инверторов. Устройство обеспечивает формирование неограниченной последовательности заданных значений набора данных, частность появления которых определяется только заданным законом распределения.

Однако данное устройство имеет недостаток - узкую область применения, ограниченную возможностью моделирования дискретных случайных процессов, характеризующихся отсутствием вероятностной связи между состояниями случайного процесса (между генерируемыми значениями заданного набора данных), отсутствием вероятностной зависимости каждого очередного состояния случайного процесса от предыдущего.

Из известных наиболее близким аналогом (прототипом), по своей технической сущности, заявленному устройству является генератор случайной последовательности по Патенту РФ №2542903 «Генератор случайной последовательности» МПК G06F 7/58, G06F 1/02, опубликованный 27.02.2015, Бюл. №6. Устройство-прототип содержит источник случайных чисел, оперативное запоминающее устройство, первый и второй селекторы-мультиплексоры, K блоков хранения границ интервалов, K блоков сравнения, шифратор приоритетов, N инверторов, первый и второй регистр. Устройство-прототип обеспечивает формирование значений элементов случайного процесса, учитывая вероятностные связи между состояниями этого процесса.

Однако прототип имеет недостаток - относительно низкую достоверность генерируемой последовательности заданных значений набора данных в условиях, характерных для случайных процессов, протекающих в реальных системах, в реальной вычислительной технике, когда значения элементов случайного процесса зависят не только от вероятностных, но и от неоднозначных (нечетких) связей между состояниями этого процесса.

Данное устройство позволяет получать текущие вероятностно-временные значения элементов заданного набора данных с учетом наличия вероятностной (заданной количественно) связи каждого очередного значения с предыдущим, в то время как при исследовании многих случайных процессов, протекающих в реальных системах, широкое применение находят модели [1], объективно основанные на качественно (неоднозначно, нечетко) заданных значениях параметров случайного процесса, где связь каждого очередного значения с предыдущим из последовательности генерируемых значений носит не только количественный - вероятностный (однозначно, четко идентифицируемый), но и неоднозначный (идентифицируемый лишь на качественном уровне), нечеткий характер, традиционно описываемый с привлечением лингвистической переменной.

Целью изобретения является разработка устройства, обеспечивающего повышение достоверности генерируемой последовательности за счет обеспечения возможности генерации заданных значений набора данных с учетом наличия не только вероятностной, но и неоднозначной (нечеткой) связи каждого очередного значения с предыдущим, создание генератора случайной последовательности, способного с высокой достоверностью формировать значения элементов случайного процесса, характеризующего реальное поведение сложной вычислительной системы - когда взаимосвязи параметров случайного процесса, взаимосвязи каждого очередного из последовательности генерируемых значений с предыдущим значением имеют как количественно (вероятностно), так и качественно (неоднозначно, нечетко, с привлечением лингвистической переменной) выраженный физический смысл.

Указанная цель достигается тем, что в известный генератор случайной последовательности, содержащий K блоков сравнения, где K≥2 - максимально возможная мощность заданного множества генерируемых значений, первый селектор-мультиплексор, второй селектор-мультиплексор, оперативное запоминающее устройство, шифратор приоритетов, N инверторов, где N=[log2K] - число двоичных разрядов, достаточное для адресации элементов заданного множества генерируемых значений, K блоков хранения границ интервалов, выполненных в виде оперативных запоминающих устройств, первый регистр, второй регистр и источник случайных чисел, дополнительно включены блок анализа исходных данных исходных данных и блок преобразования исходных данных. При этом P-разрядный, где Р>N, выход «Случайное число» источника случайных чисел соединен с P-разрядными входами «Случайное число» K блоков сравнения, P-разрядный выход k-го блока хранения границ интервалов, где k=1, 2, …, K, соединен с P-разрядным входом «Верхняя граница» k-го блока сравнения. Выход «Результат сравнения» k-го блока сравнения соединен с k-м инверсным входом шифратора приоритетов, n-й инверсный выход которого, где n=1, 2 N, соединен с входом n-го инвертора. Вход выбора первого селектора-мультиплексора соединен с управляющим входом источника случайных чисел и является управляющим входом генератора, первый N-разрядный информационный вход первого селектора-мультиплексора является первым N-разрядным адресным входом генератора, N-разрядный выход первого селектора-мультиплексора соединен с N-разрядным адресным входом оперативного запоминающего устройства, инверсные входы «Чтение/запись» и «Выбор кристалла» которого являются соответственно первым входом «Чтение/запись» и первым входом «Выбор кристалла» генератора. Причем М-разрядный выход оперативного запоминающего устройства, где М≥2 - количество разрядов, достаточное для представления максимального значения из числа значений, входящих в состав заданного множества генерируемых значений, является М-разрядным выходом «Результат» генератора, М-разрядный информационный вход оперативного запоминающего устройства является M-разрядным информационным входом генератора. При этом P-разрядный информационный вход k-го блока хранения границ интервалов является k-й P-разрядным информационным входом генератора, n-й разряд N-разрядного информационного входа второго регистра соединен с инверсным выходом n-го инвертора, a N-разрядный выход второго регистра соединен с вторым N-разрядным информационным входом первого селектора-мультиплексора и вторым N-разрядным информационным входом второго селектора-мультиплексора, первый N-разрядный вход которого является вторым N-разрядным адресным входом генератора, а его N-разрядный выход соединен с N-разрядным информационным входом блока анализа исходных данных, N проверочных выходов которого соединены с соответствующими N проверочными входами блока преобразования исходных данных, N-разрядный выход которого и N-разрядный транзитный выход блока анализа исходных данных объединены меду собой и являются N-разрядным информационным входом первого регистра, N-разрядный выход которого соединен с N-разрядными адресными входами каждого из K блоков хранения границ интервалов, соответствующие инверсные входы «Выбор кристалла» и «Чтение/запись» которых объединены между собой и являются соответственно вторым входом «Выбор кристалла» и вторым входом «Чтение/запись» генератора. Вход выбора второго селектора-мультиплексора соединен с управляющим входом источника случайных чисел, входы инициализации первого и второго регистров являются соответственно первым и вторым входом «Установка» генератора, а входы сброса первого и второго регистров объединены и являются входом «Обнуление» генератора.

Блок анализа исходных данных состоит из регистра хранения и счетчика. При этом N-разрядный вход счетчика является N-разрядным информационным входом блока, N выходов счетчика соединены с соответствующими N входами регистра хранения. Причем N-разрядный транзитный выход регистра хранения является N-разрядным транзитным выходом блока, N проверочных выходов регистра хранения являются соответствующими N проверочными выходами блока анализа исходных данных.

Блок преобразования исходных данных, предназначенный для трансформирования исходных данных, заданных в нечеткой форме к виду, пригодному для осуществления процедуры параметрического моделирования (генерирования) случайных процессов, состоит из регистра, элемента расчета дополнения, главного и вспомогательного элементов хранения, главного и вспомогательного анализаторов, элемента расчета объединения и вычислителя. При этом N-разрядный выход вычислителя является N-разрядным выходом блока преобразования исходных данных, N входов регистра являются соответствующими N проверочными входами блока, N первичных выходов регистра подключены к соответствующим N первичным входам элемента расчета дополнения и к соответствующим N входам главного элемента хранения, N вторичных выходов регистра подключены к соответствующим N вторичным входам элемента расчета дополнения и к соответствующим N прямым входам вспомогательного элемента хранения, N выходов главного элемента хранения подключены к соответствующим N основным входам главного анализатора, N выходов вспомогательного элемента хранения подключены к соответствующим N основным входам вспомогательного анализатора, N дополнительных входов главного анализатора подключены к соответствующим N первичным выходам элемента расчета дополнения. Причем N вторичных выходов элемента расчета дополнения соединены с соответствующими N дополнительными входами вспомогательного анализатора, N выходов главного анализатора подключены к соответствующим N первичным входам элемента расчета объединения, N вторичных входов которого соединены с соответствующими N выходами вспомогательного анализатора, N выходов элемента расчета объединения соединены с соответствующими N дополнительными входами элемента расчета дополнения, соответствующими N дополнительными входами вспомогательного элемента хранения и соответствующими N входами вычислителя.

Благодаря новой совокупности существенных признаков за счет введения блока анализа, обеспечивающего последовательное сравнение (по количеству разрядов) поступающих в двоичном коде исходных данных (вида взаимосвязи каждого очередного значения случайного процесса с предыдущим) и принятие решения об их математической природе, а также блока преобразования исходных данных, обеспечивающего трансформирование исходных данных, заданных в нечеткой форме к виду, пригодному для осуществления процедуры параметрического моделирования (генерирования) случайных процессов, в заявленном генераторе случайной последовательности достигается возможность повышения достоверности генерируемой последовательности заданных значений набора данных за счет обеспечения возможности генерации последовательности из заданного множества значений с учетом наличия не только вероятностной, но и неоднозначной (нечеткой) связи каждого очередного значения с предыдущим.

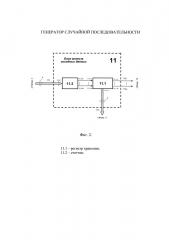

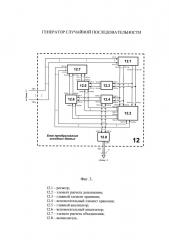

Заявленное устройство поясняется чертежами, на которых:

на фиг. 1 - структурная схема генератор случайной последовательности;

на фиг. 2 - структурная схема блока анализа исходных данных;

на фиг. 3 - структурная схема блока преобразования исходных данных;

на фиг. 4 - структурная схема блока сравнения.

Генератор случайной последовательности (см. фиг. 1) состоит из первого селектора-мультиплексора 1, второго селектора-мультиплексора 2, первого регистра 3, источника случайных чисел 4, оперативного запоминающего устройства 5, K блоков хранения границ интервалов 61-6K, K блоков сравнения 71-7K, шифратора приоритетов 8, N инверторов 91-9N, второго регистра 10, блока анализа исходных данных 11 и блока преобразования исходных данных 12.

Элементы соединены между собой следующим образом (см. фиг. 1). P-разрядный выход «Случайное число» 42 источника случайных чисел 4 соединен с P-разрядными входами «Случайное число» 711-71K K блоков сравнения 71-7K, P-разрядный выход 65k k-го блока хранения границ интервалов 6k, где k=1, 2, …, K, соединен с P-разрядным входом «Верхняя граница» 72k k-го блока сравнения 7k. Выход «Результат сравнения» 73k k-го блока сравнения 7k соединен с k-м инверсным входом 81k шифратора приоритетов 8, n-й инверсный выход 82n которого, где n=1, 2, …, N, соединен с входом 91n n-го инвертора 9n. Вход выбора 0013 (вход SE) первого селектора-мультиплексора 1 соединен с управляющим входом 41 источника случайных чисел 4 и является управляющим входом 07 генератора, первый N-разрядный информационный вход 0011 (вход для разрядов A1-AN) первого селектора-мультиплексора 1 является первым N-разрядным адресным входом 01 генератора, N-разрядный выход 0014 (выход для разрядов Q1-QN) первого селектора-мультиплексора 1 соединен с N-разрядным адресным входом 52 (входом для разрядов A1-AN) оперативного запоминающего устройства 5, инверсные входы «Чтение/запись» 54 (вход ) и «Выбор кристалла» 51 (вход ) которого являются соответственно первым входом «Чтение/запись» 02 и первым входом «Выбор кристалла» 04 генератора. Причем М-разрядный выход 55 (выход для разрядов C1-CM) оперативного запоминающего устройства 5 является М-разрядным выходом «Результат» 013 генератора, М-разрядный информационный вход 53 (вход для разрядов D1-DM) оперативного запоминающего устройства 5 является М-разрядным информационным входом 03 генератора. При этом P-разрядный информационный вход 63k (вход для разрядов D1-DP) k-го блока хранения границ интервалов 6k является k-м P-разрядным информационным входом 09k генератора, n-й разряд N-разрядного информационного входа 101 второго регистра 10 соединен с инверсным выходом 92n n-го инвертора %, а N-разрядный выход 104 второго регистра 10 соединен с вторым N-разрядным информационным входом 0012 (входом для разрядов B1-BN) первого селектора-мультиплексора 1 и вторым N-разрядным информационным входом 22 (входом для разрядов B1-BN) второго селектора-мультиплексора 2, первый N-разрядный вход 21 которого является вторым N-разрядным адресным входом 05 генератора, а его N-разрядный выход 24 соединен с N-разрядным информационным входом 111 блока анализа исходных данных 11, N проверочных выходов 1121-112N которого соединены с соответствующими N проверочными входами 1211-121N блока преобразования исходных данных 12, N-разрядный выход 122 которого и N-разрядный транзитный выход 113 блока анализа исходных данных 11 объединены между собой и являются N-разрядным информационным входом 31 первого регистра 3, N-разрядный выход 34 которого соединен с N-разрядными адресными входами 621-62K K блоков хранения границ интервалов 61-6K, соответствующие инверсные входы «Выбор кристалла» 611-61K (входы ) и «Чтение/запись» 641-64K (входы ) которых объединены между собой и являются соответственно вторым входом «Выбор кристалла» 08 и вторым входом «Чтение/запись» 010 генератора. Вход выбора 23 (вход SE) второго селектора-мультиплексора 2 соединен с управляющим входом 41 источника случайных чисел 4, входы инициализации 33 и 103 (входы С) первого 3 и второго 10 регистров являются соответственно первым 06 и вторым 012 входом «Установка» генератора, а входы сброса 32 и 102 (входы R) первого 3 и второго 10 регистров объединены и являются входом «Обнуление» 011 генератора.

Число «N, (N=[log2K]; N≥1)» (блоков, разрядов, входов, выходов и т.п.) определяется в соответствии с количеством двоичных разрядов, достаточных для адресации элементов заданного множества генерируемых значений случайной последовательности (т.е, для адресации элементов набора данных) и, как правило, составляет от 2 (двух) до 10 (десяти).

Число «K, (K≥2)» характеризует максимально возможную мощность заданного множества генерируемых значений случайной последовательности (т.е., количество элементов в заданном наборе данных) и, как правило, составляет от 2 (двух) до 500 (пятисот).

Число «М, (М≥2)» характеризует количество двоичных разрядов, достаточное для представления максимального значения из числа значений, входящих в состав заданного множества генерируемых значений случайной последовательности (т.е, для представления значений элементов заданного набора данных) и, как правило, составляет от 2 (двух) до 10 (десяти).

Число «Р, (Р>N)» характеризует разрядность информационных входов генератора и определяется в соответствии с количеством, большим, чем количество двоичных разрядов, достаточных для адресации элементов заданного множества генерируемых значений случайной последовательности и, как правило, составляет от 3 (трех) до 11 (одиннадцати).

Блок анализа исходных данных 11, изображенный на фиг. 2, предназначен для осуществления процедуры последовательного сравнения (по количеству разрядов) поступающих в двоичном коде исходных данных (вида взаимосвязи параметров случайного процесса) и принятия решения об их математической природе - взаимосвязь параметров случайного процесса задана параметрически (вероятностно) или с использованием функции принадлежности, характерной для нечетких множеств.

Блок анализа исходных данных 11 (фиг. 2) состоит из регистра хранения 11.1 и счетчика 11.2. При этом N-разрядный вход 11.2-1 счетчика 11.2 является N-разрядным информационным входом 111 блока 11, N выходов 11.2-21-11.2-2N счетчика 11.2 соединены с соответствующими N входами 11.1-21-11.1-2N регистра хранения 11.1. Причем N-разрядный транзитный выход 11.1-3 регистра хранения 11.1 является N-разрядным транзитным выходом 113 блока 11, N проверочных выходов 11.1-11-11.1-1N регистра хранения 11.1 являются соответствующими N проверочными выходами 1121-112N блока анализа исходных данных 11.

Регистр хранения 11.1 блока анализа исходных данных 11 предназначен для принятия решения о математической природе исходных данных (вида взаимосвязи параметров случайного процесса), заданных в виде двоичного кода - взаимосвязь каждого очередного значения случайного процесса с предыдущим заданы вероятностно (количественно) или с использованием функции принадлежности, характерной для нечетких множеств. Регистр хранения 11.1 может быть реализован на базе типового регистра хранения на D-триггерах, описанного в литературе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 156-158, рис. 5.27].

Счетчик 11.2 блока анализа исходных данных 11 предназначен для регистрации и последовательного сравнения (по количеству разрядов) поступающих в двоичном коде данных, характеризующих взаимосвязь каждого очередного значения случайного процесса с предыдущим. Техническая реализация счетчика 11.2 возможна на базе серийно выпускаемого счетчика с параллельным переносом на N-триггерах, как показано в работе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 172-175, рис. 5.40].

Блок преобразования исходных данных 12, изображенный на фиг. 3, предназначен для трансформирования исходных данных, заданных в нечеткой форме к виду, пригодному для осуществления процедуры параметрического моделирования (генерирования) случайных процессов.

Блок преобразования исходных данных 12 (фиг. 3) состоит из регистра 12.1, элемента расчета дополнения 12.2, главного 12.3 и вспомогательного 12.4 элементов хранения, главного 12.5 и вспомогательного 12.6 анализаторов, элемента расчета объединения 12.7 и вычислителя 12.8. При этом N-разрядный выход 12.8-2 вычислителя 12.8 является N-разрядным выходом 122 блока преобразования исходных данных 12, N входов 12.1-11-12.1-1N регистра 12.1 являются соответствующими N проверочными входами 1211-121N блока 12, N первичных выходов 12.1-21-12.1-2N регистра 12.1 подключены к соответствующим N первичным входам 12.2-11-12.2-1N элемента расчета дополнения 12.2 и к соответствующим N входам 12.3-11-12.3-1N главного элемента хранения 12.3, N вторичных выходов 12.1-31-12.1-3N регистра 12.1 подключены к соответствующим N вторичным входам 12.2-21-12.2-2N элемента расчета дополнения 12.2 и к соответствующим N прямым входам 12.4-11-12.4-1N вспомогательного элемента хранения 12.4, N выходов 12.3-21-12.3-2N главного элемента хранения 12.3 подключены к соответствующим N основным входам 12.5-11-12.5-1N главного анализатора 12.5, N выходов 12.4-21-12.4-2N вспомогательного элемента хранения 12.4 подключены к соответствующим N основным входам 12.6-11-12.6-1N вспомогательного анализатора 12.6, N дополнительных входов 12.5-21-12.5-2N главного анализатора 12.5 подключены к соответствующим N первичным выходам 12.2-31-12.2-3N элемента расчета дополнения 12.2. Причем N вторичных выходов 12.2-41-12.2-4N элемента расчета дополнения 12.2 соединены с соответствующими N дополнительными входами 12.6-21-12.6-2N вспомогательного анализатора 12.6, N выходов 12.5-31-12.5-3N главного анализатора 12.5 подключены к соответствующим N первичным входам 12.7-11-12.1-1N элемента расчета объединения 12.7, N вторичных входов 12.7-21-12.7-2N которого соединены с соответствующими N выходами 12.6-31-12.6-3N вспомогательного анализатора 12.6, N выходов 12.7-31-12.7-3N элемента расчета объединения 12.7 соединены с соответствующими N дополнительными входами 12.2-51-12.2-51 элемента расчета дополнения 12.2, соответствующими N дополнительными входами 12.4-31-12.4-3N вспомогательного элемента хранения 12.4 и соответствующими N входами 12.8-11-12.8-1N вычислителя 12.8.

Регистр 12.1 блока преобразования исходных данных 12 предназначен для регистрации и сортировки поступающей нечеткой информации на две составляющие, по начальному количеству мнений экспертов о каждом из N нечетко заданных данных, характеризующих взаимосвязь каждого очередного значения случайного процесса с предыдущим. Регистр 12.1 может быть технически реализован на базе серийно выпускаемого двоичного счетчика с последовательным переносом на Т-триггерах, как описано в [Угрюмов Е.П. Проектирование элементов и узлов ЭВМ. - М.: Высшая школа, 1987. С. 138-141, рис. 9.1.].

Элемент расчета дополнения 12.2 блока преобразования исходных данных 12 предназначен для реализации процедуры арифметического вычитания из единицы значений функций принадлежности нечетких множеств. Частным случаем технической реализации элемента расчета дополнения 12.2 может служить обычное арифметико-логическое устройство (АЛУ), описанное, например, в [Угрюмов Е.П. Проектирование элементов и узлов ЭВМ. - М.: Высшая школа, 1987. С. 196-198, рис. 11.15].

Главный 12.3 и вспомогательный 12.4 элементы хранения блока преобразования исходных данных 12 предназначены соответственно для хранения нечеткой исходной информации, поступающей от первого и второго эксперта (от эксперта Lu Z), т.е. для хранения количественно выраженных двух (по начальному числу экспертов) мнений экспертов о каждом из N нечетко заданных данных, характеризующих взаимосвязь каждого очередного значения случайного процесса с предыдущим. Главный элемент хранения 12.3 может быть технически реализован в виде серийно выпускаемого динамического оперативного запоминающего устройства, как показано в литературе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 194-196, рис. 6.9 (б)]. Вспомогательный элемент хранения 12.4 отличается от главного элемента хранения 12.3 лишь наличием дополнительных N входов (12.4-31-12.4-3N), которые технически могут быть легко объединены с соответствующими N прямыми входами (12.4-11-12.4-1N), что позволяет осуществить реализацию вспомогательного элемента хранения 12.4 аналогично главному элементу хранения 12.3, в виде динамического оперативного запоминающего устройства, как описано в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 194-196, рис. 6.9 (б)].

Главный анализатор 12.5 блока преобразования исходных данных 12 предназначен для определения пересечения нечетких множеств - пересечения дополнения нечеткого множества, сформулированного экспертом L с нечетким множеством, сформулированным экспертом Z. Главный анализатор 12.5 может быть технически реализован на базе цифрового узла сравнения, как показано в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 149-152, рис. 5.22 (a)].

Вспомогательный анализатор 12.6 блока преобразования исходных данных 12 предназначен для определения пересечения нечетких множеств - пересечения нечеткого множества, сформулированного экспертом L с дополнением нечеткого множества, сформулированного экспертом Z. Вспомогательный анализатор 12.6 также может быть технически реализован на базе цифрового узла сравнения, как описано в [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 149-152, рис. 5.22 (a)].

Элемент расчета объединения 12.7 блока преобразования исходных данных 12 предназначен для реализации завершающего цикла дизъюнктивного суммирования -определения объединения нечетких множеств. Элемент расчета объединения 12.7 представляет собой цифровой узел сравнения и может быть технически реализован в виде серийно выпускаемого быстродействующего цифрового узла сравнения, как показано в работе [Гусев В.В., Лебедев О.Н., Сидоров A.M. Основы импульсной и цифровой техники. - СПб.: СПВВИУС, 1995. С. 149-152, рис. 5.19].

Вычислитель 12.8 блока преобразования исходных данных 12 предназначен для однозначного выбора (присвоения) количественных (вероятностных) значений анализируемых данных, характеризующих взаимосвязь каждого очередного значения случайного процесса с предыдущим. Вычислитель 12.8 представляет собой серийно выпускаемый программируемый ТТЛ-компаратор типа 74LS85, описанный в [Янсен Й. Курс цифровой электроники: Сложные ИС для устройств передачи данных. Т. 3. - М.: Мир, 1987. С. 38-40, рис. 1.21].

Первый селектор-мультиплексор 1, входящий в общую структурную схему генератора случайной последовательности, предназначен для коммутации на свой N-разрядный выход сигналов одной из двух групп: с первого N-разрядного информационного входа 0011 (входа для разрядов A1-AN) либо со второго N-разрядного информационного входа 0012 (входа для разрядов B1-BN). Схема построения первого селектора-мультиплексора 1 известна, он может быть технически реализован на базе серийно выпускаемого N-разрядного селектора-мультиплексора, как показано в [И.И. Петровский и др.: «Логические ИС КР1533, КР1554», справочник в двух частях, часть 1-М.: Бином, 1993, с. 211].

Второй селектор-мультиплексор 2, входящий в общую структурную схему генератора случайной последовательности, предназначен для коммутации на свой N-разрядный выход сигналов одной из двух групп: с первого N-разрядного входа 21 (входа для разрядов A1-AN) либо со второго N-разрядного информационного входа 22 (входа для разрядов B1-BN). Он отвечает за запись новых значений (для данного шага) верхних границ интервалов, на которые разбивается множество адресов заданного набора данных, определяемых на каждом последующем шаге параметрически (количественно) и нечетко заданными вероятностями переходов случайного процесса из состояния в состояние [1]. Схема построения второго селектора-мультиплексора 2 известна и аналогична схеме первого селектора-мультиплексора 1. Он может быть технически реализован на базе серийно выпускаемого N-разрядного селектора-мультиплексора, как показано в [И.И. Петровский и др.: «Логические ИС КР1533, КР1554», справочник в двух частях, часть 1 - М.: Бином, 1993, с. 211].

Первый регистр 3, входящий в общую структурную схему генератора случайной последовательности, предназначен для регистрации и хранения двоичных кодов, определяющих генерацию последовательности значений из заданного множества значений с учетом наличия не только вероятностной, но и неоднозначной (нечеткой) связи каждого очередного значения с предыдущим. Он отвечает за регистрацию и хранение значений новых (для каждого последующего шага) верхних границ интервалов, величина которых динамично изменяется по методам марковских цепей, зависит от вероятности перехода случайного процесса из состояния в состояние и соответствует значениям требуемых на данном шаге вероятностей наблюдения соответствующих элементов заданного набора данных. Описание работы и схема таких регистров известны и приведены, например, в книге [П.П. Мальцев, Н.С. Долидзе и др., «Цифровые интегральные микросхемы: справочник», - М.: «Радио и связь», 1994, с. 57-62].

Источник случайных чисел 4, входящий в общую структурную схему генератора случайной последовательности, предназначен для генерирования P-разрядных случайных чисел, известен, и может быть технически реализован, как показано, например, в [М.П. Бобнев «Генерирование случайных сигналов», - М: Энергия, 1971, с. 168-174].

Оперативное запоминающее устройство 5, входящее в общую структурную схему генератора случайной последовательности, предназначено для хранения значений элементов заданного набора данных. Схема построения оперативного запоминающего устройства известна, он может быть технически реализован на базе серийно выпускаемого оперативного запоминающего устройства, как показано в [В.Л. Шило «Популярные цифровые микросхемы», - М: «Радио и связь», 1987, с. 164-166].

Блоки хранения границ интервалов 61-6K, входящие в общую структурную схему генератора случайной последовательности, предназначены для хранения двоичных кодов, определяющих граничные значения вероятности появления соответствующих элементов заданного набора данных (набора данных в заданном интервале). Они выполненных в виде оперативных запоминающих устройств, структура их построения известна, они могут быть технически реализованы на базе серийно выпускаемых оперативных запоминающих устройств, как показано в [В.Л. Шило «Популярные цифровые микросхемы», - М.: «Радио и связь», 1987, с. 164-166].

Блоки сравнения 71-7K, входящие в общую структурную схему генератора случайной последовательности, предназначены для сравнения случайного значения, генерируемого источником случайных чисел, и значения на выходе соответствующего регистра, а также для формирования результата сравнения. Блок сравнения 7k может быть технически реализован, как показано на фиг. 4, содержит компаратор 7.1k, P-входовый элемент ИЛИ-НЕ 7.2k и элемент ИЛИ 7.3k первый вход 7.3k-1 которого подключен к выходу «Неравенство» 7.1k-3 (выходу А>В) компаратора 7.1k. Второй вход 7.3k-2 элемента ИЛИ 7.3k подключен к инверсному выходу 7.2k-2 P-входового элемента ИЛИ-НЕ 7.2k, выход 7.3k-3 элемента ИЛИ 7.3k является выходом «Результат сравнения» 7.3k блока сравнения 7k. Р входов (входов A1-AP) первой группы 7.1k-1 информационных входов компаратора 7.1k являются P-разрядным входом «Случайное число» 7.1k блока сравнения 7k, Р входов (входов B1-BP) второй группы 7.1k-2 информационных входов компаратора 7.1k соединены с соответствующими входами 7.2k-11-7.2k-1P P-входового элемента ИЛИ-НЕ 7.2k и являются вторым P-разрядным информационным входом «Верхняя граница» 72k блока сравнения 7k.

Компаратор 7.1k блока сравнения 7k предназначен для сравнения двух P-разрядных чисел и формирования результата сравнения. Описание работы и схема компаратора известны, приведены, например, в книге [В.Л. Шило «Популярные цифровые микросхемы», - М.: «Радио и связь», 1987, с. 183-184].

Элемент ИЛИ-НЕ 7.2k блока сравнения 7k предназначен для формирования на своем выходе значения логического нуля, если на всех разрядах второго P-разрядного входа «Верхняя граница» 72k блока сравнения 7k установлены значения логической единицы. Элемент ИЛИ-НЕ 7.2k может быть реализован технически на базе серийно выпускаемого элемента ИЛИ-НЕ, как показано в [И.И.Петровский и др.: «Логические ИС КР1533, КР1554», справочник в двух частях, часть 1 - М.: Бином, 1993, с. 246-247].

Элемент ИЛИ 7.3k блока сравнения 7k предназначен для формирования на своем выходе значения логической единицы, если на одном из его входов имеется значение логической единицы, схема реализации такого элемента ИЛИ известна и описана, например, в [Б.В. Тарабрин, СВ. Якубовский, Н.А. Барканов и др. «Справочник по интегральным микросхемам». - 2-е изд., перераб. и доп. - М: Энергия, 1981, с. 109].

Шифратор приоритетов 8, входящий в общую схему генератора случайной последовательности, предназначен для преобразования значения логического нуля на одном из его входов в соответствующий двоичный код на его выходе, причем преобразование осуществляется с учетом приоритетов, определяемых номером входа. Схема реализации шифратора приоритетов известна и подробно описана, например, в [П.П. Мальцев, Н.С. Долидзе и др., «Цифровые интегральные микросхемы: справочник», - М.: «Радио и связь», 1994, с. 40-41].

Инверторы 91-9N, входящие в общую схему генератора случайной последовательности, предназначены для инвертирования сигналов с инверсных выходов шифратора приоритетов. Схема реализации инвертора известна и подробно описана, например, в [И.И. Петровский и др.: «Логические ИС КР1533, КР1554», справочник в двух частях, часть 1. - М.: Бином, 1993, с. 471-472].

Второй регистр 10, входящий в общую схему генератора случайной последовательности, предназначен для хранения двоичных кодов, определяющих вероятности появления соответствующих элементов заданного набора данных. Он отвечает за регистрацию и хранение значений предыдущих (для прошлого шага) верхних границ интервалов (полученных с учетом наличия не только вероятностной, но и неоднозначной, нечеткой связи каждого очередного значения с предыдущим), величина которых динамично изменяется по методам марковских цепей, зависит от вероятности перехода случайного процесса из состояния в состояние и соответствует значениям требуемых на прошедшем шаге вероятностей наблюдения соответствующих элементов заданного набора данных. Он аналогичен первому регистру 3, описание работы и схема таких регистров известны и приведены, например, в книге [П.П. Мальцев, Н.С. Долидзе и др., «Цифровые интегральные микросхемы: справочник», - М.: «Радио и связь», 1994, с. 57-62].

В заявленном устройстве генерирование заданных значений набора данных с учетом как вероятностной, так и неоднозначной (нечеткой) связи каждого очередного значения с предыдущим, осуществляется поэтапно, первым этапом является учет вероятностной связи каждого очередного значения с предыдущим, реализуемое на основе закона распределения, который задается путем указания требуемой вероятности появления соответствующего элемента заданного набора данных. При этом применяется подход [3], основанный на использовании источника случайных чисел, распределенных равномерно в диапазоне [0; 1). Данный диапазон разбивается на совокупность интервалов, количество которых соответствует количеств