Команды, процессоры, способы и системы доступа множественных регистров к памяти

Иллюстрации

Показать всеИзобретение относится к вычислительной технике. Технический результат заключается в обеспечении возможности сохранять большие операнды без необходимости увеличивать разрядность физических регистров. Процессор содержит множество N-разрядных регистров; декодирующее звено, выполненное с возможностью приема команды на доступ к памяти множества регистров, причем команда на доступ к памяти множества регистров указывает ячейку памяти и указывает регистр; и звено доступа к памяти, сопряженное с декодирующим звеном и с указанным множеством N-разрядных регистров, причем звено доступа к памяти выполнено с возможностью в ответ на команду на доступ к памяти множества регистров выполнения операции доступа к памяти множества регистров, причем операция доступа к памяти множества регистров включает в себя использование своего набора N-разрядных данных в каждом из указанного множества N-разрядных регистров, содержащих указанный регистр, который является регистром, из которого загружают данные, или регистром, в котором сохраняют данные, и различных соответствующих N-разрядных участков в М×N-разрядной строке памяти, соответствующей указанной ячейке памяти. 4 н. и 20 з.п. ф-лы, 21 ил.

Реферат

ПРЕДЩЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Область техники, к которой относится изобретение

Описываемые здесь варианты воплощения изобретения, в общем, относятся к процессорам. В частности, описываемые здесь варианты воплощения изобретения, в общем, относятся к доступу к данным в памяти, осуществляемому процессорами.

Уровень техники

Многие процессоры имеют архитектуры с одним потоком команд и многими потоками данных (SIMD - архитектуры). В SIMD - архитектурах команда обработки упакованных данных (данных в упакованном формате), векторная команда или SIMD - команда могут оперировать множественными элементами данных (например, множественными парами элементов данных) одновременно или параллельно. Множественные элементы данных могут быть упакованы в пределах некоторого регистра или ячейки памяти как упакованные данные. В упакованных данных разряды регистра или другого места хранения информации могут быть логически разделены на последовательность элементов данных. Например, регистр для упакованных данных с разрядностью в 64 разряда может иметь два упакованных 32 - разрядных элемента данных, четыре упакованных 16 - разрядных элемента данных или восемь упакованных 8 - разрядных элементов данных. Процессор может иметь аппаратное обеспечение для параллельного исполнения, отвечающее на команду обработки упакованных данных таким образом, что одновременно (например, параллельно) выполняет множественные операции.

В некоторых процессорах за эти годы имело место прогрессирующее увеличение разрядности операндов, состоящих из упакованных данных. Это увеличение разрядности операндов, состоящих из упакованных данных, вообще говоря, позволяет одновременно (например, параллельно) обрабатывать большее количество элементов данных, что, вообще говоря, помогает повысить производительность. Например, операнд, состоящий из упакованных данных с разрядностью в 128 разрядов, может иметь четыре 32 - разрядных элемента данных (вместо только двух в случае операнда, состоящего из упакованных данных с разрядностью в 64 - разряда), восемь 16 - разрядных элементов упакованных данных (вместо только четырех в случае операнда, состоящего из упакованных данных с разрядностью в 64 - разряда), и так далее.

В некоторых процессорах увеличение разрядности операндов, состоящих из упакованных данных, сопровождается соответствующим увеличением разрядности регистров. Однако один возможный недостаток увеличения разрядности регистров заключается в увеличении площади или занимаемого места, занимаемых регистрами на кристалле. Например, увеличение разрядности каждого регистра из набора 64 -разрядных регистров, такое чтобы они каждый были 128 - разрядными регистрами, вероятно, приблизительно удвоит площадь или занимаемое место, занимаемые регистрами на кристалле. Влияние этого, вероятно, будет даже больше в тех вариантах реализации, в которых физических регистров реализовано больше, чем архитектурных регистров, поскольку приблизительно удвоиться может размер большего количества регистров. Другой возможный недостаток такого рода увеличения разрядности регистров заключается в соответствующем увеличении количества данных о состоянии, контексте или других данных, хранимых в регистрах, которые необходимо помещать в эти регистры и извлекать из них (например, сохранять и восстанавливать) при переключениях контекста, сохранениях состояний в режимах электропитания и подобных переходах. Например, для каждого регистра может потребоваться при изменениях контекста загружать и выгружать 128 разрядов вместо только 64 разрядов.

Процессоры обычно исполняют команды на загрузку данных (например, операнды, состоящие их упакованных данных) из памяти и сохранение данных (например, операндов, состоящих из упакованных данных) в память. Например, процессор может исполнять команду на загрузку из памяти для того, чтобы загружать или считывать операнд, состоящий из упакованных данных, из памяти в регистр адресат. Процессор может исполнять команду на запись в память для того, чтобы записывать или сохранять операнд, состоящий из упакованных данных, из регистра - источника в память.

Краткое описание чертежей

Изобретение можно лучше всего понять, обратившись к нижеследующему описанию и прилагаемым к нему чертежам, которые используются для того, чтобы проиллюстрировать варианты воплощения изобретения. На чертежах:

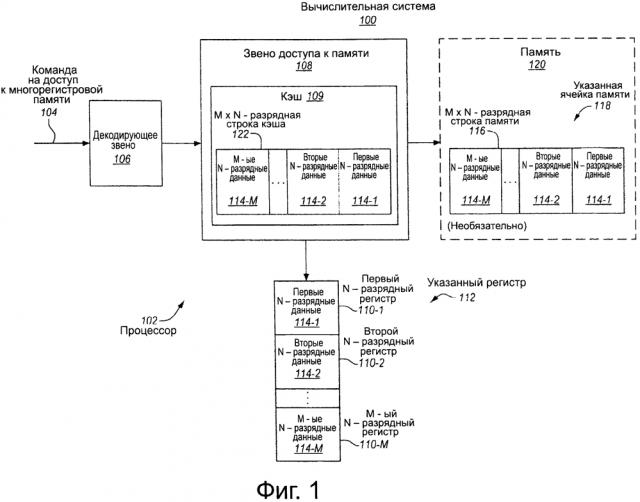

Фиг. 1 представляет собой блок-схему одного варианта воплощения вычислительной системы.

Фиг. 2 представляет собой блок-схему алгоритма одного варианта воплощения способа обработки одного варианта воплощения команды на доступ множественных регистров к памяти.

Фиг. 3 представляет собой блок-схему алгоритма одного варианта воплощения способа обработки одного варианта воплощения команды на загрузку множественных регистров из памяти.

Фиг. 4 представляет собой блок-схему алгоритма одного варианта воплощения способа обработки одного варианта воплощения команды на запись из множественных регистров в память.

Фиг. 5 представляет собой структурную схему для первого приводимого в качестве примера варианта воплощения подходящей операции доступа множественных регистров к памяти.

Фиг. 6 представляет собой структурную схему для второго приводимого в качестве примера варианта воплощения подходящей операции доступа множественных регистров к памяти.

Фиг. 7 представляет собой структурную схему для третьего приводимого в качестве примера варианта воплощения подходящей операции доступа множественных регистров к памяти.

Фиг. 8 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором набор регистров можно рассматривать или осуществлять к нему доступ, в различных представлениях, как к 64 - разрядным регистрам, 128 - разрядным регистрам и 256 - разрядным регистрам.

Фиг. 9А-9С представляют собой блок-схемы вариантов воплощения подходящих форматов команды для команд на доступ множественных регистров к памяти.

Фиг. 10А представляет собой блок-схему, на которой проиллюстрированы как приводимый в качестве примера конвейер без переупорядочения последовательности команд, так и приводимый в качестве примера конвейер с переименованием регистров, переупорядочиванием последовательности выдачи/исполнения команд, соответствующие вариантам воплощения изобретения.

Фиг. 10В представляет собой блок-схему, на которой проиллюстрированы как приводимый в качестве примера вариант воплощения ядра, имеющего архитектуру без переупорядочения последовательности команд, так и приводимое в качестве примера ядро, имеющее архитектуру с переименованием регистров, переупорядочиванием последовательности выдачи/исполнения команд, подлежащие включению в состав процессора, соответствующего вариантам воплощения изобретения.

Фиг. 11А представляет собой блок-схему одиночного ядра процессора наряду с его соединением с расположенной на кристалле сетью межсоединений и с его локальным подмножеством кэша уровня 2 (L 2), соответствующих вариантам воплощения изобретения.

Фиг. 11В представляет собой расширенное представление части ядра процессора, показанного на Фиг. 11А, соответствующего вариантам воплощения изобретения.

Фиг. 12 представляет собой блок-схему процессора, который может иметь больше чем одно ядро, может иметь интегрированный контроллер памяти и может иметь интегрированные графические средства, соответствующего вариантам воплощения изобретения.

На Фиг. 13 показана блок-схема системы в соответствии с одним вариантом воплощения настоящего изобретения.

На Фиг. 14 показана блок-схема первой более конкретной системы, приводимой в качестве примера, в соответствии с одним вариантом воплощения настоящего изобретения.

На Фиг. 15 показана блок-схема второй более конкретной системы, приводимой в качестве примера, в соответствии с одним вариантом воплощения настоящего изобретения.

На Фиг. 16 показана блок-схема внутрикристальной системы (SoC) в соответствии с одним вариантом воплощения настоящего изобретения.

Фиг. 17 представляет собой блок-схему, на которой сравнивается использование конвертора команд, реализованного программными средствами, для того, чтобы конвертировать двоичные команды в некотором исходном наборе команд в двоичные команды в некотором заданном наборе команд в соответствии с вариантами воплощения изобретения.

Подробное описание вариантов осуществления изобретения

В нижеследующем описании, излагаются многочисленные конкретные подробности (например, конкретные операции, выполняемые в ответ на команды, конкретные количества регистров, конкретные емкости регистров, конкретные размеры строк кэша, конкретные конфигурации процессора, конкретные микроархитектурные подробности, конкретные последовательности операций и так далее). Однако варианты воплощения изобретения могут быть осуществлены на практике без этих конкретных подробностей. В других случаях, хорошо известные схемы, конструкции и технологии не показаны подробно во избежание затруднения понимания этого описания.

Традиционные команды на доступ к памяти часто включают в себя только одиночный регистр при доступе к памяти. Количество данных, обмен которыми осуществляется между памятью и этим одиночным регистром, составляет только разрядность этого одиночного регистра (например, 64 разряда в случае 64 - разрядных регистров). Однако обычно данные в памяти организованы как "строки" большей разрядности. Эти строки памяти представляют количество данных, передача или обмен которыми осуществляется между памятью и процессором, например, одним или более кэшеми процессора. Например, даже притом, что в регистровый файл или из него фактически могут передаваться только 64 разряда данных, обычно между памятью и кэшем процессора может передаваться целая строка памяти большей разрядности, имеющая эти 64 разряда данных. Строка памяти может быть сохранена в строке кэша, имеющейся в пределах кэша. Многие процессоры обычно используют строки памяти, имеющие разрядность в 512 разрядов, и соответствующие им строки кэша, имеющие разрядность в 512 разрядов. При загрузке 64 - разрядных данных в одиночный регистр адресат, может загружаться или извлекаться в 512 - разрядную строку кэша, находящуюся в кэше процессора, вся 512 - разрядная строка памяти, имеющая эти 64 -разрядные данные, а в этот одиночный регистр - адресат могут загружаться только эти 64 - разрядные данные. Только 64 разряда данных будут фактически переданы из кэша в регистровый файл.

Один потенциальный недостаток таких традиционных команд на доступ к памяти при "одиночном регистре" заключается в том, что используемая ширина полосы пропускания между кэшем и регистрами может иметь тенденцию быть относительно низкой, особенно в тех процессорах, которые используют для хранения упакованных данных регистры с относительно малой разрядностью. В некоторых случаях, другие данные в пределах той же самой строки памяти и/или строки кэша могут также требоваться для обработки, но обычно не передаются в регистры этой командой. Например, это может иметь место для операндов в памяти, состоящих из упакованных данных большой разрядности, которые имеют более высокую разрядность, чем регистры процессора. В некоторых случаях, может быть желательно загрузить в регистры процессора по меньшей мере половину строки памяти, или, в других случаях, всю строку памяти. Один возможный способ загрузить всю 512 - разрядную строку памяти в восемь 64 - разрядных регистров состоял бы в том, чтобы использовать загрузку восьми отдельных одиночных 64 - разрядных регистров из команд доступа к памяти. Например, первая загрузка одиночного 64 - разрядного регистра из команды на доступ в память, указывающей некоторые первые 64 - разрядные данные 512 -разрядной строки в памяти, может загрузить и сохранить указанную первую 64 - разрядную порцию в первом указанном регистре. Вся 512 - разрядная строка памяти может быть извлечена из памяти в процессор и сохранена в 512 - разрядной строке кэша. Вторая загрузка одиночного 64 - разрядного регистра из команды на доступ в память, указывающей некоторые вторые 64 - разрядные данные 512 - разрядной строки в памяти, может загрузить указанную вторую 64 - разрядную порцию из уже загруженной 512 - разрядной строки кэша и сохранить вторые 64 - разрядные данные во втором указанном регистре. Аналогичным образом, загрузка одиночных 64 - разрядных регистров: с третей по восьмую, из команд на доступ к памяти может также использовать данные из строки кэша, уже загруженной в кэш. Однако возможный недостаток такого рода подхода заключается в необходимости исполнять множественные команды, что ведет к увеличению размера кода и продолжительности обработки данных, и может включать в себя множественные доступы к кэшу.

Здесь раскрываются команды на доступ множественных регистров к памяти, процессоры для исполнения этих команд, способы, выполняемые этими процессорами при обработке или исполнении этих команд, и системы, включающие в себя один или более процессоров для обработки или исполнения этих команд.

Фиг. 1 представляет собой структурную схему одного варианта воплощения вычислительной системы (100). В различных вариантах воплощения изобретения, эта вычислительная система может представлять настольный компьютер, переносной компьютер, компьютер типа "ноутбук", планшетный компьютер, "нетбук" (переносной компьютер для работы в сети), "смартфон" (мобильный телефон, обладающий рядом функций компьютера), персонального цифрового секретаря, сотовый телефон, сервер, сетевое устройство (например, маршрутизатор или коммутатор), мобильное интернет - устройство (MID - устройство), универсальный проигрыватель, интеллектуальный телевизор, телевизионную абонентскую приставку, контроллер для видеоигр или другой тип электронного устройства, имеющего по меньшей мере один процессор.

Эта вычислительная система включает в себя процессор (102) и память (120). Память может включать в себя одно или более запоминающих устройств либо одного и того же, либо различных типов. Один общий тип памяти, который подходит для вариантов воплощения изобретения, представляет собой динамическое оперативное запоминающее устройство (DRAM), хотя могут также использоваться и другие типы памяти (например, флэш - память). Процессор и память сопряжены друг с другом механизмом (124) межсоединения. Для сопряжения процессора с памятью подходит любой традиционный механизм межсоединения, известный в данной области техники. Примеры таких механизмов включают в себя межсоединения, шины, концентраторы, контроллеры памяти, наборы микросхем, компоненты набора микросхем и тому подобное и их сочетания, но не ограничиваются ими.

Процессор (102) представляет аппарат для обработки команд, который может быть приведен в действие для обработки команд. В некоторых вариантах воплощения изобретения, этот процессор может представлять собой универсальный процессор (например, универсальный микропроцессор, относящийся к типу, используемому в настольном компьютере, переносном компьютере и подобных им компьютерах). В качестве альтернативы, этот процессор может представлять собой процессор специального назначения. Примеры подходящих процессоров специального назначения включают в себя: сетевые процессоры, процессоры передачи данных, криптографические процессоры, графические процессоры, сопроцессоры, встроенные процессоры, процессоры цифровой обработки сигналов (DSP - процессоры) и контроллеры (например, микроконтроллеры), в качестве лишь нескольких примеров, но не ограничиваются ими. Процессор может представлять собой любой процессор из числа: разнообразных процессоров для вычислений со сложным набором команд (CISC - процессоров), разнообразных процессоров для вычислений с сокращенным набором команд (RISC - процессоров), разнообразных процессоров с командными словами сверхбольшой длины (VLIW - процессоров), разнообразных гибридов этих процессоров или других типов процессоров без каких бы то ни было исключений.

Процессор (102) может принимать команду (104) на доступ множественных регистров к памяти. В некоторых вариантах воплощения изобретения, команда на доступ множественных регистров к памяти может представлять команду на загрузку множественных регистров из памяти. В других вариантах воплощения изобретения, команда на доступ множественных регистров к памяти может представлять команду на сохранение данных из множественных регистров в памяти. Команда на доступ множественных регистров к памяти может представить команду в машинном коде, команду на языке ассемблера, макрокоманду или управляющий сигнал набора команд процессора. В некоторых вариантах воплощения изобретения, команда на доступ множественных регистров к памяти может явным образом специфицировать (например, посредством некоторого набора разрядов или одного или более полей), или иным образом указывать (например, неявно указывать) ячейку (118) памяти, находящуюся в памяти (120), и может явным образом специфицировать или иным образом указывать регистр (112) (например, регистр, реализованный набором N - разрядных регистров (110)).

Процессор включает в себя звено (106) декодирования команд. Звено (106) декодирования команд может также упоминаться как декодирующее звено, декодер или декодирующая логика. Декодирующее звено может принимать и декодировать команды относительно более высокого уровня (например, команды в машинном коде, команды на языке ассемблера, макрокоманды), и выводить одну или более команд относительно более низкого уровня или управляющие сигналы (например, микрокоманды, микрооперации, точки входа в микрокод), которые отражают, представляют команды более высокого уровня и/или выведены из них. Эти одна или более команд более низкого уровня или управляющие сигналы могут реализовывать команду более высокого уровня посредством одной или более операций более низкого уровня (например, уровня схемы или уровня аппаратного обеспечения). Декодирующее звено может быть реализовано с использованием всевозможных различных механизмов, включающих в себя: постоянные запоминающие устройства для микрокода (ROM - устройства), таблицы поиска, аппаратные варианты реализации, программируемые логические матрицы (PLA - матрицы) и другие механизмы, используемые для реализации декодирующих звеньев, известные в данной области техники, но не ограниченных этими механизмами.

В других вариантах воплощения изобретения могут быть использованы эмулятор, транслятор, блок трансформации, интерпретатор команд или другая логика конвертирования команд. В данной области техники известны всевозможные различные типы логики конвертирования команд, и они могут быть реализованы в виде программного обеспечения, аппаратного обеспечения, микропрограммного обеспечения или их сочетания. Логика конвертирования команд может эмулировать, транслировать, трансформировать, интерпретировать или иным образом конвертировать команду в одну или более соответствующих производных команд или управляющих сигналов. В некоторых вариантах воплощения изобретения могут быть использованы как логика конвертирования команд, так и декодирующее звено. Например, логика конвертирования команд может конвертировать команду в одну или более промежуточных команд, а декодирующее звено может декодировать эти одну или более промежуточных команд в одну или более команд более низкого уровня или управляющих сигналов, исполняемых интегральными схемами процессора. Логика конвертирования команд может быть расположена вне процессора (например, на отдельном кристалле или в памяти), на процессоре или и там и там.

Обратимся вновь к Фиг. 1, на которой с декодирующим звеном (106) сопряжено звено (108) доступа к памяти. Звено доступа к памяти может принимать одну или более декодированных или иным образом конвертированных команд или управляющих сигналов, которые представляют команду (104) на доступ множественных регистров к памяти и/или выведены из нее. Звено доступа к памяти также сопряжен с памятью (120) посредством механизма (124) межсоединения. Звено доступа к памяти может реализовывать один или более компонентов, часто находящихся в подсистеме памяти процессоров, для осуществления доступа или взаимодействия с памятью. Примеры таких компонентов включают в себя, логику доступа к памяти, звено интерфейса шины, один или более уровней кэша, один или более буферов быстрого преобразования адреса (TLS - буферов), логика преобразования виртуального адреса и так далее, но не ограничиваются ими. Как показано на чертеже, звено доступа к памяти может иметь по меньшей мере один кэш (109).

Процессор (102) также включает в себя набор N - разрядных регистров (110). Каждый из регистров может представлять находящееся на кристалле место хранения данных, которое способно функционировать таким образом, чтобы сохранять данные, например, N - разрядные данные. В некоторых вариантах воплощения изобретения, N - разрядные регистры могут представлять регистры для упакованных данных, способные функционировать таким образом, чтобы сохранять N - разрядные упакованные данные, векторные данные или данные для архитектуры с одним потоком команд и многими потоками данных (SIMD - данные), хотя это не обязательное требование. В разнообразных вариантах воплощения изобретения, N - разрядные регистры могут представлять собой 64 - разрядные регистры, 128 - разрядные регистры или 256 - разрядные регистры. В качестве альтернативы, N - разрядные регистры могут иметь другие размеры (например, 32 - разрядные регистры, 80 - разрядные регистры и так далее). В некоторых вариантах воплощения изобретения, набор N - разрядных регистров может включить в себя, реализовывать или иным образом содержать регистр (112), который указан командой на доступ множественных регистров к памяти. Регистры могут быть видимыми для программного обеспечения и/или программиста и/или могут быть специфицированы командами из набора команд для идентификации операндов. Регистры могут быть реализованы различными способами в различных микроархитектурах с использованием хорошо известных технологий и не ограничены никаким конкретным типом схемы. Примеры подходящих типов регистров включают в себя: выделенные физические регистры, динамически распределяемые физические регистры с использованием переименования регистров и их сочетания, но не ограничиваются ими.

Как было упомянуто ранее, в некоторых вариантах воплощения изобретения, команда (104) на доступ множественных регистров к памяти может явным образом специфицировать (например, посредством некоторого набора разрядов или одного или более полей) или иным образом указывать (например, указывать неявным образом), регистр (112). В некоторых вариантах воплощения изобретения, набор N - разрядных регистров может включать в себя, реализовывать или иным образом содержать регистр (112) обозначенный командой на доступ множественных регистров к памяти. Помимо этого, в некоторых вариантах воплощения изобретения, команда на доступ множественных регистров к памяти может явным образом специфицировать или иным образом указывать ячейку (118) памяти, находящуюся в этой памяти. В некоторых вариантах воплощения изобретения, данные в памяти могут быть организованы как строки памяти. На иллюстрации показана M×N - разрядная строка (116) памяти, которая (строка) соответствует указанной ячейке (118) памяти (например, включает в себя данные в указанной ячейке памяти). M×N - разрядная строка памяти имеет целое число (М) порций, имеющих разрядность в N - разрядов, данных. Как показано на чертеже, M×N - разрядная строка памяти может иметь данные: с первых N - разрядных данных (114-1) по М-ые N - разрядные данные (114 - М). В некоторых вариантах воплощения изобретения, M×N - разрядная строка представляет собой по меньшей мере 512 разрядов. В одном варианте воплощения изобретения, целое число N может представлять собой 128 разрядов, а целое число М может представлять собой четыре. В другом варианте воплощения изобретения, целое число N может представлять собой 256 разрядов, а целое число М может представлять собой два. В еще одном другом варианте воплощения изобретения, целое число N может представлять собой 64 разряда, а целое число М может представлять собой восемь. В других вариантах воплощения изобретения, разрядность M×N - разрядной строки может иметь другие разрядности (например, 256 разрядов, по меньшей мере 512 разрядов, 1024 разряда и так далее). Количество (М) N - разрядных элементов данных обычно равно разрядности строки памяти, разделенной на разрядность N - разрядных элементов данных. В некоторых вариантах воплощения изобретения, M×N - разрядная строка может иметь разрядность, равную разрядности строки кэша процессора.

В некоторых вариантах воплощения изобретения, звено (108) доступа к памяти способен функционировать в ответ на команду (104) на доступ множественных регистров к памяти и/или в результате этой команды (например, в ответ на одну или более декодированных или иным образом конвертированных команд или управляющих сигналов, которые представляют эту команду на доступ множественных регистров к памяти и/или выведены из нее) таким образом, чтобы выполнять операцию доступа множественных регистров к памяти. В некоторых вариантах воплощения изобретения, в операцию доступа множественных регистров к памяти могут быть вовлечены N - разрядные данные, в каждом из множества N - разрядных регистров (110), которые должны включать в себя, реализовывать или иным образом содержать регистр (112), указанный командой (104). Помимо этого, в некоторых вариантах воплощения изобретения, в операцию доступа множественных регистров к памяти могут также быть вовлечены различные соответствующие N - разрядные порции (114) в M×N - разрядной строке (116) памяти, которая должна соответствовать указанной ячейке (118) памяти. Как показано на чертеже, M×N - разрядная строка памяти может быть сохранена в M×N - разрядной строке (122) кэша, входящей в состав кэша (109), например, в общем традиционным способом. Звено доступа к памяти и/или процессор могут включать в себя специальную или особую логику (например, схемы или другое аппаратное обеспечение, возможно, объединенное с микропрограммным обеспечением и/или программным обеспечением) способную функционировать таким образом, чтобы выполнять операции, отвечающие на эту команду.

В некоторых вариантах воплощения изобретения, команда на доступ множественных регистров к памяти может представлять собой команду на загрузку множественных регистров (осуществляемую) из памяти. В ответ на эту команду на загрузку множественных регистров из памяти, в некоторых вариантах воплощения изобретения, процессор может загрузить в каждый из множества N - разрядных регистров различные N - разрядные порции из M×N - разрядной строки памяти. В других вариантах воплощения изобретения, команда на доступ множественных регистров к памяти может представлять собой команду на запись из множественных регистров в память. В ответ на команду на запись из множественных регистров в память, в некоторых вариантах воплощения изобретения, процессор может записать N -разрядные данные, из каждого из множества N - разрядных регистров, в различные соответствующие N - разрядные порции в M×N - разрядной строке памяти.

В некоторых вариантах воплощения изобретения, суммарное количество разрядов, вовлеченных в операцию доступа множественных регистров к памяти (например, сумма N - разрядных данных в каждом из множества N - разрядных регистров (110), вовлеченных в эту операцию), может составлять по меньшей мере половину, или, в некоторых случаях, вплоть до всех, M×N разрядов строки (116) памяти. В некоторых вариантах воплощения изобретения по меньшей мере половина, или, в некоторых случаях, вплоть до всех, M×N разрядов строки памяти могут быть передана из кэша (109) в набор регистров (110). В разнообразных вариантах воплощения изобретения, могут быть вовлечены по меньшей мере два, три, четыре или более регистров. В качестве одного примера, в одном варианте воплощения изобретения, если M×N разрядов равно 512 разрядам, и N равно 128 разрядам, то в разнообразных аспектах изобретения в операцию доступа множественных регистров к памяти могут быть вовлечены по меньшей мере два 128 - разрядных регистра (110), в некоторых случаях три 128 -разрядных регистра (110) или в некоторых случаях четыре 128 - разрядных регистра (110). В качестве другого примера, в одном варианте воплощения изобретения, если M×N - разрядов равно 512 разрядам, и N равно 64 разрядам, то в разнообразных аспектах изобретения в операцию доступа множественных регистров к памяти могут быть вовлечены по меньшей мере три 64 - разрядных регистра (110) по меньшей мере четыре 64 - разрядных регистра (110) или в некоторых случаях где-нибудь до восьми 64 - разрядных регистров (110). В качестве еще одного другого примера, в одном варианте воплощения изобретения, если M×N разрядов равно 512 разрядам, и N равно 256 разрядам, то в операцию доступа множественных регистров к памяти могут быть вовлечены два 256 - разрядных регистра (110).

Во избежание затруднения понимания описания, на чертеже показан и описан относительно простой процессор (102). В других вариантах воплощения изобретения, процессор, если требуется, может включать в себя другие хорошо известные компоненты, находящиеся в процессорах. Примеры таких компонентов включают в себя: звено предсказания ветвей, звено выборки команд, буферы быстрого преобразования адресов команд и данных, буферы предварительной выборки, очереди микрокоманд, задатчики последовательностей микрокоманд, звено переименования регистров, звено планирования команд, звено изъятия, другие компоненты, входящие в состав процессоров, и разнообразные их сочетания, но не ограничиваются этими компонентами. Имеются без преувеличения многочисленные различные сочетания и конфигурации компонентов в процессорах, и варианты воплощения изобретения не ограничены никаким конкретным сочетанием или конфигурацией. Варианты воплощения изобретения могут быть включены в состав процессоров, иметь множественные ядра, логические процессоры или механизмы исполнения по меньшей мере один из которых способен выполнять вариант воплощения команды на доступ множественных регистров к памяти.

Фиг. 2 представляет собой блок-схему алгоритма одного варианта воплощения способа (230) обработки одного варианта воплощения команды на доступ множественных регистров к памяти. Этот способ может быть выполнен посредством процессора, аппарата для обработки команд, интегральной схемы или тому подобного и/или внутри них.

Способ включает в себя, на этапе 231, прием команды на доступ множественных регистров к памяти. В некоторых вариантах воплощения изобретения, команда (104) на доступ множественных регистров к памяти может специфицировать или иным образом указывать ячейку памяти, и может специфицировать или иным образом указывать регистр. В разнообразных аспектах изобретения, эта команда может быть принята в процессоре, аппарате для обработки команд или их части (например, в звене выборки команд, декодирующем звене, конверторе команд и так далее). В разнообразных аспектах изобретения, эта команда может быть принята от источника, находящегося вне кристалла (например, из памяти, с диска, из межсоединения и так далее), или от источника, находящегося на кристалле, (например, из кэша команд, звена выборки команд и так далее).

Способ включает в себя, на этапе 232, выполнение операции доступа множественных регистров к памяти в ответ на команду на доступ множественных регистров к памяти. В некоторых вариантах воплощения изобретения, операцию доступа к памяти могут выполнять звено доступа к памяти или другая часть процессора. В некоторых вариантах воплощения изобретения, в операцию доступа множественных регистров к памяти могут быть вовлечены N - разрядные данные, в каждом из множества N - разрядных регистров, которые включают в себя, реализуют или иным образом содержат указанный регистр, и различные соответствующие N - разрядные порции в M×N - разрядной строке памяти, которая (строка) соответствует указанной ячейке памяти (например, M×N - разрядная строка памяти включает в себя данные в указанной ячейке памяти).

В некоторых вариантах воплощения изобретения, суммарное количество разрядов N - разрядных данных во множестве N - разрядных регистров, вовлеченных в операцию доступа множественных регистров к памяти, может составлять по меньшей мере половину, или, в некоторых случаях, вплоть до всех, M×N разрядов строки памяти. В некоторых вариантах воплощения изобретения, суммарное количество разрядов N - разрядных данных во множестве N - разрядных регистров, вовлеченных в операцию доступа множественных регистров к памяти, может составлять по меньшей мере 256 разрядов по меньшей мере 512 разрядов или в некоторых случаях большее количество разрядов (например, 1024 разрядов). В разнообразных вариантах воплощения изобретения, в операцию доступа множественных регистров к памяти могут быть вовлечены по меньшей мере два, три, четыре или большее количество регистров.

Фиг. 3 представляет собой блок-схему алгоритма одного варианта воплощения способа (330) обработки одного варианта воплощения команды на загрузку множественных регистров из памяти. Этот способ может быть выполнен посредством процессора, аппарата для обработки команд, интегральной схемы или тому подобного и/или внутри них.

Способ включает в себя, на этапе 331, прием команды на загрузку множественных регистров из памяти. В некоторых вариантах воплощения изобретения, команда на загрузку множественных регистров из памяти может специфицировать или иным образом указывать ячейку памяти, и может специфицировать или иным образом указывать регистр. Эта команда может быть принята различными способами, описанными выше в связи с Фиг. 2.

Способ также включает в себя, на этапе 332, выполнение операции загрузки множественных регистров из памяти в ответ на команду на загрузку множественных регистров из памяти. В некоторых вариантах воплощения изобретения, эту операцию могут выполнять звено доступа к памяти или другая часть процессора. В некоторых вариантах воплощения изобретения, выполнение этой операции может включать в себя загрузку различных N - разрядных порций из M×N - разрядной строки памяти, которая (строка) соответствует указанной ячейке памяти, в каждый из множества N - разрядных регистров, которые содержат указанный регистр. В некоторых вариантах воплощения изобретения, это может включать в себя передачу этих различных N - разрядных порций из M×N - разрядной строки кэша из кэша в каждый из этих различных N - разрядных регистров.

В некоторых вариантах воплощения изобретения, суммарное количество разрядов различных N - разрядных порций, загружаемых во множество N - разрядных регистров из M×N - разрядной строки памяти, составляет по меньшей мере половину, или, в некоторых случаях, вплоть до всех, M×N разрядов строки памяти. В некоторых вариантах воплощения изобретения, суммарное количество разрядов различных N - разрядных порций, загружаемых во множество N - разрядных регистров из M×N - разрядной строки памяти, может составлять по меньшей мере 256 разрядов, по меньшей мере 512 разрядов или в некоторых случаях большее количество разрядов (например, 1024 разряда). В разнообразных вариантах воплощения изобретения, в операцию загрузки множественных регистров из памяти могут быть вовлечены по меньшей мере два, три, четыре или большее количество регистров. В одном конкретном примере, эта операция может загружать различные 128 - разрядные порции строки памяти, которая составляет по меньшей мере 512 разрядов, в каждый из по меньшей мере четырех 128 - разрядных регистров. В другом конкретном примере, эта операция может загружать различные 256 - разрядные порции строки памяти, которая составляет по меньшей мере 512 разрядов, в каждый из по меньшей мере двух 256 - разрядных регистров.

Фиг. 4 представляет собой блок-схему алгоритма одного варианта воплощения способа (430) обработки одного варианта воплощения команды на сохранение из множественных регистров в память. Этот способ может быть выполнен посредством процессора, аппарата для обработки команд, интегральной схемы или тому подобного и/или внутри них.

Способ включает в себя, на этапе 431, прием команды на сохра