Патент ссср 263677

Иллюстрации

Показать всеРеферат

263677 часть этой ячейки восстанавливается с репистра 2, а кодовая — с регистра 4. Затем производится передача содержимого регистра

2 на регистр 1. Описанный процесс повторяется, пока не будут размечены все адреса, после чего регистр 1 обнуляется, а в регистр 2 устанавл ивается код адреса начальной ячейки блока 8.

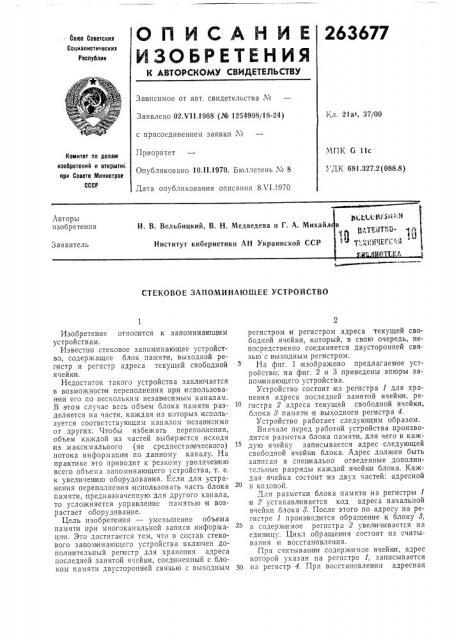

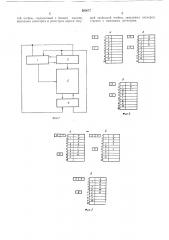

Таким образом, в результате разметки в каждой свободной ячейке блока 8 указан адрес следующей свободной ячейки. Эпюра запоминающего устройства (объем V=10 ячейкам) после указанного процесса разметки показана на фиг. 2, а: слева внизу — репистр

2 текущей свободной ячейки, на котором записан код адреса первой свободной ячейк|и блока; слева сверху — регистр 1 последней занятой ячейки, который в конце процесса разметки обнуляется, основное поле рисунка — блок памяти. Описанная разметка про|изводится 20 один раз .перед работой с предложенным устройством.

Запись в запоминающее устройство производ ится всегда по адресу, содержащемуся в регистре 2. Содержимое этой ячейками считывается на регистр 4. При восстановлении адресная часть ячейки восстанавливается с репистра 1, а в кодовую часть записывается нужная информация. Пр и,этом содержимое адресной части этой ячейками с регистра 4 передается на репистр 2, содержимое которого передается на регистр 1.

Таким образом, при записи содержимое регистров 1 и 2 и адресной части ячейками блока

8, в которую производится запись,:изменяются таким образом, что регистры 1 и 2 указывают новые значения последней занятой и текущей свободной ячеек соответственно, а в адресной части ячейки блока 8 должен быть указан адрес, предыдущей занятой (заполненной) 40 ячейки.

Эпюра запоминающего устройства (V=10) после записи четырех символов А, В, С, D подряд приведена на фиг. 2, б. Репистры 2 и

1 слева указывают адреса соответственно бли- 45 жайшей свободной (5):и последней занятой (4) ячеек. Содержимое адресной части этой ячейки с регистра 4 передается на регистр 1, содержимое которого .переписывается на регистр 2.

Чтение из стековой памяти выполняется по адресу, содержащемуся в регистре 1, т. е. по адресу последней занятой ячейками. Содержимое этой ячейками считывается на регистр 4.

При восстановлении кодовая часть ячейками îá,нуляется, а адресная часть восстанавливается с регистра 2. При этом предыдущее содерж имое адресной части этой ячейки с регистра 4 передается на репистр 1, а его содержимое— на репистр 2.

Таким образом, при чтении содержимое репистров 1 и 2 и адресной части ячейки блока

8, из которой производится чтение, модифицируется так им образом, что регистры 1 IH 2 указывают новое значение адресов последней 65 занятой и текущей свободной ячеек соответственно, а в адресной части ячейки запоминающего устройства должен быть адрес следующей свободной ячейками, Эпюра запоминающего устройства после одного чтения приведена на фиг. 2, в.

Следовательно, в процессе работы стекового запоминающего устройства все его ячейки автоматически размечаются таким образом, что в каждой свободной ячейке всегда указывается адрес следующей свободной, а в каждой занятой ячейке всегда указываегся адрес предыдущей занятой.

Пр и необходимостями использовать стековую память по нескольким (и) независимым каналам в устройстве используется один регистр 2, а репистр 1 разбивается на и независимых частей, каждая из которых соответствует определенному каналу и используется незавиоимо от остальных так, как было описано выше для одного канала. Пр и этом в каждой занятой ячейке -того канала указывается адрес предыдущей занятой ячейки этого же канала.

Информация для записи в запоминающее устройство и запросы на считывание из него могут поступать в любой последовательности по разл ичным каналам. Напр имер, эпюра приведенной выше памяти (V=10) после записи символов А, В, С, N по первому каналу и символов а, b, с, d по второму каналу, поступающ их к устройству в последовательности

ABabCcdN, приведена на фиг. 3, а: слева сверху изображен регистр 1, разбитый на две части (левая соответствует первому каналу, правая — второму), слева вн|изу — регистр 2.

В результате записи указанной последовательност и в стековое запоминающее устройство на регистре 1 слева стоит код адреса 8, справа—

7, на регистре 2 — код адреса 9. Эпюра этой же памятки после одного считывания по второму каналу и затем двух считываний по первому каналу пр иведена на фиг. 3, б, а эпюра этой памяти после одного считывания по второму каналу и затем запиои символов КМ по первому каналу приведена на рис. З,в.

Количество регистра 1 может быть сведено к одному, общему для всех и каналов, для этого в блоке 8 отводится и ячеек для хранения адреса последней занятой ячейками по каждому каналу, который считывается на регистр 4 и передается на регистр 1 прои подключении каждого канала. В конце работы t-го канала содержимое регистра 1 снова заносится в ту же фиксированную ячейку блока 8, адрес которой определяется номером канала.

Предмет изобретения

Стековое запоминающее устройство, содержащее блок памяти, выходной регистр и регистр адреса текущей свободной ячейками, отличающееся тем, что, с целью уменьшения объема памятки при многоканальной записи информации, в него введен дополнительный репистр для хранения адреса последней заня263677

5 той ячейки, соединенный выходным регистром .и регистром адреса текущей свободной ячейки, связанным непосредственно с выходным регистром. фыр.2 г

5

СК3 в

ro т г з

Ф

5 (8

8 гп o) у г з

6

8

18 г з

b

8 ю () г з ч (ч) 5

7 в (чД г з ч

) 5

6