Команда и логика для обеспечения функциональных возможностей цикла защищенного хеширования с шифром

Иллюстрации

Показать всеИзобретение относится к командам и логике для обеспечения функциональных возможностей цикла защищенного хеширования с шифром. Технический результат – обеспечение функциональных возможностей цикла защищенного хеширования с шифром. Процессор для обеспечения функциональных возможностей цикла защищенного хеширования с шифром содержит каскад декодирования для декодирования первой команды для выполнения алгоритма защищенного хеширования с шифром с использованием алгоритма стандарта тройного шифрования данных (TDES), причем первая команда указывает данные источника и один или более операндов-ключей, и один или более аппаратных исполняющих блоков, выполненных с возможностью в ответ на декодированную первую команду выполнения над данными источника первоначальной перестановки для генерирования подвергшихся перестановке данных источника, выполнения над подвергшимися перестановке данными источника одной или более циклических итераций алгоритма защищенного хеширования с шифром с использованием указанного одного или более операндов-ключей для генерирования зашифрованных данных, причем указанная одна или более циклических итераций составляют меньше 16, как указано первой командой, выполнения над зашифрованными данными перестановки, обратной первоначальной, и сохранения результата исполнения первой команды в регистре-адресате, причем первая команда указывает регистр-адресат с операндом регистра-адресата с одной командой и множеством данных (SIMD). 4 н. и 23 з.п. ф-лы, 27 ил.

Реферат

Область техники, к которой относится изобретение

Изобретение относится к области логики обработки данных, к микропроцессорам и связанной с ними структурой набора команд, которые при их исполнении посредством процессора или другой логики обработки данных выполняют логические, математические или другие функциональные операции. В частности, изобретение относится к командам и логике для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

Уровень техники

Хеш-функции могут использоваться для многих целей: например, для индексации данных в хеш-таблицах, для создания идентифицирующих характеристик, для балансировочного распределения нагрузки, для поиска данных в базах данных, для обнаружения дублированных данных или для однозначной идентификации файлов, и в качестве контрольных сумм для обнаружения случайного нарушения целостности данных. Например, в приложении к балансировочному распределению нагрузки, в хеш-алгоритме может использоваться в качестве основы для выбора сервера IP-адрес (адрес по межсетевому протоколу) клиента, или MAC-адрес (адрес по Протоколу управления доступом к передающей среде) клиента, или значение HTTP-заголовка (заголовка по Протоколу передачи гипертекста) и так далее. В таких приложениях один и тот же клиент может обслуживаться одним и тем же сервером, даже тогда, когда список располагаемых серверов изменен в течение сеанса связи с клиентом. Такого рода свойство может также сделать этот алгоритм полезным для приложений, которые требуют хранения информации о состоянии стороны сервера, таких как "cookies" (небольшой фрагмент данных о предыстории обращений данного пользователя к данному веб-серверу, автоматически создаваемый сервером на машине пользователя).

Термин "согласующееся хеширование" относится к способу распределения запросов между изменяющейся совокупностью Web-серверов. Каждое гнездо представлено узлом в распределенной системе. Добавление (подсоединения) и удаление (отключения/отказы) узлов требует переключения элементов, при котором количество гнезд/узлов изменяется. Хеш-функция может не сохранять структуру. В идеальном варианте для каждых входных данных вероятность получения любых из возможных выходных данных должна быть равной. Любые неравномерности в частотном распределении входных данных трансформируются в равномерное распределение выходных данных.

Однако могут иметь место проблемы как вследствие случайностей, так и по умыслу. В случае случайности пользователи могут состоять из различных групп, которым доступ к ресурсам требуется в различной степени. Если эти группы ненадлежащим образом сбалансированы, то пользователям, которых хеш-функция направляет на некоторый ресурс, доступ к ресурсам может требоваться в большей степени, чем другим пользователям. Этот некоторый ресурс в таком случае подвергается более высокой нагрузке, чем другие ресурсы, что приводит к смещению баланса нагрузки между ресурсами.

В случае умысла могут иметь место так называемые "хеш-атаки", которые предназначены для того, чтобы вызвать смещение баланса нагрузки между ресурсами. Хеш-атаки обычно делаются возможными действиями атакующих лиц, имеющих достаточное знание о системе, и/или атакующих лиц, использующих информацию, которая выводится из системы, содержащей ресурсы. Атакующие лица в таком случае заботятся о том, чтобы каждый запрос на ресурсы при прохождении хеш-функции направлялся на один и тот же ресурс. Этот ресурс в таком случае подвергается необычно высокой нагрузке и в таком случае функционирует более или менее неэффективно, что может в результате привести к так называемому "отказу в обслуживании", при котором ресурс не принимает более никаких пользователей. Этот отказ в обслуживании может оказывать воздействие на эффективность обслуживания всей системы.

Криптографическая хеш-функция представляет собой хеш-функцию, то есть алгоритм, который берет произвольный блок данных и возвращает битовую строку постоянного размера, (криптографическое) хеш-значение, таким образом, что (случайное или намеренное) изменение данных будет (с очень высокой вероятностью) изменять хеш-значение. Кодируемые данные часто называются "сообщением", а хеш-значение иногда называется профиль сообщения или "профиль".

Криптографические хеш-функции имеют много вариантов применения по защите информации, особенно в цифровых подписях, кодах аутентификации сообщений (MAC-кодах) и других формах аутентификации. Они могут также использоваться в качестве обыкновенных хеш-функций для индексации данных в хеш-таблицах, для для создания идентифицирующих характеристик, для обнаружения дублированных данных или для однозначной идентификации файлов, и в качестве контрольных сумм для обнаружения случайного нарушения целостности данных. В контекстах защиты информации криптографические хеш-значения иногда называются (цифровыми) "отпечатками пальцев", контрольными суммами или просто хеш-значениями, даже при том, что все эти термины представляют функции с довольно различными свойствами и целями.

Одна из наиболее известных криптографических хеш-функций представляет собой алгоритм MD5 (Алгоритм 5 "Сообщение - профиль"), разработанный Рональдом Райвестом (Ronald Rivest). Другие распространенные алгоритмы представляют собой SHA 1 (Алгоритм 1 защищенного хеширования), так же, как и его варианты SHA 2 и SHA 3, опубликованные Национальным институтом стандартов и технологии (институтом NIST (США)) в качестве Федерального стандарта США по обработке информации (FIPS-стандарта).

Если криптографическая хеш-функция основана на некоторой математической функции, то она все-таки может стать восприимчивой к атакам, имеющим целью отказ в обслуживании, в том, что при некоторых обстоятельствах она может стать подверженной одному закону из числа так называемых: "закона Ципфа (Zipfs)", "степенного закона" или "распределение Парето", при которых некоторый конкретный ресурс подвергается необычно высокой нагрузке. Это свойство или аналогичные свойства могут злонамеренно использоваться для того, чтобы вызвать смещение баланса нагрузки между ресурсами, приводящее к отказу в обслуживании.

Два важных компромисса в хеш-функциях для одного класса хеширования для выполнения поиска представляют собой: (1) сложность против скорости вычисления - слишком простая, и хеш-функция легко взламывается, слишком сложная, и хеш-функция слишком долго вычисляется; и (2) распределение профиля и лавинообразные свойства - изменение единственного бита во входных данных должно вызывать изменение n битов в выводимом значении хеш-профиля, самым сильным является случай, при котором n составляет приблизительно половину размера выводимого значения хеш-профиля.

Некоторыми предложены процессоры (например, в патенте США, имеющем номер 8255703) или сопроцессоры (например, в патенте США, имеющем номер 7240203), способные исполнять весь алгоритм защищенного хеширования. Один недостаток такого подхода заключается в том, что он не вписывается с легкостью в стандартный конвейер исполнения в современном микропроцессоре, если не уделить специальное внимание таким вопросам, как специальная обработка прерываний или одновременное суперскалярное исполнение других команд. Другое несоответствие со стандартными конвейерами исполнения заключается в задержке, требующейся для исполнения всего алгоритма защищенного хеширования.

Современные процессоры часто включают в себя команды для обеспечения операций, которые являются интенсивными в вычислительном отношении, но предлагают высокий уровень параллелизма данных, что может использоваться при эффективной реализации с использованием разнообразных устройств хранения данных, таких как, например, векторные регистры в технологии (SIMD) с одним потоком команд и многими потоками данных. Центральный процессор (CPU) может в таком случае предоставлять параллельные аппаратные средства для поддержки обработки векторов. Вектор представляет собой структуру данных, которая содержит некоторое количество последовательных элементов данных. Векторный регистр размера М может содержать N векторных элементов размера О, где N=М/О. Например, векторный регистр размером в 64 байта может быть разделен на: (а) 64 векторных элемента, при этом каждый элемент содержит порцию данных, которая занимает 1 байт; (b) 32 векторных элемента, содержащих порции данных, которые занимают 2 байта (или одно "слово") каждый; (с) 16 векторных элементов, содержащих порции данных, которые занимают 4 байта (или одно "двойное слово") каждый; или (d) 8 векторных элементов, содержащих порции данных, которые занимают 8 байтов (или одно "учетверенное слово") каждый. Природа параллелизма в векторных регистрах SIMD могла бы хорошо подходить для обработки алгоритмов защищенного хеширования.

До настоящего времени потенциальные решения для таких сложностей, несоответствий, проблем, ограничивающих производительность, и других критических вопросов не были надлежащим образом исследованы.

Краткое описание чертежей

Изобретение проиллюстрировано в порядке примера, а не ограничения, чертежами.

Фиг. 1A представляет собой структурную схему одного варианта воплощения системы, которая исполняет команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

Фиг. 1B представляет собой структурную схему другого варианта воплощения системы, которая исполняет команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

Фиг. 1C представляет собой структурную схему другого варианта воплощения системы, которая исполняет команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

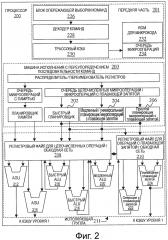

Фиг. 2 представляет собой структурную схему одного варианта воплощения процессора, который исполняет команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

На Фиг. 3A проиллюстрированы типы упакованных данных в соответствии с одним вариантом воплощения изобретения.

На Фиг. 3B проиллюстрированы типы упакованных данных в соответствии с одним вариантом воплощения изобретения.

На Фиг. 3C проиллюстрированы типы упакованных данных в соответствии с одним вариантом воплощения изобретения.

На Фиг. 3D проиллюстрировано кодирование команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующее одному варианту воплощения изобретения.

На Фиг. 3E проиллюстрировано кодирование команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующее другому варианту воплощения изобретения.

На Фиг. 3F проиллюстрировано кодирование команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующее другому варианту воплощения изобретения.

На Фиг. 3G проиллюстрировано кодирование команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующее другому варианту воплощения изобретения.

На Фиг. 3H проиллюстрировано кодирование команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром, соответствующее другому варианту воплощения изобретения.

На Фиг. 4A проиллюстрированы элементы одного варианта воплощения микроархитектуры процессора для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

На Фиг. 4B проиллюстрированы элементы другого варианта воплощения микроархитектуры процессора для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

Фиг. 5 представляет собой структурную схему одного варианта воплощения процессора для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

Фиг. 6 представляет собой структурную схему одного варианта воплощения вычислительной системы для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

Фиг. 7 представляет собой структурную схему другого варианта воплощения вычислительной системы для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

Фиг. 8 представляет собой структурную схему другого варианта воплощения вычислительной системы для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

Фиг. 9 представляет собой структурную схему одного варианта воплощения внутрикристальной системы для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

Фиг. 10 представляет собой структурную схему некоторого варианта воплощения процессора для исполнения команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

На Фиг. 11 проиллюстрирована структурная схема одного варианта воплощения системы разработки IP-ядра, которая обеспечивает функциональные возможности "среза" циклов защищенного хеширования в технологии SIMD (с одним потоком команд и многими потоками данных.

На Фиг. 12 проиллюстрирован один вариант воплощения системы эмуляции архитектуры, которая обеспечивает функциональные возможности "среза" циклов защищенного хеширования в технологии SIMD.

На Фиг. 13 проиллюстрирован один вариант воплощения системы для преобразования команд, которые обеспечивают функциональные возможности цикла защищенного хеширования с шифром.

На Фиг. 14 проиллюстрирована схема для одного варианта воплощения аппарата для исполнения команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

На Фиг. 15 проиллюстрирована схема для альтернативного варианта воплощения аппарата для исполнения команды для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

На Фиг. 16 проиллюстрирована блок-схема алгоритма для некоторого варианта воплощения процесса для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

На Фиг. 17 проиллюстрирована блок-схема алгоритма для другого варианта воплощения процесса для обеспечения функциональных возможностей цикла защищенного хеширования с шифром.

Детализированное описание

В нижеследующем описании раскрываются команды и логика обработки данных, обеспечивающие функциональные возможности цикла алгоритма защищенного хеширования с шифром. Некоторые варианты воплощения изобретения включают в себя процессор, содержащий: декодирующую стадию для декодирования команды для алгоритма защищенного хеширования с шифром, первую команду, указывающую данные источников, и один или более операндов-ключей. Исполняющие блоки процессора реагируют на декодированную команду, выполняя над данными источников одну или более циклических итераций алгоритма защищенного хеширования с шифром, используя эти один или более операндов-ключей, и сохраняют результат исполнения команды в регистре-адресате. В одном варианте воплощения команды указывают итерацию цикла алгоритма защищенного хеширования с шифром, использующую шифровальный алгоритм Файстела (Feistel), такой как DES (Стандарт шифрования данных) или TDES (Тройной DES). В альтернативных вариантах воплощения изобретения могут использоваться другие шифровальные алгоритмы, например, такие как Blowfish, SAFER (Защищенная и быстрая процедура шифрования) K - 64, CAST5 (разработанный Карлайлом Эдэмсом (Carlisle Adams) and и Стаффордом Тавэйрсом (Stafford Tavares)), FEAL (Алгоритм быстрого шифрования данных) и так далее. В одном варианте воплощения изобретения результат исполнения команды может быть использован при генерировании назначения ресурса из запроса для запросов на балансировку нагрузки по набору ресурсов обработки данных. В некоторых вариантах воплощения изобретения может указываться (например, в непосредственном операнде) диапазон номеров цикла для выполнения алгоритма защищенного хеширования с шифром. Например, в одном варианте воплощения шестнадцатеричный диапазон 0×0F в непосредственном байтовом операнде может указывать на то, что команда должна выполнить все шестнадцать (16) итераций алгоритма хеширования с шифром, тогда как шестнадцатеричный диапазон 0×FF в непосредственном байтовом операнде может указывать на то, что команда должна выполнить только одну итерацию цикла шестнадцать (16), или шестнадцатеричный диапазон 0×F8 в непосредственном байтовом операнде может указывать на то, что команда должна выполнить итерации: с цикла шестнадцать (16) по цикл девять (9), в режиме дешифрования алгоритма хеширования с шифром. Следует понимать, что одно неожиданное преимущество от использования шифра в качестве алгоритма хеширования, в противоположность однонаправленным алгоритмам хеширования, заключается в том, что он является обратимым, что может помочь с конструированием ключей для балансировки нагрузки, которые обеспечивают требуемые характеристики (например, стойкое и/или согласующееся хеширование), позволяя при этом введение новых ключей для воспрепятствования атаке (например, такой как атака с целью отказа в обслуживании). Другое неожиданное преимущество от выполнения в качестве алгоритма хеширования только указанного количества итераций шифра заключается в том, что для каждого цикла или диапазона циклических итераций могут быть использованы различные наборы ключей, что обеспечивает результаты шифрования, которые невозможны при использовании стандартной схемы с подключом.

Следует понимать, что команды для использования алгоритма защищенного хеширования с шифром, как в описанных здесь вариантах воплощения изобретения, могут быть использованы для обеспечения функциональных возможностей защищенного хеширования в приложениях, таких как приложения для обеспечения балансировочного распределения нагрузки и/или защиту от атак, имеющих целью отказ в обслуживании, и так далее, не требуя при этом чрезмерной сложности вычислений или неприемлемых времен задержки, но тем не менее предусматривая хорошо выбранные настройки для воспрепятствования атакам и вдобавок к этому не уменьшая требуемое качество обслуживания в этом процессе.

В нижеследующем описании для обеспечения более полного понимания вариантов воплощения изобретения приводятся многочисленные конкретные подробности, такие как логика обработки данных, типы процессоров, микроархитектурные условия, события, механизмы разблокирования и тому подобное. Специалисту в данной области техники следует, однако, понимать, что изобретение может быть осуществлено на практике и без таких конкретных подробностей. В дополнение к этому некоторые хорошо известные структуры, схемы и тому подобное не показаны подробно для того, чтобы избежать излишнего затруднения понимания вариантов воплощения изобретения.

Хотя нижеследующие варианты воплощения изобретения описаны в отношении процессора, другие варианты воплощения изобретения применимы к другим типам интегральных схем и логических устройств. Технологии и концепции, аналогичные вариантам воплощения изобретения, могут быть применены к другим типам схем или полупроводниковых устройств, которые могут выиграть от более высокой пропускной способности и повышенной производительности конвейера. Концепции вариантов воплощения изобретения применимы к любому процессору или машине, которая выполняет манипулирование данными. Однако изобретение не ограничено процессорами или машинами, которые выполняют операции над 512-разрядными, 256-разрядными, 128-разрядными, 64-разрядными, 32-разрядными или 16-разрядными данными и могут быть применены к любому процессору и машине, в которой выполняется манипуляция или управление данными. В дополнение к этому в нижеследующем описании приводятся примеры и на прилагаемых чертежах показаны разнообразные примеры для целей иллюстрации. Однако эти примеры не должны толковаться в ограничивающем смысле, поскольку они предназначены просто для того, чтобы дать примеры вариантов воплощения изобретения, а не дать исчерпывающий перечень всех возможных реализаций вариантов воплощения изобретения.

Хотя нижеприведенные примеры описывают обработку и распределение команд в контексте исполняющих блоков и логических схем, другие варианты воплощения изобретения могут быть реализованы посредством данных и/или команд, хранящихся на машиночитаемом, материальном носителе информации, которые при их выполнении машиной заставляют машину выполнять функции, согласующиеся с, по меньшей мере, одним вариантом воплощения изобретения. В одном варианте воплощения изобретения функции, связанные с вариантами воплощения изобретения, воплощены в исполняемых машиной командах. Эти команды могут быть использованы для того, чтобы заставлять универсальный или специализированный процессор, который запрограммирован посредством этих команд, выполнять этапы изобретения. Варианты воплощения изобретения могут быть предоставлены в виде компьютерного программного продукта или программного обеспечения, которое может включать в себя машиночитаемый или читаемый компьютером носитель информации, хранящий на себе команды, которые могут быть использованы для программирования компьютера (или других электронных устройств) на выполнение одной или более операций, соответствующих вариантам воплощения изобретения. В качестве альтернативы этапы вариантов воплощения изобретения могли бы быть выполнены специальными компонентами аппаратного обеспечения, которые содержат неперепрограммируемую логику для выполнения этапов, или любым сочетанием программируемых компьютерных компонентов и неперепрограммируемых компонентов аппаратного обеспечения.

Команды, используемые для программирования логики на выполнение вариантов воплощения изобретения, могут храниться в памяти в системе, такой как DRAM (динамичное оперативное запоминающее устройство), кэш, флэш-память или другое запоминающее устройство. Кроме того, эти команды могут быть распространены по сети или посредством других читаемых компьютером носителей информации. Таким образом, машиночитаемый носитель информации может включать в себя любой механизм для хранения или передачи информации в форме, читаемой машиной (например, компьютером), но не ограничен: гибкими магнитными дисками, оптическими дисками, компакт-диском, постоянным запоминающим устройством (CD-ROM (постоянными запоминающими устройствами на компакт-дисках)), и магнитооптическими дисками, постоянным запоминающим устройством (ROM-устройствами), оперативным запоминающим устройством (RAM), стираемым программируемым постоянным запоминающим устройством (EPROM), электрически стираемым программируемым постоянным запоминающим устройством (EEPROM), магнитными или оптическими картами, флэш-памятью или материальным, машиночитаемым запоминающим устройством, используемым при передаче информации по сети "Интернет" через электрические, оптические, акустические или другие формы распространяемых сигналов (например, несущие, инфракрасные сигналы, цифровые сигналы и так далее). Соответственно читаемый компьютером носитель информации включает в себя любой тип материального машиночитаемого носителя информации, подходящего для хранения или передачи электронных команд или информации в форме, читаемой машиной (например, компьютером).

Конструкция может проходить через различные стадии: от создания до моделирования и до изготовления. Данные, представляющие конструкцию, могут представлять конструкцию множеством способов. Сначала, что является полезным при моделировании, аппаратные средства могут быть представлены с использованием языка описания аппаратных средств или другого языка функционального описания. В дополнение к этому на некоторых стадиях процесса проектирования может быть выполнена модель уровня схем с логикой и/или элементами транзисторной логики. Кроме того, большинство конструкций на некоторой стадии достигают уровня данных, представляющих физическое размещение различных устройств в модели аппаратных средств. В случае, при котором используются традиционные технологии производства полупроводников, данные, представляющие модель аппаратных средств, могут представлять собой данные, указывающие на присутствие или отсутствие различных признаков на различных маскирующих слоях для фотошаблонов, используемых для производства интегральной схемы. В любом представлении конструкции данные могут храниться на любой форме машиночитаемого носителя информации. Память или магнитное или оптическое запоминающее устройство, такое как диск, могут являться этим машиночитаемым носителем информации, предназначенным для хранения информации, переданной посредством оптической или электрической волны, модулированной или иным образом сгенерированной для передачи такой информации. Когда осуществляется передача электрической несущей, указывающей или переносящей код или конструкцию, то в той мере, в какой выполняется копирование, буферизация или ретрансляция электрического сигнала, создается новая копия. Таким образом, поставщик услуг связи или поставщик сетевых услуг могут сохранить на материальном, машиночитаемом носителе информации, по меньшей мере, временно, некоторую вещь, такую как информация, закодированная в несущей, воплощающую технологии вариантов воплощения изобретения.

В современных процессорах множество различных исполняющих блоков используется таким образом, чтобы обрабатывать и исполнять разнообразие кода и команд. Не все команды созданы равными, поскольку некоторые завершаются более быстро, в то время как другие могут до своего завершения занять некоторое количество периодов тактовых импульсов. Чем выше пропускная способность для команд, тем лучше общая производительность процессора. Таким образом, было бы выгодно, чтобы как можно больше команд исполнялось настолько быстро, насколько это возможно. Однако существуют некоторые команды, которые имеют более высокую сложность и требуют большего в том, что касается времени исполнения и ресурсов процессора. Например, существуют команды на вычисления с плавающей запятой, операции загрузки/сохранения в памяти, перемещения данных и так далее.

По мере того, как все больше компьютерных систем используется в Интернет-приложениях, текстовых и мультимедийных приложениях, со временем вводилась дополнительная поддержка процессора. В одном варианте воплощения изобретения набор команд может быть связан с одной или более архитектурами компьютера, включающими в себя типы данных, команды, архитектуру регистров, способы адресации, архитектуру памяти, обработку прерываний и особых ситуаций и внешний ввод данных и вывод данных (I/O).

В одном варианте воплощения изобретения архитектура набора команд (ISA-архитектура) может быть реализована посредством одной или более микроархитектур, которые включают в себя логику и схемы процессора, используемые для реализации одного или более набора команд. Соответственно процессоры с различной микроархитектурой могут совместно использовать, по меньшей мере, часть общего набора команд. Например, процессоры Intel® Pentium 4, процессоры Intel® Core™ и процессоры от компании Advanced Micro Devices, Inc., Саннивейл, штат Калифорния, США, реализуют почти идентичные версии набора команд x86 (с некоторыми расширениями, которые были добавлены с более новыми версиями), но имеют различающиеся внутренние конструкции. Аналогичным образом, процессоры, сконструированные другими компаниями-разработчиками процессоров, такими как ARM Holdings, Ltd., MIPS, или их лицензиатами или последователями могут совместно использовать, по меньшей мере, часть общего набора команд, но могут включать в себя различающиеся конструкции процессора. Например, одна и та же архитектура регистров ISA-архитектуры может быть реализована различными способами в различных микроархитектурах с использованием новых или хорошо известных технологий, включая в себя выделенные физические регистры, один или более динамически распределяемых физических регистров, использующих механизм переименования регистров (например, с использованием таблицы альтернативных имен регистров (RAT-таблицы), переупорядочивающего буфера (ROB-буфера) и регистрового файла изъятия. В одном варианте воплощения изобретения регистры могут включать в себя один или более регистров, архитектур регистров, регистровых файлов или других наборов регистров, которые могут быть или могут не быть адресуемыми для разработчика программного обеспечения.

В одном варианте воплощения изобретения команда может включать в себя один или более форматов команды. В одном варианте воплощения изобретения формат команды может указывать различные поля (количество разрядов, место расположения разрядов, и так далее) для определения, среди прочего, операции, подлежащей выполнению, и операнда (операндов), над котором (которыми) должна быть выполнена эта операция. Некоторые форматы команд могут быть дополнительно подразделены по шаблонам команд (или подформатам). Например, шаблоны команд некоторого данного формата команды могут быть определены как имеющие различные подмножества полей формата команды и/или определены как имеющие некоторое данное поле, интерпретируемое различным образом. В одном варианте воплощения изобретения команда выражается с использованием формата команды (и, если это определено, в некотором заданном одном из шаблонов команды этого формата команды) и определяет или указывает операцию и операнды, которыми будет оперировать эта операция.

Научные, финансовые, универсальные автовекторизируемые приложения, RMS-приложения (приложения с распознаванием, разработкой и синтезом) и визуальные и мультимедийные приложения (например, двумерная/трехмерная графика, обработка изображений, сжатие видеоданных/восстановление сжатых видеоданных, алгоритмы распознавания речи и манипуляции аудиоданными) могут требовать, чтобы одна и та же операция выполнялась над большим количеством порций данных. В одном варианте реализации изобретения аббревиатура SIMD (с одним потоком команд и многими потоками данных) относится к типу команды, которая заставляет процессор выполнять операцию над множественными элементами данных. Технология SIMD может быть использована в процессорах, которые могут логически разделять разряды в регистре на некоторое количество элементов данных фиксированного размера или переменного размера, каждый из которых представляет отдельное значение. Например, в одном варианте воплощения изобретения разряды в 64-разрядном регистре могут быть организованы как операнд-источник, содержащий четыре отдельных 16-разрядных элемента данных, каждый из которых представляет отдельное 16-разрядное значение. Этот тип данных может именоваться как 'упакованный' тип данных или 'векторный' тип данных, и операнды этого типа данных именуются как операнды упакованных данных или векторные операнды. В одном варианте воплощения изобретения порция упакованных данных или вектор может представлять собой последовательность элементов упакованных данных, хранящихся в одном регистре, и операнд упакованных данных или векторный операнд может представлять собой операнд-источник или операнд-адресат в SIMD-команде (или 'команде с упакованными данными' или 'векторной команде'). В одном варианте воплощения изобретения SIMD-команда определяет отдельную векторную операцию, которая должна быть выполнена над двумя векторными операндами-источниками для того, чтобы сгенерировать векторный операнд-адресат (также именуемый как результирующий векторный операнд), имеющий тот же самый или другой размер, с тем же самым или другим количеством элементов данных и в том же самом или другом порядке следования элементов данных.

Технология SIMD, такая как та, что используется процессорами Intel® Core™, имеющими набор команд, включающий в себя команды х86, MMX™ (Мультимедийного расширения), расширения SIMD для потоковой обработки (SSE - расширений), SSE 2, SSE 3, SSE 4.1 и SSE 4.2, процессорами ARM, такими как семейство процессоров ARM Cortex®, имеющих набор команд, включающий в себя векторные команды с плавающей запятой (VFP - команды) и/или команды технологии NEON, и процессорами MIPS, такими как семейство процессоров Loongson, разработанных Институтом вычислительной техники (ICT) Китайской Академии Наук, сделала возможным значительное повышение производительности приложения (Core™ и ММХ™ представляют собой зарегистрированные товарные знаки или товарные знаки корпорации Intel Corporation, Санта-Клара, штат Калифорния, США).

В одном варианте воплощения изобретения термины "регистры/данные адресата и источника" представляют собой общие термины, представляющие источник и адресат соответствующих данных или операции. В некоторых вариантах воплощения изобретения они могут быть реализованы посредством регистров, памяти или других запоминающих областей, имеющих другие названия или функции, чем те, которые изображены. Например, в одном варианте реализации изобретения "DEST1" может представлять собой регистр временного запоминания или другую запоминающую область, тогда как "SRC1" и "SRC2" могут представлять собой первый и второй запоминающие регистры-источники или другую область памяти и так далее. В других вариантах воплощения изобретения две или более области из числа запоминающих областей SRC и DEST могут соответствовать различным элементам хранения данных в пределах одной и той же запоминающей области (например, SIMD - регистра). В одном варианте воплощения изобретения один из регистров-источников может также действовать в качестве регистра-адресата, например, при записи результата операции, выполненной над первыми и вторыми данными источников, в обратном направлении, в один из двух регистров - источников, служащий в качестве регистра-адресата.

Фиг. 1A представляет собой структурную схему приводимой в качестве примера вычислительной системы, сформированной с процессором, который включает в себя исполняющие блоки для исполнения команды в соответствии с одним вариантом воплощения изобретения. Система (100) включает в себя компонент, такой как процессор (102), для использования исполняющих блоков, включающих в себя логику для выполнения алгоритмов для обработки данных, в соответствии с изобретением, такой как в описанном здесь варианте воплощения изобретения. Система (100) является представителем систем обработки данных, основанных на микропроцессорах Pentium® III, Pentium® 4, Xeon™, Itanium®, XScale® и/или StrongARM™, поставляемых корпорацией Intel Corporation, Санта Клара, штат Калифорния, США, хотя могут также использоваться и другие системы (включающие в себя персональные компьютеры, имеющие другие микропроцессоры, инженерные рабочие станции, телевизионные абонентские приставки и тому подобное). В одном варианте воплощения изобретения приводимая в качестве примера система (100) может исполнять версию операционной системы WINDOWS®, поставляемой корпорацией Microsoft Corporation, г. Редмонд, Вашингтон, США, хотя могут также использоваться и другие операционные системы (например, UNIX и Linux), встроенное программное обеспечение и/или графические пользовательские интерфейсы. Таким образом, варианты воплощения изобретения не ограничены никаким конкретным сочетанием схем аппаратного обеспечения и программного обеспечения.

Варианты воплощения изобретения не ограничены компьютерными системами. Альтернативные варианты воплощения изобретения могут быть использованы в других устройствах, таких как карманные устройства, и встроенных вариантах применения. Некоторые примеры карманных устройств включают в себя сотовые телефоны, устройства связи по Интернет-протоколу, цифровые фотокамеры, персональные цифровые секретари (PDA) и карманные персональные компьютеры. Встроенные варианты применения могут включать в себя микроконтроллер, процессор цифровой обработки сигналов (DSP-процессор), внутрикристальную систему, сетевые компьютеры (NetPC (сетевые персональные компьютеры)), телевизионные абонентские приставки, сетевые концентраторы, коммутаторы глобальной сети (WAN) или любую другую систему, которая может выполнять одну или более команд в соответствии с, по