Дифференциальный усилитель с повышенным ослаблением синфазного сигнала

Иллюстрации

Показать всеИзобретение относится к области электроники и радиотехники. Технический результат: уменьшение коэффициента передачи входного синфазного сигнала. Технический результат достигается за счет новых элементов и связей, введенных в дифференциальный усилитель с повышенным ослаблением синфазного сигнала: второй (3) токовой выход входного дифференциального каскада (1) связан со входом второго (9) токового зеркала через первую (10) цепь согласования потенциалов, а четвертый (5) токовый выход входного дифференциального каскада (1) связан со входом первого (7) токового зеркала через вторую (11) цепь согласования потенциалов. 5 ил.

Реферат

Изобретение относится к области электроники и измерительной техники и может быть использовано в качестве устройства усиления сигналов различных датчиков, в структуре аналоговых микросхем, работающих в условиях синфазных помех.

Для работы в составе измерительных систем необходимы дифференциальные усилители сигналов различных сенсоров, обеспечивающие высокое ослабление синфазной составляющей двух входных напряжений.

В современной электронике широко применяются дифференциальные усилители (ДУ) с многоканальным входным каскадом, работающим на симметричную дифференциальную нагрузку на основе двух токовых зеркал [1-10]. Благодаря такому решению имеется потенциальная возможность существенного уменьшения коэффициента передачи синфазного сигнала (Ксф), которая, однако, не всегда реализуется.

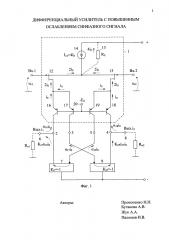

Ближайшим прототипом (фиг. 1) заявляемого устройства является дифференциальный усилитель по патенту US №1385255. Он содержит входной дифференциальный каскад 1, первый 2 и второй 3 синфазные друг с другом токовые выходы входного дифференциального каскада 1, третий 4 и четвертый 5 синфазные друг с другом токовые выходы входного дифференциального каскада 1, причем фазы выходных токов первого 2 и второго 3 токовых выходов входного дифференциального каскада 1 противоположны фазам выходных токов третьего 4 и четвертого 5 токовых выходов входного дифференциального каскада 1, первый 6 токовый выход устройства, связанный с первым 2 токовым выходом входного дифференциального каскада 1 и выходом первого 7 токового зеркала, второй 8 токовый выход устройства, связанный с третьим 4 токовым выходом входного дифференциального каскада 1 и выходом второго 9 токового зеркала, причем второй 3 токовый выход входного дифференциального каскада 1 связан со входом второго 9 токового зеркала, а четвертоый 5 токовый выход входного дифференциального каскада 1 связан со входом первого 7 токового зеркала.

Существенный недостаток известного ДУ состоит в том, что он характеризуется невысоким значением коэффициента ослабления входного синфазного сигнала

где Kd>>1 - дифференциальный коэффициент усиления ДУ;

Ксф<<1 - коэффициент передачи входного синфазного сигнала ДУ.

Основная задача предлагаемого изобретения состоит в уменьшении коэффициента передачи синфазного сигнала Ксф при неизменном Kd. В конечном итоге это повышает Кос.сф (1).

Поставленная задача достигается тем, что в дифференциальном усилителе (фиг. 1) входной дифференциальный каскад 1, первый 2 и второй 3 синфазные друг с другом токовые выходы входного дифференциального каскада 1, третий 4 и четвертый 5 синфазные друг с другом токовые выходы входного дифференциального каскада 1, причем фазы выходных токов первого 2 и второго 3 токовых выходов входного дифференциального каскада 1 противоположны фазам выходных токов третьего 4 и четвертого 5 токовых выходов входного дифференциального каскада 1, первый 6 токовый выход устройства, связанный с первым 2 токовым выходом входного дифференциального каскада 1 и выходом первого 7 токового зеркала, второй 8 токовый выход устройства, связанный с третьим 4 токовым выходом входного дифференциального каскада 1 и выходом второго 9 токового зеркала, причем второй 3 токовый выход входного дифференциального каскада 1 связан со входом второго 9 токового зеркала, а четвертый 5 токовый выход входного дифференциального каскада 1 связан со входом первого 7 токового зеркала, предусмотрены новые элементы и связи - второй 3 токовой выход входной дифференциального каскада 1 связан со входом второго 9 токового зеркала через первую 10 цепь согласования потенциалов, а четвертый 5 токовый выход входного дифференциального каскада 1 связан со входом первого 7 токового зеркала через вторую 11 цепь согласования потенциалов.

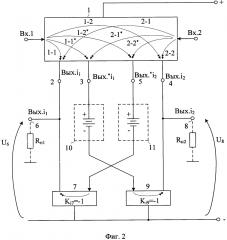

На фиг. 1 показана схема ДУ-прототипа, а на фиг. 2 - функциональная схема заявляемого ДУ в соответствии с формулой изобретения.

На фиг. 3 представлена схема заявляемого устройства с конкретным выполнением входного дифференциального каскада 1, который в данном случае соответствует входному каскаду ДУ-прототипа.

На фиг. 4 приведена схема заявляемого ДУ фиг. 2 в среде PSpice на моделях интегральных транзисторов АБМК_1.4 (ОАО «Интеграл», г. Минск).

На фиг. 5 представлена частотная зависимость коэффициента передачи синфазного сигнала Ксф схемы ДУ фиг. 4 от величины напряжений на цепях согласования потенциалов (10 и 11): Е10=Е11=V4=V6=vvar=5B и Е10=Е11=V4=V6=vvar=0B для случая, когда статическое напряжение на выходах 6 и 8 равно 5В.

Дифференциальный усилитель с повышенным ослаблением синфазного сигнала (фиг. 2) содержит входной дифференциальный каскад 1, первый 2 и второй 3 синфазные друг с другом токовые выходы входного дифференциального каскада 1, третий 4 и четвертый 5 синфазные друг с другом токовые выходы входного дифференциального каскада 1, причем фазы выходных токов первого 2 и второго 3 токовых выходов входного дифференциального каскада 1 противоположны фазам выходных токов третьего 4 и четвертого 5 токовых выходов входного дифференциального каскада 1, первый 6 токовый выход устройства, связанный с первым 2 токовым выходом входного дифференциального каскада 1 и выходом первого 7 токового зеркала, второй 8 токовый выход устройства, связанный с третьим 4 токовым выходом входного дифференциального каскада 1 и выходом второго 9 токового зеркала, причем второй 3 токовый выход входного дифференциального каскада 1 связан со входом второго 9 токового зеркала, а четвертый 5 токовый выход входного дифференциального каскада 1 связан со входом первого 7 токового зеркала. Второй 3 токовой выход входного дифференциального каскада 1 связан со входом второго 9 токового зеркала через первую 10 цепь согласования потенциалов, а четвертый 5 токовый выход входного дифференциального каскада 1 связан со входом первого 7 токового зеркала через вторую 11 цепь согласования потенциалов. Рассмотрим работу заявляемого ДУ (фиг. 2).

ДУ рассматриваемого класса характеризуется (благодаря высокой симметрии) потенциально высоким значением коэффициента ослабления входных синфазных сигналов. Однако на практике эти возможности не реализуются из-за влияния на Ксф напряжений Эрли выходных транзисторов входного дифференциального каскада 1.

Изменение входного синфазного сигнала на величину uc приводит к изменению тока iR0 общей истоковой цепи входного дифференциального каскада

Приращение данного тока iR0 передается в истоки транзисторов 12 и 13 и вызывает соответствующие приращения токов эмиттера i’ транзисторов 16 и 17 (18, 19):

При этом токи выходов 2, 4, 3, 5 и выходные токи первого 7 и второго 9 токовых зеркал:

В результате для первого 6 токового выхода устройства можно найти приращение тока в нагрузке Rн1, выходное напряжение uвых.6, а также коэффициент Ксф.6 для данного выхода:

Из последнего уравнения следует, что при выполнении условий

коэффициент передачи синфазного сигнала Ксф близок к нулю, что соответствует высоким значениям Кос.сф.

Однако на практике условие (16) не реализуется из-за неодинакового деления тока стока ic транзистора 12 (13) между эмиттерами транзисторов 16 и 17 (транзисторов 18, 19). Данный эффект обусловлен влиянием напряжения Эрли транзисторов 16 и 17 на данное перераспределение тока ic12 (ic13). На практике ток эмиттера и коллектора транзистора 17 (19) будет всегда больше, чем ток эмиттера и коллектора транзистора 16 (18). Это связано с более высоким уровнем напряжения коллектор-база транзисторов 17 (19) по сравнению с напряжением коллектор-база транзистора 16 (18). Как следствие, коэффициент Ксф в ДУ-прототипе получается небольшим.

Для уменьшения коэффициента Ксф в заявляемую схему вводятся цепи согласования потенциалов 10 и 11, которые выравнивают коэффициенты деления тока стока транзистора 12 (13) между эмиттерами транзисторов 16 и 17 (транзисторов 18 и 19). Это позволяет получить полную взаимную компенсацию токов от синфазного сигнала в цепи выходов 6 и 8. Данный вывод подтверждается результатами компьютерного моделирования, представленными на фиг. 5. За счет выбора параметров цепей согласования 10 и 11 коэффициент передачи синфазного сигнала предлагаемого ДУ уменьшается с -57 дБ до -198 дБ, т.е. более чем в несколько миллионов раз.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с прототипом по ослаблению синфазных сигналов.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент SU 1385255

2. Патент US 6.972.623, fig. 7

3. Патентная заявка US 2005/0285677, fig. 1

4. Патент US 4.417.292, fig. 1

5. Патент US 5.070.306, fig. 3

6. Патент US 5.955.922

7. Патент US 5.610.547, fig. 34

8. Патентная заявка US 2010/001797, fig. 3

9. Патентная заявка US 2014/0197888

10. Патент US 5.610.547, fig. 28

Дифференциальный усилитель с повышенным ослаблением синфазного сигнала, содержащий входной дифференциальный каскад, первый и второй синфазные друг с другом токовые выходы входного дифференциального каскада, третий и четвертый синфазные друг с другом токовые выходы входного дифференциального каскада, причем фазы выходных токов первого и второго токовых выходов входного дифференциального каскада противоположны фазам выходных токов третьего и четвертого токовых выходов входного дифференциального каскада, первый токовый выход устройства, связанный с первым токовым выходом входного дифференциального каскада и выходом первого токового зеркала, второй токовый выход устройства, связанный с третьим токовым выходом входного дифференциального каскада и выходом второго токового зеркала, причем второй токовый выход входного дифференциального каскада связан со входом второго токового зеркала, а четвертый токовый выход входного дифференциального каскада связан со входом первого токового зеркала, отличающийся тем, что второй токовой выход входного дифференциального каскада связан со входом второго токового зеркала через первую цепь согласования потенциалов, а четвертый токовый выход входного дифференциального каскада связан со входом первого токового зеркала через вторую цепь согласования потенциалов.