Загрузка парциальной ширины, зависящая от режима, в процессорах с регистрами с большим числом разрядов, способы и системы

Иллюстрации

Показать всеИзобретение относится к области загрузки данных из памяти в процессоры. Техническим результатом является повышение производительности процессорных систем за счет использования нескольких режимов для обработки инструкции загрузки парциальной ширины и/или ее кода операции. Процессор для загрузки данных содержит регистр, имеющий ширину; блок декодирования для приема инструкции загрузки парциальной ширины, причем инструкция загрузки парциальной ширины указывает ячейку памяти в качестве операнда источника и указывает регистр в качестве операнда назначения; подсистему памяти, соединенную с блоком декодирования, причем подсистема памяти предназначена для загрузки данных из указанной ячейки памяти в процессор, в ответ на инструкцию загрузки парциальной ширины; и блок записи в регистр, соединенный с подсистемой памяти и регистром, причем блок записи в регистр предназначен, в ответ на инструкцию загрузки парциальной ширины, для записи по меньшей мере части загруженных данных на парциальной ширине регистра и для завершения записи в регистр с набором разрядов, хранящихся на оставшейся ширине регистра, которые имеют значения разрядов, которые зависят от режима загрузки парциальной ширины процессора, при этом инструкция загрузки парциальной ширины не указывает режим загрузки парциальной ширины. 4 н. и 21 з.п. ф-лы, 17 ил.

Реферат

Область техники, к которой относится изобретение

Варианты осуществления, описанные здесь, относятся, в общем, к процессорам. В частности, варианты осуществления, описанные здесь, относятся, в общем, к загрузке данных из памяти в процессоры.

Уровень техники

Набор инструкций процессора обычно включает в себя множество различных типов инструкций, которые процессор может исполнить или выполнить. Например, набор инструкций может обычно включать в себя различные арифметические инструкции, различные логические инструкции, различные инструкции загрузки для загрузки данных из памяти в процессор и т.д.

Одна проблема состоит в том, что обычно ограничено число инструкций, которые могут быть включены в набор инструкций. Каждая инструкция может включать в себя код операции. Коды операций могут представлять собой части инструкций, которые используются для точного определения конкретных инструкций и/или операций, которые будут выполняться. Например, заданная инструкция загрузки данных из памяти может иметь заданный уникальный код операции для того, чтобы ее можно было отличить от других типов инструкций и разрешить процессору распознать ее. Код операции может представлять собой группу разрядов заданной длины в одном или более полях или позициях в пределах формата инструкции. Часто возникает ситуация, когда желательно поддерживать относительно маленьким число разрядов кодов операций, обеспечивая при этом желаемое число инструкций/операций. Длинные коды операций приводят к увеличению размера и/или сложности декодера. В дополнение, длинные коды операций приводят к увеличению общей длины инструкции, которая может заставить инструкции использовать больше пространства программы и занимать больше пространства в кэш-памяти. Число различных инструкций, которые можно однозначно идентифицировать с помощью заданной длины кода операции и/или длины инструкции, является часто ограниченным в большей степени, чем это желательно. Дополнительные инструкции обычно не могут постоянно добавляться в набор инструкций без окончательного исчерпания имеющихся кодов операций или увеличения длины инструкций в архитектурах с переменной длиной инструкций.

В некоторых случаях различные инструкции и/или операции могут иметь одинаковый код операции (или одинаковую часть кода операции), но могут включать в себя один или более дополнительных разрядов для того, чтобы можно было различать между собой различные версии инструкций и/или операций. Потенциальные недостатки этого метода состоят в том, что он может иметь тенденцию к увеличению длины инструкции или в некоторых случаях может отсутствовать доступный участок памяти в пределах длины инструкции для размещения дополнительного разряда (дополнительных разрядов), можно было различать между собой различные версии инструкций и/или операций.

Краткое описание чертежей

Настоящее изобретение можно будет лучше понять со ссылкой на последующее описание и сопроводительные чертежи, которые используются для иллюстрации вариантов осуществления. На чертежах:

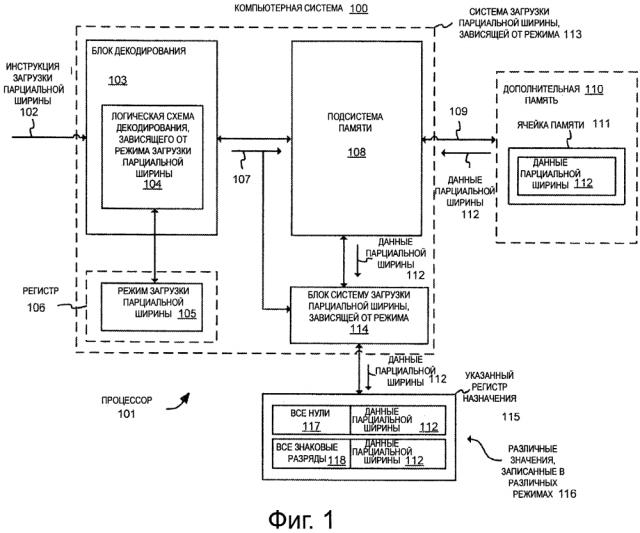

на фиг. 1 показана блок-схема варианта осуществления компьютерной системы, имеющей процессор для выполнения инструкции загрузки парциальной ширины;

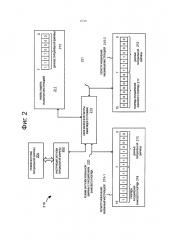

на фиг. 2 показана блок-схема первого примерного варианта осуществления операции загрузки парциальной ширины, которую можно выполнить согласно режиму загрузки парциальной ширины расширения знака или согласно режиму загрузки парциальной ширины с дополнением нулями;

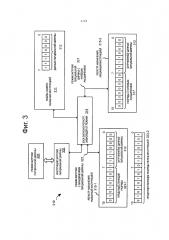

на фиг. 3 показана блок-схема второго примерного варианта осуществления операции загрузки парциальной ширины, которую можно выполнить согласно режиму загрузки с объединением парциальной ширины или согласно режиму загрузки парциальной ширины с дополнением нулями;

на фиг. 4 показана блок-схема последовательности операций варианта осуществления способа, который можно выполнить с помощью процессора при обработке инструкции загрузки парциальной ширины согласно варианту осуществления;

на фиг. 5 показана блок-схема варианта осуществления компьютерной системы, включающей в себя процессор с 64-разрядной архитектурой для выполнения 32-разрядной адресации памяти с дополнением нулями;

на фиг. 6 показана блок-схема варианта осуществления взаимодействия между программным модулем пользовательского уровня и модулем операционной системы для изменения режима загрузки парциальной ширины;

на фиг. 7 показана блок-схема варианта осуществления способа, который можно выполнить с помощью модуля операционной системы, привилегированного модуля или модуля другого уровня системы;

на фиг. 8А показана блок-схема, иллюстрирующая как примерный конвейер исполнения инструкций без изменения их очередности и примерное переименование регистров, так и конвейер выдачи/исполнения инструкций с изменением их очередности согласно вариантам осуществления изобретения;

на фиг. 8В показана блок-схема, иллюстрирующая как примерный вариант осуществления ядра архитектуры исполнения инструкций без изменения их очередности и примерное переименование регистров, так и ядро архитектуры выдачи/исполнения инструкций с изменением их очередности, которое будет включено в процессор, согласно вариантам осуществления изобретения;

на фиг. 9А показана блок-схема одного ядра процессора наряду с его подсоединением к сети межсоединений на кристалле и с его локальным подмножеством кэш-памяти 2-го уровня (L2) согласно вариантам осуществления изобретения;

на фиг. 9В показан расширенный вид части ядра процессора (фиг. 9А) согласно вариантам осуществления изобретения;

на фиг. 10 показана блок-схема процессора, который может иметь более одного ядро, может иметь встроенный контроллер памяти и может иметь встроенную графику согласно вариантам осуществления изобретения;

на фиг. 11 показана блок-схема системы в соответствии с одним вариантом осуществления настоящего изобретения;

на фиг. 12 показана блок-схема первой более конкретной примерной системы в соответствии с вариантом осуществления настоящего изобретения;

на фиг. 13 показана блок-схема второй более конкретной примерной системы в соответствии с вариантом осуществления настоящего изобретения;

на фиг. 14 показана блок-схема SoC в соответствии с вариантом осуществления настоящего изобретения; и

на фиг. 15 показана блок-схема, сопоставляющая использование программного конвертера инструкций для преобразования двоичных инструкций в наборе инструкций источника в двоичные инструкции в целевом наборе инструкций согласно вариантам осуществления изобретения.

Подробное описание изобретения

В некоторых вариантах осуществления процессор может иметь два или более режимов для обработки заданной инструкции и/или заданного кода операции двумя или более различными соответствующими способами, например, два или более режима для обработки загрузки парциальной ширины из инструкции памяти двумя или более различными соответствующими способами. В следующем описании изложены многочисленные конкретные детали (например, конкретные операции инструкций, конфигурации процессора, детали микроархитектуры, последовательности операций и т.д.). Однако варианты осуществления могут применяться на практике без этих конкретных деталей. В других случаях хорошо известные схемы, структуры и технологии не были показаны подробно во избежание усложнения понимания описания.

На фиг. 1 показана блок-схема варианта осуществления компьютерной системы 100. В различных вариантах осуществления компьютерная система может представлять собой настольный компьютер, портативный компьютер, компьютер типа "ноутбук", планшетный компьютер, нетбук, смартфон, персональный цифровой помощник, сотовый телефон, сервер, сетевое устройство (например, маршрутизатор или коммутатор), мобильное интернет-устройство (MID), медиапроигрыватель, интеллектуальный телевизор, телевизионную приставку, контроллер видеоигры или другой тип электронного устройства.

Компьютерная система включает в себя вариант осуществления процессора 101. В некоторых вариантах осуществления процессор может представлять собой процессор общего назначения. Например, процессор может представлять собой процессор общего назначения типа, который обычно используется в качестве центрального процессорного устройства (ЦПУ). В других вариантах осуществления процессор может представлять собой процессор специального назначения. Примеры подходящих процессоров специального назначения включают в себя, но не ограничиваются ими, сопроцессоры, графические процессоры, коммуникационные процессоры, сетевые процессоры, криптографические процессоры, встроенные процессоры и процессоры цифровых сигналов (DSPS), и это всего лишь несколько примеров. Процессор может представлять собой любой из различных процессоров с полным набором команд (CISC), различных процессоров с сокращенным набором команд (RISC), различных процессоров со сверхдлинным командным словом (VLIW), различных их гибридов или совершенно другие типы процессоров.

Компьютерная система также включает в себя вариант осуществления памяти 110. Память соединена с процессором 101 с помощью механизма 109 соединений или межсоединений. Примеры подходящих механизмов соединений или межсоединений включают в себя, но не ограничиваются ими, один или более межсоединений, шины, концентраторы, контроллеры памяти, наборы микросхем, компоненты набора микросхем и т.п. и различные их комбинации. Память может включать в себя один или более устройств памяти одинакового типа или различных типов. Одним широко используемым типом памяти, который подходит для вариантов осуществления, является динамическое запоминающее устройство (DRAM), хотя альтернативно можно использовать и другие типы памяти (например, флеш-память). Память может иметь программное обеспечение, которое хранится в ней, например, одну или более операционных систем (OS) и одну или более прикладных программ (не показаны). Во время работы инструкции программного обеспечения могут подаваться в процессор и исполняться процессором.

Как показано, инструкцию 102 загрузки парциальной ширины можно подавать в процессор 101.

Например, блок выборки (не показан) может осуществлять выборку инструкции загрузки парциальной ширины. Инструкция загрузки парциальной ширины может представлять собой инструкцию в кодах машины, инструкцию на языке ассемблера, макроинструкцию или сигнал управления ISA устройства. Инструкцию загрузки парциальной ширины можно однозначно определить (например, через одно или более полей или набор разрядов) или иным образом указать (например, неявно указать) ячейку 111 памяти в памяти 110 в качестве операнда источника, и позволяет точно определить или иным образом указать регистр 115 назначения в качестве операнда назначения, где должны быть сохранены данные 112 парциальной ширины, загруженные из памяти. Термин "данные парциальной ширины" используется в данном документе для обозначения заполнения данных или только парциальной ширины регистра 115 назначения, где должны храниться данные.

Процессор включает в себя блок 103 декодирования. Блок декодирования может также упоминаться как декодер или логическая схема декодирования. Блок декодирования может принимать инструкцию загрузки парциальной ширины. Блок декодирования может быть выполнен с возможностью декодирования инструкций относительно высокого уровня (например, инструкций машинного кода, инструкций на языке ассемблера, макроинструкций и т.д.) и вывода одной или более соответствующих инструкций относительно низкого уровня или сигналов управления (например, одной или более микроинструкций, микроопераций, точек ввода микрокода и т.д.). Инструкция(и) более низкого уровня или сигнал(ы) управления можно отобразить, представить и/или получить из инструкций относительно высокого уровня и позволяет реализовать инструкцию более высокого уровня через операцию(и) более низкого уровня (например, операции на уровне схемы или на уровне аппаратных средств). Блок декодирования можно реализовать с использованием всевозможных механизмов, включающих в себя, но не ограниченных ими, постоянные запоминающие устройства (ROM) микрокода, таблицы поиска, аппаратные реализации, программируемые логические матрицы (PLA), другие механизмы, которые используются для реализации известных в технике блоков декодирования и их комбинаций.

В других вариантах осуществления эмулятор, транслятор, трансформатор, интерпретатор или конвертер инструкций можно использовать вместо или в дополнение к блоку 103 декодирования. Конвертер инструкций может эмулировать, транслировать, трансформировать или иным образом преобразовывать инструкцию в одну или более полученные соответствующим образом инструкции или сигналы управления. Всевозможные типы таких конвертеров инструкций известны в технике, и их можно реализовать в виде аппаратных средств, программно-аппаратных средств, программного обеспечения или их комбинации. В некоторых вариантах осуществления конвертер инструкций может преобразовать принятую инструкцию более высокого уровня в одну или более инструкций промежуточного уровня, и блок декодирования может декодировать одну или более инструкций промежуточного уровня в одну или более инструкций более низкого уровня или сигналы управления, которые может выполнять собственная логическая схема процессора.

Как показано, блок декодирования является частью системы 113 загрузки парциальной ширины режима процессора. В некоторых вариантах осуществления два или более режимов можно использовать для обработки инструкции загрузки парциальной ширины и/или ее кода операции с помощью двух или более различных соответствующих способов. Преимущественно, это позволяет выполнять различные операции без необходимости использования дополнительного кода операции, что в некоторых случаях может быть затруднительно, как будет обсуждено в разделе "Уровень техники". Блок декодирования может быть связан с или иным образом поддерживать связь с режимом 105 загрузки парциальной ширины. В некоторых вариантах осуществления режим загрузки парциальной ширины может включать в себя один или более разрядов для указания одного из многочисленных различных режимов загрузки парциальной ширины. В другом аспекте можно использовать два или более разрядов для указания одного из двух, по меньшей мере трех, по меньшей мере четырех или дополнительно более чем четырех различных режимов загрузки парциальной ширины. В некоторых вариантах осуществления один или более разрядов можно сохранить в регистре 106 (например, в регистре управления, статуса или конфигурации) или другой ячейке памяти на кристалле. В качестве альтернативы, режим загрузки парциальной ширины можно дополнительно включить в один или более отдельных или изолированных разрядов необязательно в регистре управления, статуса или конфигурации. Как будет дополнительно объяснено ниже, программный модуль (например, модуль приложения пользовательского уровня, модуль операционной системы, модуль монитора виртуальной машины, привилегированный программный модуль и т.п.) может изменять режим 105 загрузки парциальной ширины (например, путем изменения одного или более разрядов) на режим, который является подходящим, желаемым или предназначенным для инструкции 102 загрузки парциальной ширины (например, программное обеспечение, использующее инструкцию загрузки парциальной ширины).

Блок декодирования и/или процессор могут осуществлять доступ к режиму загрузки парциальной ширины для определения того, какой используется текущий режим загрузки парциальной ширины, и блок декодирования может декодировать инструкцию загрузки парциальной ширины согласно определенному режиму загрузки парциальной ширины. В некоторых вариантах осуществления режим загрузки парциальной ширины можно использовать для обеспечения различных значений, интерпретации и/или операций для инструкции загрузки парциальной ширины и/или ее кода операции. В некоторых вариантах осуществления блок декодирования может включать в себя логическую схему 104 декодирования, зависящего от режима загрузки парциальной ширины, для декодирования инструкции загрузки парциальной ширины таким способом, который зависит от, базируется на и/или согласуется с текущим режимом загрузки парциальной ширины, связанным с инструкцией (например, с режимом во время декодирования инструкции). Например, первый набор из одной или более инструкций или сигналов управления можно декодировать из инструкции загрузки парциальной ширины в первом режиме загрузки парциальной ширины, тогда как второй другой набор из одной или более инструкций или сигналов управления можно декодировать из инструкции загрузки парциальной ширины (например, того же самого кода операции) во втором другом режиме загрузки парциальной ширины. Инструкции или сигналы 107 управления, которые зависят от режима, можно выводить из блока декодирования в соответствии с текущим режимом 105.

В некоторых вариантах осуществления инструкцию загрузки парциальной ширины нельзя точно определить или иным образом указать режим 105 загрузки парциальной ширины (например, могут отсутствовать разряды инструкции для выбора или для различения многочисленных различных разновидностей инструкций/операций или точного определения режима иным образом). Это обычно помогает избежать увеличения длины инструкции, позволяет потенциально использовать технологию, где длина инструкции не разрешает такие дополнительные разряды, позволяет потенциально уменьшить или ограничить число разрядов, которые необходимо декодировать, или предлагает другие потенциальные преимущества. В некоторых вариантах осуществления может возникнуть ситуация, когда невозможно определить из опроса любого или всех разрядов инструкции загрузки парциальной ширины то, какой режим загрузки парциальной ширины использовать.

Как показано на фиг.1, подсистема 108 памяти соединена с блоком 103 декодирования и с памятью 110. Подходят различные традиционные подсистемы памяти, известные в технике. Подсистема памяти может приводиться в действие в ответ на и/или в результате подачи инструкции 102 загрузки парциальной ширины (например, в ответ на одну или более декодированных инструкций или сигнала(ов) управления, соответствующих текущему режиму 105 загрузки парциальной ширины), чтобы загрузить данные из указанной ячейки 111 памяти в процессор. Как упоминалось ранее, инструкция загрузки парциальной ширины позволяет точно определить или иным образом указать ячейку 111 памяти, имеющую 112 данные парциальной ширины. Инструкция загрузки парциальной ширины позволяет также точно определить или иным образом указать регистр 115 назначения, где хранятся данные парциальной ширины.

Согласно варианту осуществления блок 114 записи в регистр, зависящий от режима загрузки парциальной ширины, соединен с блоком 103 декодирования, с подсистемой 108 памяти и с регистром 115 назначения. Для простоты блок записи в регистр, зависящей от режима загрузки парциальной ширины может также упоминаться просто как блок записи в регистр, зависящей от режима, или блок записи в регистр. Блок записи в регистр, зависящей от режима, может приводиться в действие в ответ на и/или в результате инструкции 102 загрузки парциальной ширины (в ответ на одну или более декодированных инструкций или сигналов 107 управления, соответствующих текущему режиму 105 загрузки парциальной ширины), для записи или получения доступа иным образом к регистру 115, чтобы иметь результат, сохраненный в нем, который зависит от и/или соответствует режиму загрузки парциальной ширины. В некоторых вариантах осуществления блок записи в регистр, зависящей от режима, можно приводить в действие для записи по меньшей мере части загруженных данных 112 парциальной ширины на парциальной ширине регистра и можно приводить в действие для окончания или завершения записи в регистр набора разрядов 117, 118, которые хранятся на оставшейся ширине регистра, которые имеют значения разрядов, которые зависят от и/или соответствуют соответствующему режиму загрузки парциальной ширины. Блок записи в регистр, зависящей от режима, и/или процессор может включать в себя специфическую или конкретную логику (например, схему или другие аппаратные средства, возможно объединенные с одним или более программно-аппаратными средствами и/или программным обеспечением), реагирующую на инструкцию загрузки парциальной ширины.

Для различных вариантов осуществления подходят разные комбинации различных типов режимов загрузки парциальной ширины. Примеры включают в себя, но не ограничиваются ими, режим загрузки парциальной ширины с расширением знакового разряда, режим загрузки парциальной ширины с дополнением нулями, режим загрузки с объединением парциальной ширины и другие режимы загрузки парциальной ширины, известные в технике. В режиме загрузки парциальной ширины с расширением знакового разряда знаковый разряд данных парциальной ширины (например, самый старший двоичный разряд, имеющий значение двоичного нуля или двоичной единицы) можно копировать, расширять или иным образом сохранять или записывать на оставшейся ширине регистра, не занятого данными парциальной ширины. В режиме загрузки парциальной ширины с дополнением нулями двоичные нули можно вставлять, расширять или иным образом сохранять или записывать на оставшейся ширине регистра, не занятого данными парциальной ширины. В режиме загрузки с объединением парциальной ширины данные парциальной ширины можно объединить с исходными или предсуществующими разрядами или данными, уже сохраненными в регистре во время записи в регистр. Эти исходные или предсуществующие данные нельзя изменять или перезаписывать. Например, режим загрузки с объединением парциальной ширины позволяет хранить парциальную ширину в части самого младшего разряда регистра, перезаписывая исходные или предсуществующие данные в этой части самого младшего разряда, и позволяет хранить исходные или предсуществующие данные в оставшейся части самого старшего разряда регистра. В различных вариантах осуществления можно использовать комбинацию из двух этих или других типов режимов загрузки парциальной ширины. Различные соответствующие значения 116 можно записывать в регистр назначения в различных режимах. В иллюстрированном примере в режиме загрузки парциальной ширины с дополнением нулями данные 112 парциальной ширины могут быть включены в часть регистра назначения (например, половина самого младшего разряда или другая часть), и все нули 117 можно хранить в другой части регистра назначения (например, в части самого старшего разряда). В режиме загрузки парциальной ширины с расширением знакового разряда данные 112 парциальной ширины могут быть включены в часть регистра назначения (например, в половину самого младшего разряда или другую часть), и знаковые разряды 118 (например, основанные на самом старшем двоичном разряде данных 112 парциальной ширины) можно хранить в другой части регистра назначения (например, в половине самого старшего разряда или в другой части). В других вариантах осуществления можно использовать другие типы или комбинации различных загрузок парциальной ширины. Например, в другом варианте осуществления режим загрузки с объединением и расширением парциальной ширины (например, смотри фиг. 3), или другой тип режима загрузки парциальной ширины можно использовать вместо одного из проиллюстрированных режимов или в качестве дополнительного третьего типа режима загрузки парциальной ширины.

Процессор 101 был описан и показан в упрощенном виде во избежание излишнего усложнения описания и концепций. Устройство может включать в себя различные другие известные компоненты, которые обычно используются в процессорах. Примеры таких компонентов включают в себя, но не ограничиваются ими, блок предсказания ветвлений, блок выборки инструкции, кэш-память данных и инструкций, кэш-память второго или более высокого уровня, буферы предварительной выборки для трансляции данных и инструкций, буферы предварительной выборки, очереди для микроинструкций, планировщики последовательностей микроинструкций, блок переименования регистра, блок планирования инструкций, блоки шинного интерфейса, блок отмены инструкции, другие компоненты, включенные в процессоры, и различные их комбинации. В процессорах существуют в прямом смысле многочисленные различные комбинации и конфигурации компонентов, и варианты осуществления не ограничены какой-либо конкретной комбинацией или конфигурацией.

На фиг. 2 показана блок-схема первого примерного варианта осуществления операции 219 загрузки парциальной ширины, который можно выполнить согласно режиму 220 загрузки парциальной ширины расширения знака или согласно режиму 221 загрузки ZAJQ11 X ширины с дополнением нулями. Операцию загрузки парциальной ширины можно выполнить в ответ на инструкцию 202 загрузки парциальной ширины и режим 20 5 ассоциируемой загрузки парциальной ширины (например, режим загрузки парциальной ширины в то время, когда декодируется инструкция загрузки парциальной ширины).

Инструкция загрузки парциальной ширины позволяет точно определить или иным образом указать ячейку памяти 211 в качестве операнда источника и позволяет точно определить или иным образом указать регистр 215 назначения в качестве операнда назначения. Ячейка памяти хранит данные парциальной ширины, которые будут загружаться в регистр назначения в ответ на инструкцию загрузки парциальной ширины. Для простоты иллюстрации показаны только данные 212 парциальной ширины с 8-разрядной шириной. В иллюстрированном примере 8-разрядные данные парциальной ширины имеют, от позиции старшего значащего разряда слева до позиции младшего значащего разряда справа, значения "11110000". Однако следует понимать, что эти значения являются только примерами, и можно альтернативно использовать любые другие возможные значения разрядов. Более того, в других вариантах осуществления, вместо данных парциальной ширины с 8-разрядной шириной, данные парциальной ширины могут иметь другую ширину (например, 16 разрядов, 32 разряда, 64 разряда и т.д.). Аналогичным образом, для простоты иллюстрации иллюстрированный регистр назначения имеет ширину 16 разрядов. В других вариантах осуществления регистр назначения может иметь другую ширину (например, 32 разряда, 64 разряда, 128 разрядов и т.д.). В некоторых вариантах осуществления, как и в этом примере, данные парциальной ширины могут иметь половину ширины регистра назначения, хотя это и не требуется. В других вариантах осуществления, например, данные парциальной ширины могут иметь 16 разрядов, и регистр назначения может иметь 64 разряда, или данные парциальной ширины могут иметь 8 разрядов, и регистр назначения может иметь 32 разряда и т.д. В качестве другого примера, данные парциальной ширины могут иметь 64 разряда, и регистр назначения может иметь 128 разрядов.

Блок 214 записи в регистр, зависящей от режима, соединен с регистром 215 назначения, соединен с ячейкой памяти 211 и связан с 202 инструкцией загрузки парциальной ширины (например, соединен с блоком декодирования). Блок записи в регистр может приводиться в действие в ответ на инструкцию загрузки парциальной ширины, чтобы выполнить запись или сохранение в регистре назначения. Способ, с помощью которого выполняется запись или сохранение, может зависеть от или базироваться на режиме загрузки парциальной ширины, связанном с инструкцией загрузки парциальной ширины. В этом первом примерном варианте осуществления режим загрузки парциальной ширины позволяет указать любой из режима 220 загрузки парциальной ширины с расширением знакового разряда (слева на иллюстрации) или режим 221 загрузки парциальной ширины с дополнением нулями (справа на иллюстрации). В обеих из этих различных типов загрузок парциальной ширины данные 212 парциальной ширины (например, 8-разрядные данные парциальной ширины в этом примере) можно записать или сохранить в регистре назначения. В иллюстрированном варианте осуществления загруженные данные парциальной ширины записываются в части самого младшего разряда регистра назначения, хотя это не требуется. Как показано, в любом режиме 220 загрузки парциальной ширины с расширением знакового разряда или режиме 221 загрузки парциальной ширины с дополнением нулями значения "11110000" 8-разрядных данных парциальной ширины можно сохранить в разрядах [7:0] регистра 215-1, 215-2 назначения. В других вариантах осуществления можно использовать другие размеры данных парциальных ширин, и/или данные парциальной ширины можно записать в другие части/позиции регистра назначения (например, в старшую значащую часть и т.д.).

В иллюстрированном варианте осуществления часть самого старшего разряда (например, 8-разрядная часть самого старшего разряда в этом примере) регистра назначения обрабатывается различным образом для двух различных типов операций/режимов загрузки парциальной ширины. Для режима 220 загрузки парциальной ширины с расширением знакового разряда блок записи в регистр, зависящей от режима, управляет записью или сохранением знаковых разрядов 218 (например, знаковый разряд самого старшего двоичного разряда данных парциальной ширины) во всех оставшихся более значащих разрядах регистра 215-1 назначения, который не используется для хранения данных парциальной ширины. В иллюстрированном примере разряд 7 представляет собой знаковый разряд или старший значащий разряд данных парциальной ширины. В этом примере знаковый разряд представляет собой двоичную единицу, и, соответственно, двоичная единица 218 хранится в каждом из разрядов [15:8] регистра 215-1 назначения. Для режима 221 загрузки парциальной ширины с дополнением нулями блок записи в регистр, зависящей от режима, управляет записью и сохранением всех нулей 217 во всех оставшихся более значащих разрядах регистра 215-2 назначения, который не используется для хранения данных парциальной ширины. Как показано, двоичные нули 217 можно хранить в каждом из разрядов [15:8] регистра 215-2 назначения. Соответственно, блок записи в регистр, зависящей от режима и/или процессор может закончить запись в регистр 215 назначения с разрядами (например, 217 или 218), которые хранятся в его части, которая не используется для хранения данных парциальной ширины (например, все более значащие разряды, чем часть самого младшего разряда, который используется для хранения данных парциальной ширины), которые имеют значения разрядов, которые зависят от режима загрузки парциальной ширины.

На фиг. 3 показана блок-схема второго примерного варианта осуществления операции 319 загрузки парциальной ширины, которую можно выполнить согласно режиму 322 загрузки с объединением парциальной ширины или режиму 321 загрузки парциальной ширины с дополнением нулями. Этот второй примерный вариант осуществления имеет некоторые общие черты с ранее описанным первым примерным вариантом осуществления (фиг. 2). Во избежание излишнего усложнения описания сначала будут описаны различные дополнительные функции и характеристики второго примерного варианта осуществления без повторения всех сходных элементов. Однако следует понимать, что признаки и характеристики, описанные выше для первого примерного варианта осуществления (фиг. 2), можно также дополнительно применить ко второму примерному варианту осуществления.

Операцию 319 загрузки парциальной ширины можно выполнить в ответ на инструкцию 302 загрузки парциальной ширины и связанный режим 305 загрузки парциальной ширины. Инструкция загрузки парциальной ширины позволяет точно определить или иным образом указать ячейку памяти 311 в качестве операнда источника и позволяет точно определить или иным образом указать регистр назначения 315 в качестве операнда назначения. Ячейка памяти хранит данные 312 парциальной ширины, которые будут загружаться в регистр назначения в ответ на инструкцию загрузки парциальной ширины. Для простоты иллюстрации в этом примере показаны 8-разрядные данные парциальной ширины и 16-разрядный регистр назначения, хотя объем изобретения этим не ограничивается.

Блок 314 записи в регистр, зависящей от режима, может приводиться в действие в ответ на инструкцию загрузки парциальной ширины, чтобы выполнить запись или сохранение в регистре назначения. Способ, с помощью которого выполняется запись или сохранение, может зависеть от или базироваться на режиме загрузки парциальной ширины, связанном с инструкцией загрузки парциальной ширины. В этом втором примерном варианте осуществления режим загрузки парциальной ширины позволяет указать один из: режима 322 загрузки с объединением или объединенной парциальной шириной (слева на иллюстрации) или режима 321 загрузки парциальной ширины с дополнением нулями (справа на иллюстрации). В обоих из этих различных типов загрузок парциальной ширины данные 312 парциальной ширины (например, 8-разрядные данные парциальной ширины в этом примере) можно записать или сохранить в регистре назначения. В иллюстрированном варианте осуществления загруженные данные парциальной ширины записываются в части самого младшего разряда регистра назначения, хотя это не требуется. Как показано, в режиме 322 загрузки с объединением или объединенной парциальной шириной или режиме 321 загрузки парциальной ширины с дополнением нулями, значения "11110000" 8-разрядных данных парциальной ширины можно сохранить в разрядах [7:0] регистра 315-1, 315-2 назначения. В других вариантах осуществления можно использовать другие размеры данных парциальной ширины, и/или данные парциальной ширины можно записать в другой части/позиции регистра назначения (например, в старшей значащей части и т.д.).

В иллюстрированном варианте осуществления часть самого старшего разряда (например, 8-разрядная часть самого старшего разряда в этом примере) регистра 215 назначения обрабатывается различным образом для двух различных типов операций/режимов загрузки парциальной ширины. В режиме 322 загрузки с объединением или объединенной парциальной шириной управление блоком записи в регистр, зависящей от режима, осуществляется таким образом, чтобы завершить запись в регистр назначения 315-1 с разрядами 323-1, которые хранятся в его части, которая не используется для хранения данных парциальной ширины (например, все более значащие разряды, чем 8 разрядов самого младшего разряда, который используется для хранения 8-разрядных данных парциальной ширины), которые имеют значения разрядов, которые зависят от режима загрузки парциальной ширины. Например, как показано, блок записи в регистр может завершить запись регистра 315-1 назначения с исходным набором разрядов (то есть те разряды, которые были первоначально в регистре 315-1 назначения перед инструкцией загрузки парциальной ширины), которые хранятся в оставшейся 8-разрядной части самого значащего разряда регистра 315-1 назначения. Для ссылки показан набор 323-2 значений предсуществующих разрядов, которые существовали перед выполнением инструкции парциальной записи в регистр. Разряды [15:8] предсуществующих значений 323-2 разрядов имеют значения "01010101". Следует отметить, что эти одинаковые значения "01010101" в разрядах [15:8] значений 323-2 разрядов, которые существовали перед выполнением инструкции парциальной записи в регистр, также появляются в качестве тех же самых значений разрядов "01010101" в разрядах [15:8] регистра 315-2 назначения после выполнения инструкции парциальной записи в регистр. Данные парциальной ширины можно объединить или вставить в регистр назначения вместо некоторых разрядов, при этом оставляя другие разряды неизменными. В режиме 321 загрузки парциальной ширины с дополнением нулями управление блоком записи в регистр, зависящей от режима, осуществляется таким образом, чтобы записать или сохранить все нули 317 во всех оставшихся более значащих разрядах регистра назначения 315-2, которые не используются для хранения данных парциальной ширины. Как показано, двоичные нули 317 могут храниться в каждом из разрядов [15:8] регистра назначения 315-2.

Следует понимать, что в качестве примера подходящих типов режимов загрузки парциальной ширины представлено всего лишь несколько иллюстративных вариантов осуществления. Рассмотрен д