Цифроаналоговый преобразователь

Иллюстрации

Показать всеИзобретение относится к средствам обработки информации и может быть использовано при создании высокоскоростных функциональных цифроаналоговых и аналого-цифровых преобразователей и преобразователей частоты. Технический результат заключается в расширении арсенала средств того же назначения. В заявленном цифроаналоговом преобразователе, содержащем весовые двоично-взвешенные сопротивления 1 и аналоговые ключи 2, причем управляющие входы аналоговых ключей 2 соединены с соответствующими цифровыми управляющими выходами цифрового регистра 5, к точке объединения весовых двоично-взвешенных сопротивлений 1 подключены источник опорного тока Io 6 и вход повторителя напряжения 7, при этом аналоговые выходы аналоговых ключей 2 соединены с общей шиной схемы. 2 ил.

Реферат

Изобретение относится к измерительной технике, автоматике и схемотехнике сопряжения цифровых и аналоговых сигналов в электронных схемах обработки информации и может быть использовано при создании простых высокоскоростных функциональных цифроаналоговых и аналого-цифровых преобразователей небольшой разрядности, в схемах преобразования частоты следования низкочастотных сигналов в напряжение в различных тахометрических и подобных им устройствах в области геофизического приборостроения, а также в схемах, требующих мгновенного вычисления функции 1/х.

Из существующего уровня техники широко известен классический параллельный цифроаналоговый преобразователь с использованием весовых двоично-взвешенных сопротивлений и аналоговых ключей, управляемых входным цифровым двоичным кодом (см. «Управляющие ЭВМ и комплексы. Раздел: Программно-технические комплексы (ПТК)», Доцент каф. ИУ-1 Суханов Владимир Александрович, материалы к лекциям, гл. 3.2, рис. 3.1, http://iul.my1.ru/_fr/0/_3_2011.pdf). Данное техническое решение принято в качестве прототипа.

Функциональная схема цифроаналогового преобразователя-прототипа приведена на фиг. 1 (см. прототип).

Принятые обозначения:

1 - n весовых двоично-взвешенных сопротивлений,

2 - n аналоговых ключей (S(0) - S(n-l)),

3 - источник опорного напряжения Uo,

4 - выходной суммирующий каскад на операционном усилителе,

5 - цифровой регистр.

Схема содержит n весовых двоично-взвешенных сопротивлений 1, n ключей (S(0) - S(n-l)) 2, управляемых входным цифровым двоичным кодом D = (d(n-1), d(n-2), … d(1), d(0)) с выхода n-разрядного цифрового регистра 5, источник 3 опорного напряжения Uo и выходной суммирующий каскад 4 на операционном усилителе. Одни концы весовых двоично-взвешенных сопротивлений 1 объединены в общую точку. К этой же точке подключен источник опорного напряжения Uo 3. Другие концы весовых двоично-взвешенных сопротивлений 1 подключены к аналоговым входам аналоговых ключей 2. Аналоговые выходы аналоговых ключей 2 присоединены к суммирующей шине, что обеспечивает параллельное соединение весовых двоично-взвешенных сопротивлений 1. Управляющие входы аналоговых ключей 2 соединены с соответствующими выходами цифрового регистра 5.

Схема работает следующим образом.

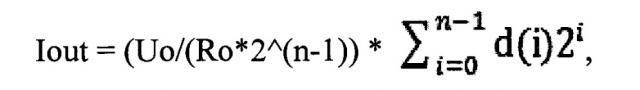

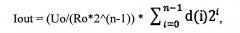

Каждый i-й ключ аналоговых ключей 2 подключает соответствующее сопротивление весовых двоично-взвешенных сопротивлений 1 к суммирующей шине цифроаналогового преобразователя, когда значение d(i) = 1, и отключает его от нее, когда значение d(i) = 0. Сопротивления Ri весовых двоично-взвешенных сопротивлений 1 таковы, что обеспечивается пропорциональность протекающего в них тока двоичному весу соответствующего разряда входного цифрового двоичного кода. При этом i = 1, 2, …, (n-1), где Ro - сопротивление самого старшего значащего разряда d(n-1) (наименьшее по величине), сопротивление следующего равно 2*Ro и т.д. до сопротивления в младшем значащем разряде, значение которого равно В точку объединения весовых двоично-взвешенных сопротивлений 1 подается опорное напряжение Uo от источника 3 опорного напряжения. Выходной ток в суммирующей шине цифроаналогового преобразователя при этом определяется соотношением

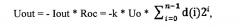

а напряжение на выходе схемы -

где

d(i) = 0 или 1 - значение i-го значащего разряда входного цифрового двоичного кода.

Roc - сопротивление обратной связи.

Недостатком описанного цифроаналогового преобразователя-прототипа является невозможность преобразования входного цифрового двоичного кода в аналоговую величину, обратно-пропорциональную значению этого кода.

Техническим результатом изобретения является возможность преобразования входного цифрового двоичного кода в аналоговую величину, обратно-пропорциональную значению этого кода.

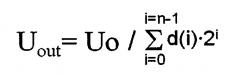

Технический результат достигается тем, что цифроаналоговый преобразователь, содержащий n весовых двоично-взвешенных сопротивлений, одни концы которых объединены, а другие подключены к аналоговым входам n аналоговых ключей, причем управляющие входы n аналоговых ключей соединены с соответствующими цифровыми управляющими n выходами цифрового регистра, к точке объединения n весовых двоично-взвешенных сопротивлений подключены источник опорного тока Io и вход повторителя напряжения, при этом аналоговые выходы n аналоговых ключей соединены с общей шиной схемы, а напряжение на выходе повторителя напряжения определяется выражением

где:

- падение напряжения на сопротивлении самого младшего значащего разряда цифроаналогового преобразователя,

Io - ток источника опорного тока,

Ro - сопротивление самого старшего значащего разряда цифроаналогового преобразователя,

n - разрядность цифроаналогового преобразователя,

d(i) = 0 или 1 - значение i-го значащего разряда входного цифрового двоичного кода.

Функциональная схема заявленного цифроаналогового преобразователя представлена на фиг. 2. Принятые обозначения:

1 - n весовых двоично-взвешенных сопротивлений,

2 - n аналоговых ключей (S(0) - S(n-1)),

5 - цифровой регистр.

6 - источник опорного тока Iо,

7 - повторитель напряжения.

Схема содержит n весовых двоично-взвешенных сопротивлений 1, n ключей (S(0) - S(n-l)) 2, управляемых входным цифровым двоичным кодом D = (d(n-1), d(n-2), … d(1), d(0)) с выхода n-разрядного цифрового регистра 5, источник 6 опорного тока Io и повторитель 7 напряжения.

Схема работает следующим образом.

Одни концы весовых двоично-взвешенных сопротивлений 1 подключены к аналоговым входам аналоговых ключей 2, управляемых входным цифровым двоичным кодом с цифрового регистра 5. Другие концы весовых двоично-взвешенных сопротивлений 1 объединены в общую точку. Каждый i-й разряд цифрового регистра 5 управляет ключом Si аналоговых ключей 2, который подключает Ri весовых двоично-взвешенных сопротивлений 1 к общей шине схемы, когда значение d(i) = 1, и отключает его, когда значение d(i) = 0. Сопротивления Ri весовых двоично-взвешенных сопротивлений 1 таковы, что обеспечивается обратная пропорциональность падения напряжения на них двоичному весу соответствующего разряда входного цифрового двоичного кода. При этом i = 1, 2, …, (n-1), где Ro - сопротивление самого старшего значащего разряда d(n-1) (наименьшее по величине), сопротивление следующего равно Ro*2 и т.д. до сопротивления в младшем значащем разряде, значение которого равно В точку объединения весовых двоично-взвешенных сопротивлений 1 подается опорный ток Io от источника 6 опорного тока. В качестве результата преобразования при этом используется падение напряжения на суммарной проводимости весовых двоично-взвешенных сопротивлений 1. Это напряжение подается на выход схемы через повторитель 7 напряжения на операционном усилителе. Суммарная проводимость параллельно включенных весовых двоично-взвешенных сопротивлений 1 определяется следующим соотношением:

или через проводимости,

где Go = 1/Ro,

или

или

или

Напряжение на выходе ОУ с учетом (1) определяется соотношением:

или в окончательном виде

где

- падение напряжения на сопротивлении самого младшего значащего разряда цифроаналогового преобразователя,

Io - ток источника опорного тока,

Ro - сопротивление самого старшего значащего разряда цифроаналогового преобразователя,

n - разрядность цифроаналогового преобразователя,

d(i) = 0 или 1 - значение i-го значащего разряда входного цифрового двоичного кода.

Таким образом, достигается заявленный технический результат, заключающийся в возможности преобразования входного цифрового двоичного кода в аналоговую величину, обратно-пропорциональную значению этого кода.

Цифро-аналоговый преобразователь, содержащий n весовых двоично-взвешенных сопротивлений, одни концы которых объединены, а другие подключены к аналоговым входам n аналоговых ключей, причем управляющие входы n аналоговых ключей соединены с соответствующими цифровыми управляющими n выходами цифрового регистра, отличающийся тем, что к точке объединения n весовых двоично-взвешенных сопротивлений подключены источник опорного тока Io и вход повторителя напряжения, при этом аналоговые выходы n аналоговых ключей соединены с общей шиной схемы, а напряжение на выходе повторителя напряжения определяется выражением

где Uo=Io*Ro*2^(n-1) - падение напряжения на сопротивлении самого младшего значащего разряда цифроаналогового преобразователя,

Io - ток источника опорного тока,

Ro - сопротивление самого старшего значащего разряда цифроаналогового преобразователя,

n - разрядность цифроаналогового преобразователя,

d(i)=0 или 1 - значение i-го значащего разряда входного цифрового двоичного кода.