Процессоры, способы и системы для осуществления доступа к набору регистров либо как к множеству малых регистров, либо как к объединенному большому регистру

Иллюстрации

Показать всеГруппа изобретений относится к области вычислительной техники и может быть использована для осуществления доступа к регистрам в процессорах. Техническим результатом является уменьшение занимаемой регистрами площади на кристалле. Процессор содержит набор физических регистров, каждый из которых выполнен с возможностью хранения упакованных данных; исполняющее звено, сопряженное с набором физических регистров, причем исполняющее звено выполнено с возможностью доступа к набору физических регистров по меньшей мере двумя различными методами в ответ на команды, причем указанные по меньшей мере два различных метода включают в себя первый метод, в котором набор физических регистров представляет множество N-разрядных логических регистров; и второй метод, в котором набор физических регистров представляет один логический регистр по меньшей мере из 2N разрядов, причем указанные по меньшей мере 2N разрядов составляют по меньшей мере 256 разрядов, при этом каждая из команд содержит код операции и выделенное поле, отличающееся от кода операции, для указания метода осуществления доступа исполняющим звеном к набору физических регистров для указанной команды. 4 н. и 19 з.п. ф-лы, 20 ил., 35 пр.

Реферат

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Область техники, к которой относится изобретение

Описываемые здесь варианты воплощения изобретения, в общем, относятся к процессорам. В частности, описываемые здесь варианты воплощения изобретения, в общем, относятся к использованию регистров в процессорах.

Информация о предшествующем уровне техники

Многие процессоры имеют архитектуры с одним потоком команд и многими потоками данных (SIMD - архитектуры). В SIMD - архитектурах команда обработки упакованных данных (данных в упакованном формате), векторная команда или SIMD - команда могут оперировать множественными элементами данных (например, множественными парами элементов данных) одновременно (например, параллельно). Процессор может иметь аппаратное обеспечение для параллельного исполнения, отвечающее на команду обработки упакованных данных таким образом, что одновременно (например, параллельно) выполняет множественные операции.

Множественные элементы данных могут быть упакованы в пределах регистров или ячеек памяти как упакованные данные. В упакованных данных разряды регистров или других мест хранения информации могут быть логически разделены на последовательность элементов данных. Например, регистр для упакованных данных с разрядностью в 64 разряда может иметь два упакованных 32-разрядных элемента данных, четыре упакованных 16-разрядных элемента данных или восемь упакованных 8 - разрядных элементов данных.

В некоторых процессорах за эти годы имело место прогрессирующее увеличение разрядности операндов, состоящих из упакованных данных. Это увеличение разрядности операндов, состоящих из упакованных данных, вообще говоря, позволяет одновременно (например, параллельно) обрабатывать большее количество элементов данных, что, вообще говоря, ведет к повышению производительности. Например, в случае, когда используются 128-разрядные упакованные данные, одновременно может обрабатываться восемь 16-разрядных элементов данных вместо только четырех 16-разрядных элементов данных в случае 64-разрядных упакованных данных.

Однако один возможный недостаток такого использования упакованных данных с более высокой разрядностью заключается в возможном соответствующем увеличении размера регистров и регистровых файлов. Например, увеличение разрядности каждого регистра из набора 64-разрядных регистров, такое чтобы они каждый были 128-разрядными регистрами, вероятно, приблизительно удвоит размер регистров (например, площадь или занимаемое место, занимаемые регистрами на кристалле). Влияние этого, вероятно, будет даже больше в тех вариантах реализации, в которых физических регистров реализовано больше, чем архитектурных регистров, поскольку приблизительно удвоиться может размер большего количества регистров. Другой возможный недостаток такого рода увеличения размера регистров и регистровых файлов заключается в соответствующем увеличении количества данных (например, о состоянии или контексте), которые необходимо помещать в эти регистры и извлекать из них при переключениях контекста, сохранениях состояний в режимах электропитания и подобных переходах. Например, для каждого регистра может потребоваться помещать в него и извлекать из него 128 разрядов в случае регистра с разрядностью в 128 разрядов вместо только 64 разрядов в случае регистра с разрядностью в 64-разряда.

Краткое описание чертежей

Изобретение можно лучше всего понять, обратившись к нижеследующему описанию и прилагаемым к нему чертежам, которые используются для того, чтобы проиллюстрировать варианты воплощения изобретения. На чертежах:

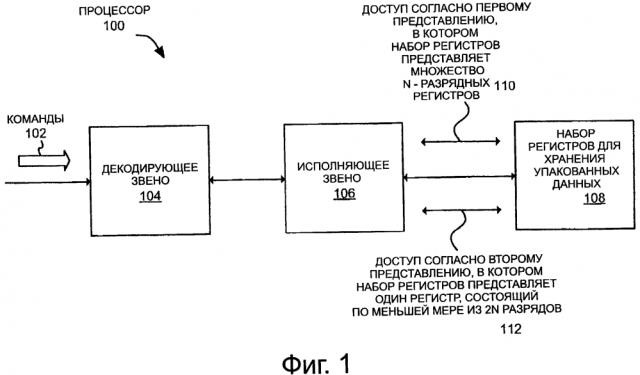

Фиг. 1 представляет собой блок-схему блок-схему одного варианта воплощения процессора.

Фиг. 2 представляет собой блок-схему алгоритма одного варианта воплощения способа, выполняемого в процессоре и/или посредством процессора.

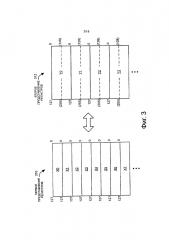

Фиг. 3 представляет собой блок-схему варианта воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 128-разрядным регистрам для упакованных данных - на первом представлении, и как к 256-разрядным регистрам для упакованных данных - на втором представлении.

Фиг. 4 представляет собой блок-схему варианта воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 64-разрядным регистрам для упакованных данных - на первом представлении, как к 128-разрядным регистрам для упакованных данных - на втором представлении, и как к 256-разрядным регистрам для упакованных данных - на третьем представлении.

Фиг. 5 представляет собой блок-схему варианта воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 128-разрядным регистрам для упакованных данных - на первом представлении, как к 256-разрядным регистрам для упакованных данных - на втором представлении, и как к 512-разрядным регистрам для упакованных данных - на третьем представлении.

Фиг. 6 представляет собой блок-схему варианта воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 255-разрядным регистрам для упакованных данных - на первом представлении, и как к 512-разрядным регистрам для упакованных данных - на втором представлении.

Фиг. 7А-С представляют собой блок-схемы вариантов воплощения подходящих форматов команды для использования различных представлений набора регистров.

Фиг. 7D представляют собой блок-схемы примеров подходящих форматов упакованных данных.

Фиг. 8А представляет собой блок-схему, на которой проиллюстрированы как приводимый в качестве примера конвейер без переупорядочения последовательности команд, так и приводимый в качестве примера конвейер с переименованием регистров, переупорядочиванием последовательности выдачи/исполнения команд, соответствующие вариантам воплощения изобретения.

Фиг. 8В представляет собой блок-схему, на которой проиллюстрированы как приводимый в качестве примера вариант воплощения ядра, имеющего архитектуру без переупорядочения последовательности команд, так и приводимое в качестве примера ядро, имеющее архитектуру с переименованием регистров, переупорядочиванием последовательности выдачи/исполнения команд, подлежащие включению в состав процессора, соответствующего вариантам воплощения изобретения.

Фиг. 9А представляет собой блок-схему одиночного ядра процессора наряду с его соединением с расположенной на кристалле сетью межсоединений и с его локальным подмножеством кэша уровня 2 (L2), соответствующих вариантам воплощения изобретения.

Фиг. 9В представляет собой расширенное представление части ядра процессора, показанного на Фиг. 9А, соответствующего вариантам воплощения изобретения.

Фиг. 10 представляет собой блок-схему процессора, который может иметь больше чем одно ядро, может иметь интегрированный контроллер памяти и может иметь интегрированные графические средства, соответствующего вариантам воплощения изобретения.

На Фиг. 11 показана блок-схема системы в соответствии с одним вариантом воплощения настоящего изобретения.

На Фиг. 12 показана блок-схема первой более конкретной системы, приводимой в качестве примера, в соответствии с одним вариантом воплощения настоящего изобретения.

На Фиг. 13 показана блок-схема второй более конкретной системы, приводимой в качестве примера, в соответствии с одним вариантом воплощения настоящего изобретения.

На Фиг. 14 показана блок-схема внутрикристальной системы (SoC) в соответствии с одним вариантом воплощения настоящего изобретения.

Фиг. 15 представляет собой блок-схему, на которой сравнивается использование конвертора команд, реализованного программными средствами, для того, чтобы конвертировать двоичные команды в некотором исходном наборе команд в двоичные команды в некотором заданном наборе команд в соответствии с вариантами воплощения изобретения.

Подробное описание вариантов осуществления изобретения

Здесь раскрываются процессоры, способы и системы, которые позволяют рассматривать или осуществлять доступ к набору регистров либо как к множеству относительно малых регистров, либо как к единому относительно большому регистру. В нижеследующем описании, излагаются многочисленные конкретные подробности (например, конкретные емкости регистров, количества регистров, команды и форматы, варианты реализации логики, конфигурации процессора, микроархитектурные подробности, последовательности операций, подробности разделения и интеграции логики и так далее). Однако следует понимать, что варианты воплощения изобретения могут быть осуществлены на практике без этих конкретных подробностей. В других случаях, хорошо известные схемы, конструкции и технологии не показаны подробно во избежание затруднения понимания этого описания.

Фиг. 1 представляет собой блок-схему блок-схему одного варианта воплощения процессора (100). Этот процессор представляет аппарат для обработки команд, который может быть приведен в действие для обработки команд. В некоторых вариантах воплощения изобретения, этот процессор может представлять собой универсальный процессор (например, универсальный микропроцессор, относящийся к типу, часто используемому в качестве центрального процессора (CPU) в настольном компьютере, переносном компьютере и подобных им компьютерах). В качестве альтернативы, этот процессор может представлять собой процессор специального назначения. Примеры подходящих процессоров специального назначения включают в себя: сетевые процессоры, процессоры передачи данных, криптографические процессоры, графические процессоры, сопроцессоры, встроенные процессоры, процессоры цифровой обработки сигналов (DSP - процессоры) и контроллеры (например, микроконтроллеры), в качестве лишь нескольких примеров, но не ограничены ими. Процессор может представлять собой любой процессор из числа: разнообразных процессоров для вычислений со сложным набором команд (CISC - процессоров), разнообразных процессоров для вычислений с сокращенным набором команд (RISC - процессоров), разнообразных процессоров с командными словами сверхбольшой длины (VLIW - процессоров), разнообразных гибридов этих процессоров или других типов процессоров без каких бы то ни было исключений.

Процессор также включает в себя набор регистров (108). Каждый из регистров может представлять находящееся на процессоре и/или на кристалле место хранения информации. В некоторых вариантах воплощения изобретения, этот набор регистров может представлять регистры для упакованных данных или иным образом могут быть способны к хранению упакованных данных, векторных данных или данных для архитектуры с одним потоком команд и многими потоками данных (SIMD - данных). Регистры для упакованных данных могут быть реализованы различными методами в различных микроархитектурах с использованием хорошо известных технологий и не ограничены никаким конкретным типом схемы или механизма. Подходящими являются всевозможные различные типы регистров. Примеры подходящих типов регистров включают в себя: выделенные физические регистры, динамически распределяемые физические регистры с использованием переименования регистров и их сочетания, но не ограничены этим.

Процессор может принимать команду (102), которая указывает по меньшей мере один регистр, реализованный на наборе (108) регистров на или иным образом с ним связанный. Эта команда может представлять команду в машинном коде, команду на языке ассемблера, макрокоманду или управляющий сигнал набора команд процессора. Эта команда может явным образом специфицировать (например, посредством некоторого набора разрядов или одного или более полей), или иным образом указывать (например, неявно указывать) этот по меньшей мере один регистр (например по меньшей мере один исходный операнд и/или операнд - адресат (для занесения результата)). В качестве одного примера, команда может специфицировать единственный используемый регистр в качестве исходного операнда, и этот единственный регистр либо может также использоваться в качестве операнда - адресата, либо команда может дополнительно специфицировать отличный от него операнд - адресат. В качестве другого примера, команда может специфицировать некоторый первый регистр, используемый в качестве первого исходного операнда, и некоторый второй регистр, используемый в качестве второго исходного операнда, и один из этих регистров, специфицированных для исходных операндов, либо может также использоваться в качестве операнда-адресата, или команда может дополнительно специфицировать отличный от них операнд-адресат. Это только несколько иллюстративных примеров. Объем изобретения не ограничен конкретным типом команды, если эта команда указывает по меньшей мере один регистр, связанный с этим набором регистров. Примеры подходящих типов команд включают в себя: команды арифметических операций над упакованными данными (например, команды сложения упакованных данных, команды умножения упакованных данных и так далее), команды логических операций над упакованными данными (например, команды циклического сдвига упакованных данных, команды сдвига упакованных данных, команды сравнения упакованных данных, команды операции "логическое ИЛИ" над упакованными данными и так далее), команды доступа к памяти, относящиеся к упакованным данным, (например, команды сбора данных, команды на разнесение данных и так далее), в качестве лишь нескольких примеров, но не ограничены ими.

Процессор включает в себя звено (104) декодирования команд. Звено (104) декодирования команд может также упоминаться как декодирующее звено, декодер или декодирующая логика. Декодирующее звено может принимать и декодировать команды относительно более высокого уровня (например, команды в машинном коде, команды на языке ассемблера, макрокоманды), и выводить одну или более команд относительно более низкого уровня или управляющие сигналы (например, микрокоманды, микрооперации, точки входа в микрокод), которые отражают, представляют команды более высокого уровня и/или выведены из них. Эти одна или более команд более низкого уровня или управляющие сигналы могут реализовывать команду более высокого уровня посредством одной или более операций более низкого уровня (например, уровня схемы или уровня аппаратного обеспечения). Декодирующее звено может быть реализовано с использованием всевозможных различных механизмов, включающих в себя: постоянные запоминающие устройства для микрокода (ROM-устройства), таблицы поиска, аппаратные варианты реализации, программируемые логические матрицы (PLA-матрицы) и другие механизмы, используемые для реализации декодирующих звеньев, известные в данной области техники, но не ограниченных этими механизмами. В других вариантах воплощения изобретения, вместо декодирующего звена или в дополнение к нему могут быть использованы эмулятор, транслятор, блок трансформации, интерпретатор команд или другая логика конвертирования команд.

Вновь обратимся к Фиг. 1, на которой с декодирующим модулем (104) и с набором (108) регистров сопряжено исполняющее звено (106). В качестве примера, это исполняющее звено может включать в себя: арифметическое устройство, логическое устройство, арифметико-логическое устройство (ALU), цифровую схему или логику для того, чтобы выполнять арифметические и логические операции, исполняющее звено для памяти, или тому подобное. Исполняющее звено может принимать одну или более декодированных или иначе конвертированных команд или один или более управляющих сигналов, которые представляют команду (102) и/или выведены из нее. Исполняющее звено и/или процессор могут специальную или особую логику (например, транзисторы, схемы или другое аппаратное обеспечение, возможно, объединенное с микропрограммным обеспечением (например, командами, хранящимися в энергонезависимой памяти) и/или программным обеспечением), которая способна функционировать таким образом, чтобы выполнять операции в ответ на команду (102) (например, в ответ на одну или более команд или один или более управляющих сигналов, декодированных или иным образом выведенных из команды (102)).

В некоторых вариантах воплощения изобретения, исполняющее звено способно функционировать в ответ на команду (102) и/или в ее результате таким образом, чтобы осуществлять доступ к набору (108) регистров либо в одном, либо в обоих по меньшей мере из двух различных методов (доступа) или представлений регистров. В некоторых вариантах воплощения, эти, по меньшей мере два различных метода или представления могут включать в себя некоторый первый метод или представление (110), в котором набор (108) регистров должны рассматриваться в качестве множества N-разрядных регистров или иным образом представлять это множество. В некоторых вариантах воплощения изобретения, эти по меньшей мере два различных пути или представления могут включать в себя некоторый второй метод или представление (112), в котором этот набор регистров должны рассматриваться в качестве единого регистра, состоящего из по меньшей мере 2N разрядов или иным образом представлять этот регистр. В некоторых вариантах воплощения изобретения, эти по меньшей мере 2N разрядов могут представлять собой по меньшей мере 256 разрядов. В других вариантах воплощения изобретения, этот набор регистров может представлять собой N-разрядные регистры (например, 128-разрядные регистры, 256-разрядные регистры и так далее). В некоторых вариантах воплощения изобретения, этот набор регистров может представлять собой N/2 - разрядные регистры (например, 64-разрядные регистры, 128-разрядные регистры и так далее).

В качестве одного конкретного примера, набор (108) регистров может состоять из двух N-разрядных регистров (например, 128-разрядных регистров). В первом методе или представлении (110), эти два N-разрядных регистра (например, 128-разрядных регистра) могут рассматриваться в качестве двух N-разрядных (например, 128-разрядных) регистров или иным образом представлять эти регистры. Во втором методе или представлении (112), эти два N-разрядных регистра (например, 128-разрядные регистры) могут рассматриваться в качестве единого регистра, состоящего по меньшей мере из 2N разрядов (например, 256 разрядов, 512 разрядов и так далее) или иным образом представлять этот регистр. В некоторых вариантах воплощения изобретения, может иметься больше, чем только два различных представления или метода осуществления доступа к набору (108) регистров. Например, в некоторых вариантах воплощения изобретения, может иметься три, четыре или больше чем четыре различных метода осуществления доступа или представления набора (108) регистров. Например, в некоторых вариантах воплощения изобретения, в этом примере может дополнительно поддерживаться осуществление доступа к набору регистров как к четырем N/2-разрядным регистрам (например, 64-разрядным регистрам).

В качестве другого конкретного примера, набор (108) регистров может состоять из четырех N/2-разрядных регистры (например, 64-разрядных регистров). В первом методе или представлении (110), эти четыре N/2-разрядных регистра (например, 64-разрядных регистра) могут рассматриваться в качестве двух N-разрядных (например, 128-разрядных) регистров или иным образом представлять эти регистры. Во втором методе или представлении (112), эти четыре N/2-разрядных регистра (например, 64-разрядных регистра) могут рассматриваться в качестве единого регистра, состоящего по меньшей мере из 2N-разрядов (например, 256 разрядов, 512 разрядов, 1024 разрядов и так далее) или иным образом представлять этот регистр. В некоторых вариантах воплощения изобретения, может иметься по меньшей мере третий метод осуществлять доступ к набору (108) регистров. Например, в некоторых вариантах воплощения изобретения, во втором представлении (112) исполняющее звено может рассматривать четыре N/2 - разрядных регистра (например, 64-разрядных регистра) или осуществлять к ним доступ как к единому регистру, состоящему по меньшей мере из 4N-разрядов (например, 512 разрядов, 1024 разрядов и так далее), и процессор может дополнительно поддерживать осуществления доступа или представление набора (108) регистров в качестве множества 2N-разрядных регистров (например, из 256 разрядов).

В некоторых вариантах воплощения изобретения, в каждом из представлений набора (108) регистров и/или методов осуществления доступа к набору (108) регистров, рассматриваемые или подвергающиеся доступу регистры для упакованных данных, могут быть видимыми для программного обеспечения и/или программиста и/или могут быть специфицированы командами из набора команд (например, макрокомандами, командами в машинном коде, командами на языке ассемблера и так далее) для идентификации операндов. Иногда регистры, специфицированные командами из набора команд, упоминаются в данных областях техники как архитектурно видимые регистры или архитектурные регистры, которые противопоставляются другим неархитектурным или архитектурно невидимым регистрам в некоторой заданной микроархитектуре (например, регистрам временного хранения, используемым для осуществления команды и так далее).

Как было показано в этих детализированных примерах, в некоторых вариантах воплощения изобретения, процессор может быть способным функционировать таким образом, чтобы распознавать, рассматривать и/или осуществлять доступ к набору (108) регистров либо как к множественным относительно малым регистрам (например, N-разрядным регистрам), или как к единому относительно большому регистру (например, регистру, имеющему по меньшей мере 2N разрядов). Например, в некоторых вариантах воплощения изобретения, смежная пара регистров может рассматриваться по отдельности в качестве 128-разрядные регистры или может быть логически "объединена" вместе и рассматриваться вся вместе как единый 256-разрядный регистр. Те же самые физические регистры и то же самое физическое суммарное количество разрядов могут входить в состав как этих двух 128-разрядных регистров, так и в единый 256-разрядный регистр, но они могут рассматриваться различными методами. Полезно, что в некоторых вариантах воплощения изобретения, такого рода подход может быть использован для того, чтобы избежать необходимости повышения разрядности этих регистров, в то же самое время позволяя все-таки повысить разрядность регистра для упакованных данных и/или разрядность операнда, состоящего из упакованных данных. Избегание повышения разрядности этих регистров может помочь избежать, или по меньшей мере уменьшить некоторые из возможных недостатков, упомянутых в разделе "Предшествующий уровень техники", например, увеличения площади или занимаемого места регистров на кристалле и/или увеличения количества данных, которое необходимо помещать в регистры и извлекать из них при переключениях контекста. В некоторых вариантах воплощения изобретения, такого рода подход может быть использован для реализации регистров для упакованных данных или операндов, состоящих по меньшей мере из 256 разрядов (например, 256 разрядов, 512 разрядов, 1024 разрядов и так далее), по причине чего вышеупомянутые возможные недостатки имеют тенденцию становиться даже еще более значительными.

Во избежание затруднения понимания описания, на чертеже показан и описан относительно простой процессор (100). В других вариантах воплощения изобретения, процессор, если требуется, может включать в себя другие хорошо известные компоненты, находящиеся в процессорах. Примеры таких компонентов включают в себя: звено предсказания ветвей, звено выборки команд, буферы быстрого преобразования адресов команд и данных, буферы предварительной выборки, очереди микрокоманд, задатчики последовательностей микрокоманд, звено переименования регистров, звено планирования команд, звено изъятия, другие компоненты, входящие в состав процессоров, и разнообразные их сочетания, но не ограничены этими компонентами. Имеются без преувеличения многочисленные различные сочетания и конфигурации компонентов в процессорах, и варианты воплощения изобретения не ограничены никаким конкретным сочетанием или конфигурацией. Варианты воплощения изобретения могут быть включены в состав процессоров, иметь множественные ядра, логические процессоры или, механизмы исполнения, по меньшей мере один из которых включает в себя или использует раскрываемый здесь вариант воплощения изобретения.

Фиг. 2 представляет собой блок-схему алгоритма одного варианта воплощения способа (214), выполняемого внутри или посредством процессора. В некоторых вариантах воплощения изобретения, операции и/или способ, показанные на Фиг. 2, могут быть выполнены посредством или внутри процессора, показанного на Фиг. 1. Подробности и дополнительные признаки, описанные выше для процессора, показанного на Фиг. 1, также, если требуется, применяются к операциям и/или способу, показанным на Фиг. 2, которые могут быть выполнены посредством и/или внутри такого рода процессора. В качестве альтернативы, операции и/или способ, показанные на Фиг. 2, могут быть выполнены посредством и/или внутри схожего или другого процессора. Помимо этого, процессор, показанный на Фиг. 1, может выполнять операции и/или способы, одинаковые с теми, что показаны на Фиг. 2, сходные с ними или отличные от них.

Способ включает в себя, на этапе 216, осуществление доступа к набору регистров по некоторому первому методу. В некоторых вариантах воплощения изобретения, в первом методе этот набор регистров может представлять некоторое множество N-разрядных регистров. Доступ может осуществляться для того, чтобы извлечь из каждого регистра из этого множества N-разрядных регистров соответствующие N-разрядные упакованные данные (или сохранить в каждом регистре из этого множества N-разрядных регистров соответствующие N-разрядные упакованные данные).

Способ включает в себя, на этапе 218, осуществление доступа к этому набору регистров по некоторому второму, другому, методу. В некоторых вариантах воплощения изобретения, во втором методе этот набор регистров может представлять единый регистр, состоящий по меньшей мере из 2N разрядов. Доступ может осуществляться для того, чтобы извлечь из этого единого регистра соответствующие упакованные данные, состоящие по меньшей мере из 2N разрядов, (или сохранить в этом едином регистре соответствующие упакованные данные, состоящие по меньшей мере из 2N разрядов). В некоторых вариантах воплощения изобретения, эти по меньшей мере 2N разрядов могут представлять собой по меньшей мере 256 разрядов.

В других вариантах воплощения изобретения, этот способ может, если требуется, включать в себя осуществление доступа к набору регистров по меньшей мере по третьему другому методу, а в некоторых случаях также и по четвертому другому методу. В некоторых вариантах воплощения изобретения, один из этих методов может обращаться с этими регистрами как с единым регистром, имеющим разрядность, составляющую по меньшей мере 512 разрядов.

Фиг. 3 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 128-разрядным регистрам для упакованных данных - на первом представлении (310), и как к 256-разрядным регистрам для упакованных данных - на втором представлении (312). На первом представлении (310) набор регистров (например, физические регистры) логически рассматриваются или к ним осуществляется доступ как к восьми 128-разрядным регистрам для упакованных данных, помеченным как Х0-Х7. На втором представлении (312) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к четырем (то есть имеющимся в два раза меньшем количестве) 256-разрядным регистрам, помеченным как Y0-Y3. На втором представлении (312) самые младшие 128 разрядов (то есть разряды 127 : 0) 256-разрядного регистра (Y0) отображаются на 128-разрядный регистр (Х0) или соответствуют ему, тогда как самые старшие 128 разрядов (то есть разряды 127 : 64) 256-разрядного регистра (Y0) отображаются на 128-разрядный регистр (XI) или соответствуют ему. Аналогичным образом, каждый из других 256-разрядных регистров (Y1)-(Y3) включает в себя отличную от других пару 128-разрядных регистров (Х2)-(Х7). Множественные (в этом случае два) малые (в этом случае 128-разрядные) регистры логически объединяются или группируется для того, чтобы сформировать единый большой (в этом случае 256-разрядный) регистр. В некоторых вариантах воплощения изобретения, реальные физические регистры, используемые для реализации этих представлений, могут представлять собой 64-разрядные регистры или 128-разрядные регистры. В качестве альтернативы, если требуется, могут быть использованы другие разрядности.

Предусматривается много вариаций проиллюстрированного варианта воплощения изобретения. В проиллюстрированном варианте воплощения, логически объединяются или группируются смежные 128-разрядные регистры (например, Х0 объединяется с X1, Х2 объединяется с Х3 и так далее). В других вариантах воплощения изобретения, могут быть объединены несмежные регистры (например, могут быть объединены несмежные регистры в различных блоках, перемежающиеся регистры и так далее). В проиллюстрированном варианте воплощения изобретения, показаны восемь 128-разрядных регистров (Х0-Х7) и четыре 256-разрядных регистра (Y0-Y3), хотя при желании, можно, если требуется, использовать либо меньшее, либо большее количество регистров. В одном приводимом в качестве примера варианте воплощения изобретения, может иметься достаточно регистров для того, чтобы рассматривать по меньшей мере шестнадцать 128-разрядных регистров (или по меньшей мере тридцать два 128-разрядных регистра) на первом представлении (310), и/или достаточно регистров для того, чтобы рассматривать по меньшей мере восемь 256-разрядных регистров (или по меньшей мере шестнадцать 128-разрядных регистров) на втором представлении (312). Помимо этого, в других вариантах воплощения изобретения, могут поддерживаться три или большее количество представлений, на которых набор регистров рассматриваются в качестве 64-разрядных регистров, 512-разрядных регистров, 1024-разрядных регистров, других емкостей или их сочетаний.

Фиг. 4 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 64-разрядным регистрам для упакованных данных - на первом представлении (410), как к 128-разрядным регистрам для упакованных данных - на втором представлении (412), и как к 256-разрядным регистрам для упакованных данных - на третьем представлении (420). На первом представлении (410) набор регистров (например, физические регистры) логически рассматриваются или к ним осуществляется доступ как к шестнадцати 64-разрядным регистрам для упакованных данных, помеченным как W0-W15.

На втором представлении (412) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к четырем (то есть имеющимся в два раза меньшем количестве) 128-разрядным регистрам, помеченным как Х0-Х7. На втором представлении (412) самые младшие 64 разряда (то есть разряды 63 : 0) 128-разрядного регистра (Х0) соответствуют 64-разрядному регистру (W0), тогда как самые старшие 64 разряда (то есть разряды 127 : 64) 128-разрядного регистра (Х0) соответствуют 64-разрядному регистру (WI). Помимо этого, на втором представлении (412) самые младшие 64 разряда (то есть разряды 63 : 0) 128-разрядного регистра (X1) соответствуют 64-разрядному регистру (W2), тогда как самые старшие 64 разряда (то есть разряды 127 : 64) 128-разрядного регистра (X1) соответствуют 64-разрядному регистру (W3).

На третьем представлении (420) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к четырем 256-разрядным регистрам, помеченным как Y0-Y3. На третьем представлении (420) самые младшие 64 разряда (то есть разряды 63 : 0) 256-разрядного регистра (Y0) соответствуют 64-разрядному регистру (W0), самые младшие промежуточные 64 разряда (то есть разряды 127 : 64) 256-разрядного регистра (Y0) соответствуют, 64-разрядному регистру (W1), самые старшие промежуточные 64 разряда (то есть разряды 191 : 128) 256-разрядного регистра (Y0) соответствуют 64-разрядному регистру (W2), и самые старшие 64 разряда (то есть разряды 255 : 192) 256-разрядного регистра (Y0) соответствуют 64-разрядному регистру (W3). Если взглянуть на это по-другому, то на третьем представлении (420) самые младшие 128 разрядов (то есть разряды 127 : 0) 256-разрядного регистра (Y0) соответствуют 128-разрядному регистру (Х0), а самые старшие 128 разрядов (то есть разряды 255 : 128) 256-разрядного регистра (Y0) соответствуют 128-разрядному регистру (Х0).

В некоторых вариантах воплощения изобретения, реальные физические регистры, используемые для реализации этих представлений, могут представлять собой 64-разрядные регистры или 128-разрядные регистры. В качестве альтернативы, если требуется, могут быть использованы и другие разрядности. Как и ранее, предусматривается много вариаций проиллюстрированного варианта воплощения изобретения. Например, могут быть объединены несмежные регистры (например, могут быть объединены несмежные регистры в различных блоках, перемежающиеся регистры и так далее). В качестве другого примера, могут быть использованы другие количества регистров. Помимо этого в других вариантах воплощения изобретения, могут поддерживаться другие представления, на которых набор регистров рассматриваются в качестве 512-разрядных регистров, 1024-разрядных регистров, других емкостей или их сочетаний.

Фиг. 5 представляет собой блок-схему, на которой проиллюстрирован вариант воплощения изобретения, в котором набор регистров рассматриваются или к ним осуществляется доступ как к 128-разрядным регистрам для упакованных данных - на первом представлении (510), как к 256-разрядным регистрам для упакованных данных - на втором представлении (512), и как к 512-разрядным регистрам для упакованных данных - на третьем представлении (522). На первом представлении (510) набор регистров (например, физические регистры) логически рассматриваются или к ним осуществляется доступ как к восьми 128-разрядным регистрам для упакованных данных, помеченным как Х0-Х7. На втором представлении (512) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к четырем (то есть имеющимся в два раза меньшем количестве) 256-разрядным регистрам, помеченным как Y0-Y3. Эта конфигурация может быть сходной с подходом, показанным и описанным для Фиг. 3.

На третьем представлении (522) тот же самый набор регистров (например, физических регистров) логически рассматриваются или к ним осуществляется доступ как к двум 512-разрядным регистрам, помеченным как Z0-Z1. На третьем представлении (522) самые младшие 128 разрядов (то есть разряды 127 : 0) 512-разрядного регистра (Z0) соответствуют 128-разрядному регистру (Х0), самые младшие промежуточные 128 разрядов (то есть разряды 255 : 128) 512-разрядного регистра (Z0) соответствуют 128-разрядному регистру (X1), самые старшие промежуточные 128 разрядов (то есть разряды 383 : 256) 512-разрядного регистра (Z0) соответствуют 128-разрядному регистру (Х2), и самые старшие 128 разрядов (то есть разряды 511 : 384) 512-разрядного регистра (Z0) соответствуют 128-разрядному регистру (Х3). Если взглянуть на это по-другому, то на третьем представлении (522) самые младшие 256 разрядов (то есть разряды 255 : 0) 512-разрядного регистра (Z0) соответствуют 256-разрядному регистру (Y0), а самые старшие 256 разрядов (то есть разряды 511 : 256) 512-разрядного регистра (Z0) соответствуют 256-разрядному регистру (Y1). Аналогичным образом, каждый из других регистров имеет аналогичное соответствие, как это показано метками разрядов.

В некоторых вариантах воплощения изобретения, реальные физические регистры, используемые для реализации этих представлений, могут представлять собой 64-разрядные регистры или 128-разрядные регистры. В качестве альтернативы, если требуется, могут быть использованы, другие разрядности. Как и ранее, предусматривается много вариаций проиллюстрированного варианта воплощения изобретения. Например, могут быть объединены несмежные регистры (например, могут быть объединены несмежные регистры в различных блоках, перемежающиеся регистры и так далее). В качестве другого примера, могут быть использованы другие количества