Адаптер магистрального последовательного интерфейса мультиплексного канала информационного обмена

Иллюстрации

Показать всеИзобретение относится к вычислительной технике и может быть использовано в вычислительных системах различного назначения для передачи информации между различными частями распределенных вычислительных систем. Технический результат, достигаемый при реализации разработанного устройства, состоит в том, что использование высокоскоростного интерфейса PCI-E для обмена данными с управляющим микропроцессором и памятью, содержащей задания, позволяет гибко изменять циклограмму работы без прерывания обмена по мультиплексному каналу, при этом управление и инициализация устройства происходит путем записи во внутренние управляющие регистры и также может происходить без прерывания работы. Для этого предложен адаптер, который содержит шину PCI-E и шину AXI, соединенные посредством моста AXI-PCI-E, а также от 4 до 8 каналов шины магистрального последовательного интерфейса с централизованным управлением, каждый из которых выполнен с возможностью одновременно выступать в качестве контроллера шины, оконечного устройства и монитора шины. 1 ил.

Реферат

Изобретение относится к вычислительной технике и может быть использовано в вычислительных системах различного назначения для передачи информации между различными частями распределенных вычислительных систем.

Известен (Микропроцессоры и микроЭВМ в системах автоматического управления: Справочник / С.Т. Хвощ, Н.Н. Варлинский, Е.А. Попов; Под общ. ред. С.Т. Хвоща. - Л.: Машиностроение. Ленингр. отд-ние, 1987, стр. 242-243, рис. 6.17,б) адаптер мультиплексных каналов информационного обмена, содержащий первый контроллер мультиплексных каналов информационного обмена (адаптер канала), первый приемопередатчик мультиплексного канала информационного обмена (образованный формирователем трансформаторной линии и оконечным усилителем), первый трансформатор гальванической развязки, при этом вход-выход (образованный выходами сигналов DO0, DO1 и входами сигналов MR, DI0, DI1) первого контроллера мультиплексных каналов информационного обмена соединен с первым входом-выходом (образованного входами сигналов DO0, DO1 и выходами сигналов MR, DI0, DI1) первого приемопередатчика мультиплексного канала информационного обмена, второй вход-выход первого приемопередатчика мультиплексного канала информационного обмена соединен с входом-выходом первого трансформатора гальванической развязки, выход которого является выходом первого мультиплексного канала информационного обмена адаптера мультиплексных каналов информационного обмена.

Недостатком известного устройства следует признать реализацию устройства на устаревшей элементной базе и, как следствие, ограниченную гибкость управления, функциональность и производительность, а также необходимость развитой системы внешнего управления. Отдельно стоит упомянуть отсутствие программной реализации смены адреса устройства в режиме ОУ (меняется путем распайки).

Известен также (RU, патент 2163728, опубл. 27.02.2001) адаптер мультиплексных каналов информационного обмена, содержащий первый контроллер мультиплексных каналов информационного обмена, первый приемопередатчик мультиплексного канала информационного обмена, первый трансформатор гальванической развязки, кроме того, он дополнительно содержит второй приемопередатчик мультиплексного канала информационного обмена, второй трансформатор гальванической развязки, первый микропроцессор, первое оперативное запоминающее устройство, первое постоянное запоминающее устройство, первый контроллер внешней интерфейсной магистрали информационного обмена, первый формирователь выходных разовых команд, первый приемник входных разовых команд, второй контроллер мультиплексных каналов информационного обмена, третий приемопередатчик мультиплексного канала информационного обмена, третий трансформатор гальванической развязки, четвертый приемопередатчик мультиплексного канала информационного обмена, четвертый трансформатор гальванической развязки, второй микропроцессор, второе оперативное запоминающее устройство, второе постоянное запоминающее устройство, второй контроллер внешней интерфейсной магистрали информационного обмена, второй формирователь выходных разовых команд, второй приемник входных разовых команд, формирователь сигнала сброса, формирователь сигнала исправности, буферный формирователь, первую внутреннюю интерфейсную магистраль информационного обмена, вторую внутреннюю интерфейсную магистраль информационного обмена, устройство ввода сигнала ручного сброса, при этом первый вход-выход первого контроллера мультиплексных каналов информационного обмена соединен с первым входом-выходом первого приемопередатчика мультиплексного канала информационного обмена, второй вход-выход первого контроллера мультиплексных каналов информационного обмена соединен с первым входом-выходом второго приемопередатчика мультиплексного канала информационного обмена, вторые входы-выходы первого и второго приемопередатчиков мультиплексных каналов информационного обмена соединены соответственно с первым и вторым трансформаторами гальванической развязки, выходы которых являются соответственно выходами первого и второго мультиплексных каналов информационного обмена адаптера мультиплексных каналов информационного обмена, интерфейсные входы-выходы первого контроллера мультиплексных каналов информационного обмена, первого микропроцессора, первого оперативного запоминающего устройства, первого постоянного запоминающего устройства, а также первый интерфейсный вход-выход первого контроллера внешней интерфейсной магистрали информационного обмена соединены между собой при помощи первой внутренней интерфейсной магистрали информационного обмена, выход разовых команд первого контроллера мультиплексных каналов информационного обмена соединен со входом первого формирователя выходных разовых команд, выход которого является первым выходом разовых команд адаптера мультиплексных каналов информационного обмена, вход разовых команд первого контроллера мультиплексных каналов информационного обмена соединен с выходом первого приемника входных разовых команд, вход которого является первым входом разовых команд адаптера мультиплексных каналов информационного обмена, второй интерфейсный вход-выход первого контроллера внешней интерфейсной магистрали информационного обмена соединен с первым входом-выходом буферного формирователя, второй вход-выход которого является входом-выходом внешней интерфейсной магистрали информационного обмена адаптера мультиплексных каналов информационного обмена, первый вход-выход второго контроллера мультиплексных каналов информационного обмена соединен с первым входом-выходом третьего приемопередатчика мультиплексного канала информационного обмена, второй вход-выход второго контроллера мультиплексных каналов информационного обмена соединен с первым входом-выходом четвертого приемопередатчика мультиплексного канала информационного обмена, вторые входы-выходы третьего и четвертого приемопередатчиков мультиплексных каналов информационного обмена соединены соответственно с третьим и четвертым трансформаторами гальванической развязки, выходы которых являются соответственно выходами третьего и четвертого мультиплексных каналов информационного обмена адаптера мультиплексных каналов информационного обмена, интерфейсные входы-выходы второго контроллера мультиплексных каналов информационного обмена, второго микропроцессора, второго оперативного запоминающего устройства, второго постоянного запоминающего устройства, а также первый интерфейсный вход-выход второго контроллера внешней интерфейсной магистрали информационного обмена соединены между собой при помощи второй внутренней интерфейсной магистрали информационного обмена, выход разовых команд второго контроллера мультиплексных каналов информационного обмена соединен со входом второго формирователя выходных разовых команд, выход которого является вторым выходом разовых команд адаптера мультиплексных каналов информационного обмена, вход разовых команд второго контроллера мультиплексных каналов информационного обмена соединен с выходом второго приемника входных разовых команд, вход которого является вторым входом разовых команд адаптера мультиплексных каналов информационного обмена, второй интерфейсный вход-выход второго контроллера внешней интерфейсной магистрали информационного обмена соединен с первым входом-выходом буферного формирователя, первый выход первого контроллера внешней интерфейсной магистрали информационного обмена соединен с первым входом формирователя сигнала сброса, первый выход второго контроллера внешней интерфейсной магистрали информационного обмена соединен со вторым входом формирователя сигнала сброса, выход устройства ввода сигнала ручного сброса соединен с третьим входом формирователя сигнала сброса, выход формирователя сигнала сброса соединен с первой и второй внутренними интерфейсными магистралями информационного обмена, второй выход первого контроллера внешней интерфейсной магистрали информационного обмена соединен с первым входом формирователя сигнала исправности, второй выход второго контроллера внешней интерфейсной магистрали информационного обмена соединен со вторым входом формирователя сигнала исправности, выход формирователя сигнала исправности является выходом сигнала исправности адаптера мультиплексных каналов информационного обмена.

Недостатком известного устройства следует признать программную реализацию контроллера обмена сообщениями по мультиплексному каналу. Данное решение, ввиду ограниченной производительности управляющих микропроцессоров и усложнении управляющих программ (при увеличении количества мультиплексных каналов), влечет за собой использование по одному микропроцессору, ОЗУ, ПЗУ и контроллеру внешней интерфейсной магистрали информационного обмена на каждую пару мультиплексных каналов. Таким образом, данное решение ведет к усложнению и удорожанию устройства при попытке увеличения количества мультиплексных каналов. Также одновременный доступ к ОЗУ со стороны как микропроцессора, так и контроллера внешней интерфейсной магистрали информационного обмена без разграничения доступа к одним и тем же ячейкам может привести к передаче или чтении порченных данных. Использование для хранения программы микропроцессора внешней ПЗУ может привести к сбоям в работе при повреждении содержимого ПЗУ при многократных чтениях во время работы.

Техническая задача, решаемая посредством разработанного устройства, состоит в обеспечении автономности работы и гибкости управления обменами по мультиплексным каналам, а также в возможности изменения количества мультиплексных каналов без существенной переделки устройства.

Технический результат, достигаемый при реализации разработанного устройства состоит в том, что использование высокоскоростного интерфейса PCI-E для обмена данными с управляющим микропроцессором и памятью, содержащей задания, позволяет гибко изменять циклограмму работы без прерывания обмена по мультиплексному каналу, при этом управление и инициализация устройства происходит путем записи во внутренние управляющие регистры и также может происходить без прерывания работы.

Разработанное устройство само считывает задания из внешней памяти и также само записывает в нее результаты обменов по мультиплексным каналам, управляющий микропроцессор занят только чтением из памяти и анализом результатов заданий, а также формированием и записью новых заданий, что позволяет использовать микропроцессоры с низкой производительностью и ценой. Также разгрузка управляющего микропроцессора и аппаратная реализация в виде одного устройства позволяет увеличивать количество мультиплексных каналов практически без удорожания устройства.

Для достижения указанного технического результата предложено использовать адаптер магистрального последовательного интерфейса мультиплексного канала информационного обмена с управлением через PCI-Е и временным тактированием обмена разработанной конструкции. Он содержит шину PCI-E и шину AXI, соединенные посредством моста AXI-PCI-E, а также от 4 до 8 каналов шины магистрального последовательного интерфейса с централизованным управлением, каждый из которых выполнен с возможностью одновременно выступать в качестве контроллера шины, оконечного устройства и монитора шины, причем для каждого указанного канала шина AXI подключена к блоку выбора задания для исполнения, выполненному с узлами FIFO задания низкого приоритета, FIFO задания обычного приоритета и FIFO задания высокого приоритета, выход блока выбора заданий для исполнения каждого канала подключен к входу первого мультиплексора, выход которого подключен к входу блока чтения и разбора заданий для контроллера шины, при этом к дополнительному входу первого мультиплексора подключен первый выход блока управления мультиплексором, второй выход которого подключен к входу блока дешифратора шины для прочитанного задания, посредством блока чтения и разбора заданий для контроллера шины и последовательно подключенного блока дешифратора шины для прочитанного задания для каждого канала через параллельно подключенные блок контроллера шины, блок оконечного устройства и блок монитора шины к мультиплексору каждого канала, к четвертому входу которого подключен первый выход второго блока управления мультиплексора, выход мультиплексора каждого канала через последовательно установленные блок формирователь кода и блок логики выбора линии к входу линии резервной этого канала и входу линии основной этого канала, при этом линия резервная присоединена к декодеру резервной линии, а линия основная присоединена к декодеру основной линии, которые в свою очередь присоединены к блокам контроллера шины, оконечного устройства и монитора шины, причем блоки контроллера шины, оконечного устройства и монитора шины каждого из каналов посредством последовательно подключенных дополнительного мультиплексора, к дополнительному входу которого подключен дополнительный блок управления, и блока выгрузки результатов сообщений мультиплексного канала информационного обмена подключены к шине AXI.

Указанный технический результат достигается за счет того, что использование одного блока чтения заданий и одного блока выгрузки результатов с разделенным по времени доступом к ним со стороны контроллеров каналов мультиплексного обмена при помощи блока выбора канала и блока выбора источника результата позволяет наращивать количество мультиплексных каналов путем простого масштабирования. Не последнюю роль в этом играет использование высокоскоростных интерфейсов AXI и PCI-E, позволяющих без задержек обслуживать множество каналов. Наличие активных блоков чтения заданий и выгрузки результатов также позволяет контроллерам мультиплексных каналов без внешнего непосредственного управления осуществлять чтение задания из внешней памяти и выгрузку результатов. Наличие в каждом контроллере мультиплексного канала логики КШ, ОУ и МШ с управлением посредством внутренних регистров, доступных для записи со стороны управляющего микропроцессора, позволяет оперативно менять функционал устройства. А использование во внутренней памяти ОУ переключаемых областей с разграничением доступа позволяет производить обновление данных в любой момент времени без нарушения их целостности.

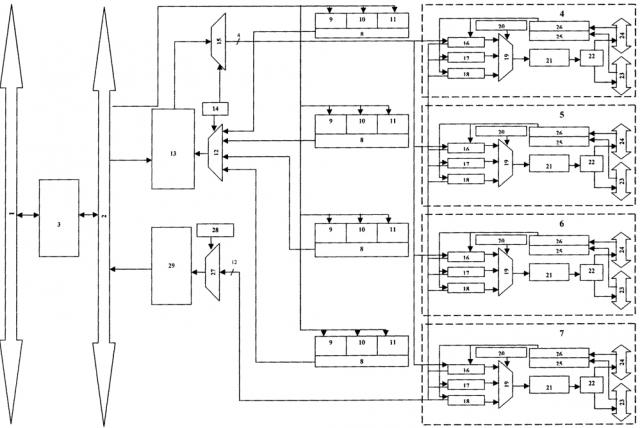

Разработанная конструкция приведена на блок-схеме с использованием следующих обозначений: шина 1 PCI-E, шина 2 AXI, мост 3 AXI-PCI-E, каналы 4, 5, 6, 7 шины магистрального последовательного интерфейса, блок 8 выбора задания для исполнения, выполненный с узлами FIFO 9 задания низкого приоритета, FIFO 10 задания обычного приоритета и FIFO 11 задания высокого приоритета, первый мультиплексор 12, блок 13 чтения и разбора заданий для контроллера шины, блок 14 управления мультиплексором 12, блок 15 дешифратора шины для прочитанного задания для выбранного блоком 14 канала, блок 16 контроллера шины, блок 17 оконечного устройства, блок 18 монитора шины, мультиплексор 19 второй, блок 20 управления второго мультиплексора, блок 21 формирователь кода, блок 22 логики выбора линии, линия 23 резервная, линия 24 основная, декодер 25 резервной линии, декодер 26 основной линии, мультиплексор выбора источника результатов 27, блок управления мультиплексором выбора источника результатов 28, блок выгрузки результатов 29.

Все временные, электрические и логические характеристики устройства соответствуют ГОСТ Р 52070 2003. Устройство содержит (в зависимости от реализации) от 4-х до 8-ми каналов магистрального последовательного интерфейса с централизованным управлением (шины Манчестер), каждый из которых может одновременно выступать в качестве КШ (контроллер шины), ОУ (оконечное устройство) и МШ (монитор шины). Инициализация, запись заданий и данных, а также выгрузка результатов осуществляется по шине стандарта AXI через мост AXI - PCI-E с использованием управляющего микропроцессора, размещенного на том же модуле.

Всего в каждом канале 2 линии связи - основная и резервная. Внутри кристалла сформированы 4 виртуальных петли, не выходящих за пределы кристалла, для коммутации каналов. При желании все каналы могут быть соединены попарно, либо все подключены на одну петлю, либо иным способом. При отключении данной функции все каналы подключаются к внешним линиям связи. Настройка коммутации определяется управляющим регистром.

КШ, ОУ и МШ представляют собой, в рамках одного канала, полностью независимые сущности. Общим для них являются только формирователь, декодеры кода Манчестер и адресное пространство управляющих регистров.

Т.к. КШ на линии всегда один и каждое устройство выходит на линию последовательно, наличие собственного формирователя у каждой сущности является избыточным. Формирователь по необходимости отсылает код либо по основной, либо по резервной линии. Так как основную и резервную линию необходимо прослушивать одновременно, в устройстве присутствует 2 декодера на канал, по одному на основную и резервную линию.

Одной из особенностей ОУ является реализация внутренней памяти. Данная память доступна на запись/чтение со стороны пользователей (шины AXI) и на чтение со стороны шины Манчестер. Поэтому существует риск чтения и выдачи в линию испорченных или не до конца обновленных данных. Со стороны шины AXI данная память представляет собой непрерывное адресное пространство. Со стороны шины Манчестер она разбита на подадреса (30 подадресов по 32 16-битных слов в каждом). Для исключения нарушения целостности данных каждый подадрес физически продублирован и состоит из 2-х страниц. Одна страница доступна для чтения/записи со стороны AXI, в то время как вторая доступна для чтения со стороны шины Манчестер. Переключение страниц происходит после полной перезаписи подадреса со стороны AXI и окончания передачи (если она была) с этого подадреса в линию Манчестера.

Задания для КШ представляют собой набор данных, структурированных особым образом. Эта структура содержит командное слово(а), признаки типа сообщения (КШ→ОУ, КШ←ОУ, ОУ→ОУ), наличия данных в сообщении, количества данных, передачи по основной/резервной линии, повтора, выдачи прерывания по завершению сообщения, пропуска задания и т.д. Данная структура, представляющая собой полное описание для организации передачи сообщения по шине Манчестер, находится во внешней (по отношению к устройству) памяти. Адреса нахождения заданий выровнены по 256 байт (2 страницы по 128 байт). Устройству передается только индекс задания и номер актуальной страницы. Базовый адрес всех заданий содержится в управляющем регистре канала. По индексу и базовому адресу устройство вычисляет адрес задания и считывает его для дальнейшей обработки.

Временная шкала работы устройства разбита по кадрам. Продолжительность кадра задается в управляющем регистре канала. В FIFO, содержащем индексы заданий, помимо самого индекса содержатся признаки начала и конца кадра. Кадр - это промежуток времени, в течение которого устройство должно выдать сообщения от признака "начало кадра" по признак "конец кадра". После выдачи последнего сообщения в кадре (с признаком "конец кадра") устройство выдает прерывание и ждет окончания времени этого кадра.

Все задания разбиты на 3 приоритета: обычный, высокий и низкий. Для них существуют 3 разных FIFO. У каждого FIFO свой адрес для записи в него индексов заданий.

Задания обычного приоритета выполняются в течение кадра в порядке очереди считывания их из соответствующего FIFO. Если сообщения обычного приоритета не укладываются во временные рамки кадра, то они все равно будут переданы. А сообщения из следующего кадра тогда будут переданы с минимальной паузой после передачи последнего сообщения из предыдущего кадра. При систематическом превышении нагрузки на кадр сообщениями обычного приоритета границы кадра будут постоянно смещаться. Ответственность за это целиком и полностью лежит на пользователе.

Задания высокого приоритета выполняются сразу же после записи их индекса в соответствующее FIFO и окончании передачи текущего задания, не учитывая границы кадров.

Задания низкого приоритета передаются после окончания передачи последнего сообщения обычного приоритета в кадре и отсутствии сообщений высокого приоритета. Также учитывается время, необходимое для передачи этого сообщения низкого приоритета. Если времени, оставшегося до конца кадра, осталось меньше, чем время, необходимое на передачу, сообщение передаваться не будет.

После окончания передачи каждая сущность (КШ, ОУ, МШ) подготавливает отчет о сообщении в определенном формате. Структура этого отчета разная для каждой сущности. Размер всех отчетов у всех сущностей одинаков и равен 128 байт. В этих отчетах содержатся индекс задания (только для КШ), командное слово или слова (только для ОУ и МШ), ответное слово, аналитика и наличие выявленных ошибок в сообщении, принятые данные, временная метка глобального таймера и т.д.

Для каждой сущности для выгрузки результатов во внешней памяти организуется кольцевой буфер. Размер буфера (в отчетах) и базовый адрес задаются в управляющих регистрах канала.

Адаптер магистрального последовательного интерфейса мультиплексного канала информационного обмена с управлением через PCI-E и временным тактированием обмена, характеризуемый тем, что он содержит шину PCI-E и шину AXI, соединенные посредством моста AXI-PCI-E, а также от 4 до 8 каналов шины магистрального последовательного интерфейса с централизованным управлением, каждый из которых выполнен с возможностью одновременно выступать в качестве контроллера шины, оконечного устройства и монитора шины, причем для каждого указанного канала шина AXI подключена к блоку выбора задания для исполнения, выполненному с узлами FIFO задания низкого приоритета, FIFO задания обычного приоритета и FIFO задания высокого приоритета, выход блока выбора заданий для исполнения каждого канала подключен к входу первого мультиплексора, выход которого подключен к входу блока чтения и разбора заданий для контроллера шины, при этом к дополнительному входу первого мультиплексора подключен первый выход блока управления мультиплексором, второй выход которого подключен к входу блока дешифратора шины для прочитанного задания, посредством блока чтения и разбора заданий для контроллера шины и последовательно подключенного блока дешифратора шины для прочитанного задания для каждого канала через параллельно подключенные блок контроллера шины, блок оконечного устройства и блок монитора шины - к мультиплексору каждого канала, к четвертому входу которого подключен первый выход второго блока управления мультиплексора, выход мультиплексора каждого канала через последовательно установленные блок формирователь кода и блок логики выбора линии подключен к входу линии резервной этого канала и входу линии основной этого канала, при этом линия резервная присоединена к декодеру резервной линии, а линия основная присоединена к декодеру основной линии, которые, в свою очередь, присоединены к блокам контроллера шины, оконечного устройства и монитора шины, причем блоки контроллера шины, оконечного устройства и монитора шины каждого из каналов посредством последовательно подключенных дополнительного мультиплексора, к дополнительному входу которого подключен дополнительный блок управления, и блока выгрузки результатов сообщений мультиплексного канала информационного обмена подключены к шине AXI.