Каскодный дифференциальный операционный усилитель

Иллюстрации

Показать всеИзобретение относится к прецизионным устройствам усиления сигналов. Технический результат заключается в повышении разомкнутого коэффициента усиления по напряжению операционного усилителя. Каскодный дифференциальный операционный усилитель содержит: входной дифференциальный каскад с общей эмиттерной цепью, согласованной с первой шиной источника питания, первый, второй, третий, четвертый дополнительные транзисторы, базы первого и второго дополнительных транзисторов подключены к первому токовому выходу входного дифференциального каскада, базы третьего и четвертого дополнительных транзисторов подключены ко второму токовому выходу входного дифференциального каскада, объединенные эмиттеры первого и второго дополнительных транзисторов связаны с эмиттером второго выходного транзистора, объединенные эмиттеры третьего и четвертого дополнительных транзисторов соединены с эмиттером первого выходного транзистора, коллекторы второго и третьего дополнительных транзисторов соединены с первым токовым выходом входного дифференциального каскада а коллекторы первого и четвертого дополнительных транзисторов связаны со вторым токовым выходом входного дифференциального каскада. 1 з.п. ф-лы, 11 ил.

Реферат

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления сигналов.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых и биполярных транзисторах, выполненные на основе архитектуры «перегнутого» каскода [1-36]. Их основные достоинства - расширенный частотный диапазон, а также эффективное использование напряжения питания.

Для работы в условиях космического пространства, в экспериментальной физике необходимы энергоэффективные радиационно-стойкие ОУ с малым напряжением смещения нуля (Uсм) и расширенным диапазоном линейной работы. Мировой опыт проектирования устройств данного класса показывает, что решение этой задачи возможно с использованием биполярно-полевого технологического процесса [15], обеспечивающего формирование р-канальных полевых и высококачественных n-p-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2. Однако для таких ОУ необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [15].

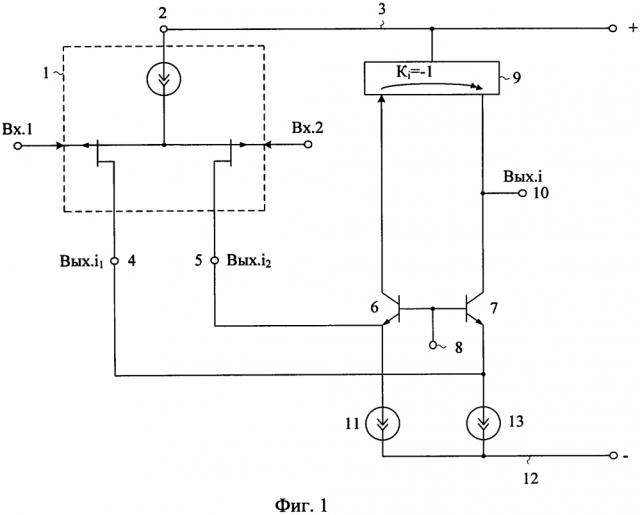

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель по патенту US 7.215.200, fig. 6. Он содержит (фиг. 1) входной дифференциальный каскад 1 с общей эмиттерной цепью 2, согласованной с первой 3 шиной источника питания, первый 4 и второй 5 токовые выходы входного дифференциального каскада 1, первый 6 и второй 7 выходные транзисторы, базы которых объединены и подключены к вспомогательному источнику напряжения 8, токовое зеркало 9, согласованное с первой 3 шиной источника питания, вход которого связан с коллектором первого 6 выходного транзистора, а выход подключен к коллектору второго 7 выходного транзистора и связан с токовым выходом 10 устройства, первый 11 токостабилизирующий двухполюсник, включенный между эмиттером первого 6 выходного транзистора и второй 12 шиной источника питания, второй 13 токостабилизирующий двухполюсник, включенный между эмиттером второго 7 выходного транзистора и второй 12 шиной источника питания.

Существенный недостаток известного ОУ состоит в том, что он имеет сравнительно небольшой разомкнутый коэффициент усиления по напряжению.

Основная задача предлагаемого изобретения состоит в повышении разомкнутого коэффициента усиления по напряжению без ухудшения статического тока ОУ.

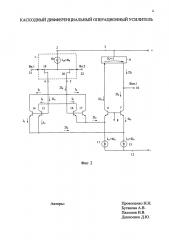

Поставленная задача достигается тем, что в операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1 с общей эмиттерной цепью 2, согласованной с первой 3 шиной источника питания, первый 4 и второй 5 токовые выходы входного дифференциального каскада 1, первый 6 и второй 7 выходные транзисторы, базы которых объединены и подключены к вспомогательному источнику напряжения 8, токовое зеркало 9, согласованное с первой 3 шиной источника питания, вход которого связан с коллектором первого 6 выходного транзистора, а выход подключен к коллектору второго 7 выходного транзистора и связан с токовым выходом 10 устройства, первый 11 токостабилизирующий двухполюсник, включенный между эмиттером первого 6 выходного транзистора и второй 12 шиной источника питания, второй 13 токостабилизирующий двухполюсник, включенный между эмиттером второго 7 выходного транзистора и второй 12 шиной источника питания, предусмотрены новые элементы и связи - в схему введены первый 14, второй 15, третий 16, четвертый 17 дополнительные транзисторы, базы первого 14 и второго 15 дополнительных транзисторов подключены к первому 4 токовому выходу входного дифференциального каскада 1, базы третьего 16 и четвертого 17 дополнительных транзисторов подключены к второму 5 токовому выходу входного дифференциального каскада 1, объединенные эмиттеры первого 14 и второго 15 дополнительных транзисторов связаны с эмиттером второго 7 выходного транзистора, объединенные эмиттеры третьего 16 и четвертого 17 дополнительных транзисторов соединены с эмиттером первого 6 выходного транзистора, коллекторы второго 15 и третьего 16 дополнительных транзисторов соединены с первым 4 токовым выходом входного дифференциального каскада 1, а коллекторы первого 14 и четвертого 17 дополнительных транзисторов связаны со вторым 5 токовым выходом входного дифференциального каскада 1.

На фиг. 1 показана схема ОУ-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с п. 1 формулы изобретения.

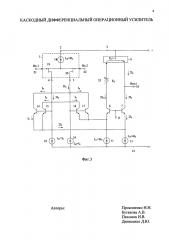

На фиг. 3 приведена схема фиг. 2 в соответствии с п. 2 формулы изобретения.

На фиг. 4 приведена модифицированная схема фиг. 3 с дополнительной цепью согласования потенциалов 25, которая уменьшает влияние напряжения Эрли транзисторов на статический режим.

На фиг. 5 показана схема фиг. 3 со специальным вариантом построения входного дифференциального каскада 1, который обеспечивает в ОУ несколько входов.

На фиг. 6 приведена схема ОУ фиг. 2 в среде компьютерного моделирования PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г. Минск).

На фиг. 7 представлены амплитудно-частотные характеристики операционного усилителя фиг. 6 без отрицательной обратной связи и со 100% отрицательной обратной связью (ООС).

На фиг. 8 приведена схема ОУ фиг. 4 в среде компьютерного моделирования PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г. Минск).

На фиг. 9 показана частотная зависимость коэффициента усиления по напряжению ОУ фиг. 8 без отрицательной обратной связи и с отрицательной обратной связью.

На фиг. 10 приведена схема ОУ фиг. 5 в среде компьютерного моделирования PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г. Минск).

На фиг. 11 показана частотная зависимость коэффициента усиления по напряжению ОУ фиг. 10 без отрицательной обратной связи (ООС) и со 100% ООС.

Компьютерное моделирование предлагаемых выше схемотехнических решений ОУ (фиг. 6, фиг. 8, фиг. 10) показывает, что систематическая составляющая их напряжения смещения нуля не превышает 5-10 мкВ (при высокой идентичности элементов - отсутствии разброса параметров транзисторов).

Каскодный дифференциальный операционный усилитель фиг. 2 содержит входной дифференциальный каскад 1 с общей эмиттерной цепью 2, согласованной с первой 3 шиной источника питания, первый 4 и второй 5 токовые выходы входного дифференциального каскада 1, первый 6 и второй 7 выходные транзисторы, базы которых объединены и подключены к вспомогательному источнику напряжения 8, токовое зеркало 9, согласованное с первой 3 шиной источника питания, вход которого связан с коллектором первого 6 выходного транзистора, а выход подключен к коллектору второго 7 выходного транзистора и связан с токовым выходом 10 устройства, первый 11 токостабилизирующий двухполюсник, включенный между эмиттером первого 6 выходного транзистора и второй 12 шиной источника питания, второй 13 токостабилизирующий двухполюсник, включенный между эмиттером второго 7 выходного транзистора и второй 12 шиной источника питания. В схему введены первый 14, второй 15, третий 16, четвертый 17 дополнительные транзисторы, базы первого 14 и второго 15 дополнительных транзисторов подключены к первому 4 токовому выходу входного дифференциального каскада 1, базы третьего 16 и четвертого 17 дополнительных транзисторов подключены к второму 5 токовому выходу входного дифференциального каскада 1, объединенные эмиттеры первого 14 и второго 15 дополнительных транзисторов связаны с эмиттером второго 7 выходного транзистора, объединенные эмиттеры третьего 16 и четвертого 17 дополнительных транзисторов соединены с эмиттером первого 6 выходного транзистора, коллекторы второго 15 и третьего 16 дополнительных транзисторов соединены с первым 4 токовым выходом входного дифференциального каскада 1, а коллекторы первого 14 и четвертого 17 дополнительных транзисторов связаны со вторым 5 токовым выходом входного дифференциального каскада 1.

Входной дифференциальный каскад 1 в схеме фиг. 2 выполнен на основе источника опорного тока 18 и входных полевых транзисторов 19, 20, затворы которых связаны с соответствующими входами ОУ 21 и 22.

На фиг. 3, в соответствии с п. 2 формулы изобретения, первый 4 токовый выход входного дифференциального каскада 1 связан со второй 12 шиной источника питания через первый 23 дополнительный токостабилизирующий двухполюсник, а второй 5 токовый выход входного дифференциального каскада 1 связан со второй 12 шиной источника питания через второй 24 дополнительный токостабилизирующий двухполюсник. Это позволяет по-иному устанавливать статический режим первого 14, второго 15, третьего 16, четвертого 17 дополнительных транзисторов.

На фиг. 4 приведена модифицированная схема фиг. 3 с дополнительной цепью согласования потенциалов 25, которая уменьшает влияние напряжения Эрли транзисторов на напряжение смещения нуля ОУ.

Для уменьшения выходного сопротивления заявляемого устройства в схеме фиг. 4 включен буферный усилитель 26, имеющий относительно выхода 27 малое выходное сопротивление. Это расширяет области применения заявляемого устройства.

В схеме фиг. 5 в качестве входного дифференциального каскада 1 используются составные транзисторы, реализуемые на входных биполярных (32, 33) и входных полевых (34,35) активных элементах. Это позволяет на основе заявляемого устройства реализовать операционные усилители с несколькими входами 28, 29, 30, 31.

Рассмотрим коротко работу ОУ фиг. 2.

За счет введения новых элементов (первого 14, второго 15, третьего 16 и четвертого 17 дополнительных транзисторов), а также новых связей между ними, эквивалентное сопротивление в цепи нагрузки входного дифференциального каскада 1 существенно повышается. Это является необходимым условием увеличения его коэффициента усиления по напряжению. При этом коэффициент усиления по напряжению выходного каскада на первом 6 и втором 7 выходных транзисторах не изменяется, а общий коэффициент усиления разомкнутого ОУ возрастает более чем на порядок.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом по величине разомкнутого коэффициента усиления по напряжению.

БИБЛИОГРАФИЧЕСКИЙ СПИСОК

1. Патент США №5.422.600, фиг. 2.

2. Патент США №4.406.990, фиг. 4.

3. Патент США №5.952.882.

4. Патент США №4.723.111.

5. Патент США №4.293.824.

6. Патент США №5.323.121.

7. Патент США №5.420.540 fig. 1.

8. Патент RU №2.354.041 С1.

9. Патентная заявка США №2003/0201828 fig 1, fig 2.

10. Патент США №6.825.721 fig 1, fig 2.

11. Патент США №6.542.030 fig. 1.

12. Патент US 6.456.162, fig. 2.

13. Патент US 6.501.333.

14. Патент US 6.717.466.

15. Патентная заявка US №2002/0196079, fig 1.

16. Патент US №4.600.893, fig. 7.

17. Патент US №4.004.245.

18. Патент US №7.411.451, fig. 5.

19. Патент US №6.788.143.

20. Патент US 4.387.309.

21. Патент US 4.390.850.

22. Патент US 5.963.085.

23. Патент US 4.783.637.

24. Патент GB 2.035.003, fig. 2.

25. Патент US 7.215.200, fig. 6.

26. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

27. Операционные усилители с непосредственной связью каскадов: монография / Анисимов В.И., Капитонов М.В., Прокопенко Н.Н., Соколов Ю.М. - Л.: «Энергия», 1979. - 148 с.

28. Нелинейная активная коррекция в прецизионных аналоговых микросхемах: монография / Н.Н. Прокопенко. - Ростов-на-Дону: Изд-во Северо-Кавказского научного центра высшей школы, 2000. - 222 с.

29. Прокопенко, Н.Н. Архитектура и схемотехника быстродействующих операционных усилителей: монография / Н.Н. Прокопенко, А.С. Будяков. - Шахты: Изд-во ЮРГУЭС, 2006. - 231 с.

30. Основные параметры и уравнения базовых схем включения мультидифференциальных операционных усилителей с высокоимпедансным узлом / Н.Н. Прокопенко, Н.В. Бутырлагин, И.В. Пахомов // Проблемы разработки перспективных микро- и наноэлектронных систем - 2014. Сборник трудов. Часть 3 / под общ. ред. академика РАН А.Л. Стемпковского. - М.: ИППМ РАН, Зеленоград, 2014. - С. 111-116.

31. Основные свойства, параметры и базовые схемы включения мультидифференциальных операционных усилителей с высокоимпедансным узлом / Н.Н. Прокопенко, О.В. Дворников, П.С. Будяков // Электронная техника. Серия 2. Полупроводниковые приборы. Выпуск 2 (233), Москва, ОАО «Пульсар», 2014 г. С. 53-64.

32. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 1 / О. Дворников // Компоненты и технологии, №6, 2005, http://kit-e.ru/articles/device/2005_6_218.php.

33. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 2 / О. Дворников // Компоненты и технологии, №7, 2005, http://kit-e.ru/articles/device/2005_7_216.php.

34. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 3 / О. Дворников // Компоненты и технологии, №8, 2005, http://kit-e.ru/articles/device/2005_8_184.php.

35. Архитектура и схемотехника дифференциальных усилителей с повышенным ослаблением синфазных сигналов: монография / Н.Н. Прокопенко, С.В. Крюков. - Шахты: ГОУ ВПО «ЮРГУЭС», 2008. - 329 с.

36. The main connection circuits of the radiation-hardened differential difference amplifier based on the bipolar and field effect technological process / N.N. Prokopenko, O.V. Dvornikov, N.V. Butyrlagin, A.V. Bugakova // 2014 12th International conference on actual problems of electronic instrument engineering (APEIE - 2014) proceedings in 7 Volumes; Novosibirsk, October 2-4, 2014. - Novosibirsk State Technical University. - Vol. 1. - P. 29-34 DOI: 10.1109/APEIE.2014.7040870.

1. Каскодный дифференциальный операционный усилитель, содержащий входной дифференциальный каскад (1) с общей эмиттерной цепью (2), согласованной с первой (3) шиной источника питания, первый (4) и второй (5) токовые выходы входного дифференциального каскада (1), первый (6) и второй (7) выходные транзисторы, базы которых объединены и подключены к вспомогательному источнику напряжения (8), токовое зеркало (9), согласованное с первой (3) шиной источника питания, вход которого связан с коллектором первого (6) выходного транзистора, а выход подключен к коллектору второго (7) выходного транзистора и связан с токовым выходом (10) устройства, первый (11) токостабилизирующий двухполюсник, включенный между эмиттером первого (6) выходного транзистора и второй (12) шиной источника питания, второй (13) токостабилизирующий двухполюсник, включенный между эмиттером второго (7) выходного транзистора и второй (12) шиной источника питания, отличающийся тем, что в схему введены первый (14), второй (15), третий (16), четвертый (17) дополнительные транзисторы, базы первого (14) и второго (15) дополнительных транзисторов подключены к первому (4) токовому выходу входного дифференциального каскада (1), базы третьего (16) и четвертого (17) дополнительных транзисторов подключены к второму (5) токовому выходу входного дифференциального каскада (1), объединенные эмиттеры первого (14) и второго (15) дополнительных транзисторов связаны с эмиттером второго (7) выходного транзистора, объединенные эмиттеры третьего (16) и четвертого (17) дополнительных транзисторов соединены с эмиттером первого (6) выходного транзистора, коллекторы второго (15) и третьего (16) дополнительных транзисторов соединены с первым (4) токовым выходом входного дифференциального каскада (1), а коллекторы первого (14) и четвертого (17) дополнительных транзисторов связаны со вторым (5) токовым выходом входного дифференциального каскада (1).

2. Каскодный дифференциальный операционный усилитель по п. 1, отличающийся тем, что первый (4) токовый выход входного дифференциального каскада (1) связан со второй (12) шиной источника питания через первый (23) дополнительный токостабилизирующий двухполюсник, а второй (5) токовый выход входного дифференциального каскада (1) связан со второй (12) шиной источника питания через второй (24) дополнительный токостабилизирующий двухполюсник.