Система регулирования тягового усилия для нескольких электросекций

Иллюстрации

Показать всеИзобретение относится к управлению тяговой системой транспортных средств. Система регулирования тягового усилия для нескольких электросекций содержит модуль подачи питания, инверторные/четырехквадратные модули, модуль ввода/вывода, сетевой модуль и модуль устранения ошибок. Инверторные/четырехквадратные модули состоят из высокоскоростной платы, платы дискретизации сигналов и платы импульсного интерфейса. Двусторонний обмен данными между платами, модулем ввода/вывода, хост-процессором, между сетевым модулем и между модулем устранения ошибок реализован посредством высокоскоростной дифференциальной шины LinkPort, посредством высокоскоростной шины, посредством шины CPCI и посредством шины CAN. Сетевой модуль содержит сетевую плату и принимает цифровые сигналы и аналоговые сигналы и отправляет данные. Модуль устранения ошибок содержит плату устранения ошибок и принимает команды на устранение ошибок и сигналы на устранение ошибок. Модуль подачи питания подает питание на инверторные/четырехквадрантные модули, модуль ввода/вывода, сетевой модуль и модуль устранения ошибок. Технический результат изобретения заключается в обеспечении стабильности и надежности в передаче информации системы регулирования тягового усилия для нескольких электросекций. 6 з.п. ф-лы, 18 ил.

Реферат

Область техники

Настоящая заявка относится к области электроники для железных дорог и, в частности, к системе регулирования тягового усилия для нескольких электросекций.

Предпосылки создания настоящего изобретения

Система регулирования тягового усилия для нескольких электросекций является ключевым регулятором мощности нескольких электросекций. Системы регулирования тягового усилия для нескольких электросекций управляют переключателями IGBT четырехквадрантных преобразователей, тормозными прерывателями и тяговыми преобразователями для обеспечения управления, что соответствует требованиям при тяговых/тормозных характеристиках нескольких электросекций.

Структурная схема основной цепи существующей системы регулирования тягового усилия для нескольких электросекций показана на фиг. 1. Однофазный ток высокого напряжения, принятый с помощью пантографа, подается на четырехквадрантный блок посредством вторичной обмотки трансформатора для выпрямления; и выпрямленный постоянный ток высокого напряжения подается на инверторный модуль питания через промежуточную шину постоянного тока. Постоянный ток высокого напряжения после преобразования с помощью инверторного модуля питания подается на тяговый электрический двигатель для управления работой тягового электрического двигателя.

В настоящее время блоки управления систем регулирования тягового усилия для нескольких электросекций представляют собой 32-разрядные хост-процессоры, например, Siemens предлагает Elan SC520 с преобладающей частотой 133 МГц от компании AMD; Bombardier предлагает MC68360 с преобладающей частотой 25 МГц от компании Freescale; ALSTOM предлагает STPC с преобладающей частотой 133 МГц от компании ST; и Zhuzhou Institute предлагает MPC5200D с преобладающей частотой 533 МГц.

В аспекте выбора процессора алгоритма управления Siemens предлагает DSP56002 с преобладающей частотой 100 МГц; Bombardier предлагает DSP56302 с преобладающей частотой 100 МГц; Alston предлагает ADI 21062 с преобладающей частотой 160 МГц; и Zhuzhou Institute предлагает TMS320C6713 с преобладающей частотой 200 МГц.

В настоящее время чипы процессоров, применяемые различными компаниями, представляют собой относительно ранние продукты с относительно устарелыми моделями чипов и системой медленного срабатывания; многие чипы были сняты с конвейера; кроме того, поскольку чипы были сняты с конвейера, затраты на производство, следовательно, увеличиваются.

Сущность настоящего изобретения

Целью настоящей заявки является обеспечение системы регулирования тягового усилия для нескольких электросекций, которая может управлять обеими двумя группами четырехквадрантных модулей питания и двумя группами инверторных модулей питания.

В настоящей заявке использованы следующие технические решения: система регулирования тягового усилия для нескольких электросекций предусмотрена для управления работой инверторных/четырехквадрантных модулей питания тягового преобразователя для нескольких электросекций, в основном содержащая модуль подачи питания, инверторные/четырехквадрантные модули, модуль ввода/вывода, сетевой модуль и модуль устранения ошибок.

Каждый из инверторных/четырехквадрантных модулей в основном состоит из высокоскоростной вычислительной платы, платы дискретизации сигналов и платы импульсного интерфейса.

Плата дискретизации сигналов в основном выполнена с возможностью приема сигналов от датчика наружной установки, импульсных сигналов обратной связи, отправленных платой импульсного интерфейса, и сигналов управления, отправленных высокоскоростной вычислительной платой, и отправки импульсных сигналов на плату импульсного интерфейса, обработанных сигналов извлечения на высокоскоростную вычислительную плату и сигналов релейного управления на модуль ввода/вывода.

Высокоскоростная вычислительная плата в основном выполнена с возможностью приема аналоговых сигналов и цифровых сигналов, извлеченных и обработанных платой дискретизации сигналов, и сигналов управления, отправленных хост-процессором, и отправки сигналов управления на плату дискретизации сигналов и обрабатывающих сигналов на сетевой модуль.

Блок регулирования тягового усилия может управлять двумя группами инверторных модулей питания и двумя группами четырехквадрантных модулей питания платой импульсного интерфейса; и

плата импульсного интерфейса в основном выполнена с возможностью приема сигналов состояния IGBT, отправленных инверторными/четырехквадрантными модулями питания, и сигналов управления IGBT, отправленных платой дискретизации сигналов, и отправки сигналов состояния IGBT на плату дискретизации сигналов и сигналов управления IGBT на инверторные/четырехквадрантные модули питания.

Двусторонний обмен данными между платой дискретизации сигналов и высокоскоростной вычислительной платой реализован посредством высокоскоростной дифференциальной шины LinkPort;

двусторонний обмен данными между платой дискретизации сигналов и модулем ввода/вывода реализован посредством высокоскоростной шины;

двусторонний обмен данными между высокоскоростной вычислительной платой и хост-процессором, между сетевым модулем и хост-процессором и между модулем устранения ошибок и хост-процессором реализован посредством шины CPCI;

двусторонний обмен данными между модулем ввода/вывода и инверторными/четырехквадрантными модулями реализован посредством высокоскоростной шины; и

двусторонний обмен данными между модулем ввода/вывода и сетевым модулем, между модулем ввода/вывода и модулем устранения ошибок реализован посредством шины CAN.

Сетевой модуль содержит сетевую плату. Сетевой модуль принимает цифровые сигналы и аналоговые сигналы, отправленные модулем ввода/вывода, и передает цифровые сигналы и аналоговые сигналы на хост-процессор посредством шины CPCI; принимает сигналы на выполнение команды от хост-процессора посредством шины CPCI и отправляет команды на модуль ввода/вывода для управления модулем ввода/вывода для вывода цифровых сигналов и аналоговых сигналов; управляет взаимодействием данных между блоком интерфейса MVB и внешней шиной MVB; и отправляет данные MVB на хост-процессор посредством шины CPCI, и отправляет данные, подлежащие отправке, посредством хост-процессора на блок интерфейса MVB посредством шины CPCI.

Модуль устранения ошибок содержит плату устранения ошибок; модуль устранения ошибок принимает команды на устранение ошибок и сигналы на устранение ошибок, отправленные хост-процессором посредством шины CPCI; модуль устранения ошибок принимает сигналы на устранение ошибок, отправленные платой дискретизации сигналов посредством высокоскоростной шины; и модуль устранения ошибок выдает аналоговые сигналы на устранение ошибок посредством 32-канальной схемы аналоговых выходных данных.

Модуль подачи питания подает питание на инверторные/четырехквадрантные модули, модуль ввода/вывода, сетевой модуль и модуль устранения ошибок; в то же время, модуль подачи питания подает питание на инверторные/четырехквадрантные модули питания; и в то же время, модуль подачи питания подает питание на встроенный датчик тягового преобразователя.

Кроме того, вследствие присутствия параметров как тока, так и напряжения в сигналах, извлеченных датчиком, плата дискретизации сигналов содержит блок извлечения параметров тока/напряжения и блок управления тактовой синхронизацией; и блок извлечения параметров тока/напряжения состоит из схемы преобразования сигналов и схемы дискретизации ADC, которые соединены друг с другом; и

блок извлечения параметров тока/напряжения содержит несколько каналов, все из которых присоединены к плате дискретизации сигналов; блок управления тактовой синхронизацией присоединен к плате дискретизации сигналов и высокоскоростной вычислительной плате, соответственно; схема преобразования сигналов содержит первый резистор, второй резистор, фильтрующий конденсатор и операционный усилитель; терминал ввода схемы преобразования сигналов присоединен к терминалу датчика дискретизации; терминал ввода схемы преобразования сигналов присоединен к первому терминалу первого резистора; второй терминал первого резистора присоединен к первому терминалу второго резистора и положительному терминалу ввода операционного усилителя, соответственно; второй терминал второго резистора заземлен; обратный терминал ввода операционного усилителя присоединен к терминалу опорного напряжения; терминал вывода операционного усилителя присоединен к схеме дискретизации ADC; и терминал ввода схемы преобразования сигналов заземлен посредством фильтрующего конденсатора.

Кроме того, плата импульсного интерфейса может выполнять функцию фотоэлектрического преобразования; плата импульсного интерфейса содержит схему преобразования уровней PWM, блок преобразования оптического сигнала в электрический, блок преобразования электрического сигнала в оптический и блок интерфейса объединительной платы; схема преобразования уровней PWM присоединена к плате дискретизации сигналов с помощью блока интерфейса объединительной платы; и плата импульсного интерфейса может дополнительно содержать блок автоматической диагностики;

блок автоматической диагностики содержит блок диагностики входных данных и блок диагностики выходных данных;

представлены несколько групп блоков преобразования оптического сигнала в электрический и блоков преобразования электрического сигнала в оптический; каждый из блоков преобразования оптического сигнала в электрический содержит уплотнитель, буферы и схему преобразования оптического сигнала в электрический, блок интерфейса объединительной платы присоединен к уплотнителю с помощью буфера I, и уплотнитель присоединен к схеме преобразования оптического сигнала в электрический с помощью буфера II; и блок преобразования электрического сигнала в оптический содержит уплотнитель, буферы и схему преобразования электрического сигнала в оптический, схема преобразования электрического сигнала в оптический присоединена к уплотнителю с помощью буфера III, и уплотнитель присоединен к блоку интерфейса объединительной платы с помощью буфера IV; и

блок диагностики выходных данных содержит уплотнитель и схему автоматической диагностики выходных данных, терминалы вывода буферов II каждой группы блоков преобразования оптического сигнала в электрический присоединены к терминалу ввода уплотнителя блока автоматической диагностики выходных данных, терминал ввода схемы автоматической диагностики выходных данных присоединен к терминалу вывода буфера II, и терминал вывода уплотнителя присоединен к блоку интерфейса объединительной платы; и блок диагностики входных данных содержит уплотнитель и схему автоматической диагностики входных данных, терминал ввода уплотнителя присоединен к блоку интерфейса объединительной платы, и терминал вывода уплотнителя разделен на несколько каналов, которые присоединены к терминалам ввода буферов III каждой группы блоков преобразования электрического сигнала в оптический, соответственно.

Для достижения прямого обмена данными между устройством управления хост-процессором (CPU) и устройством MVB на панели управления посредством интерфейса шины ISA, преобразователь протоколов между шиной CPCI и шиной ISA выполнен между сетевым модулем и хост-процессором для двустороннего обмена данными; преобразователь протоколов содержит модуль синхронизации расширения интерфейса локальной шины CPCI, модуль синхронизации интерфейса шины ISA, модуль интерфейса синхронизации шины CPCI, соответствующей шине ISA, и модуль управления тактовой синхронизацией; и модуль синхронизации расширения интерфейса локальной шины CPCI обменивается данными с локальной шиной CPCI посредством сигнала адреса/данных AD [31:0], сигнала команды/разрешения байтов C/BE [3:0], сигнала готовности к действию ведомого устройства TRDY, стоп-сигнала передачи данных STOP, сигнала периода цикла FRAME и сигнала готовности к действию ведущего устройства IRDY; модуль синхронизации интерфейса шины ISA обменивается данными с модулем синхронизации расширения интерфейса локальной шины CPCI посредством сигнала разрешения передачи данных S_DATA_VLD, сигнала разрешения адреса ADDR_VLD, сигнала разрешения считывания barx_rd, сигнала разрешения записи barx_wr, сигнала разрешения байта S_CBE, сигнала данных D [31:0] и сигнала адреса A [31:0]; модуль синхронизации интерфейса шины ISA обменивается данными с локальной шиной ISA посредством сигнала данных SD, сигнала адреса SA, сигнала считывания/записи устройства ввода-вывода IOW/IOR, сигнала считывания/записи c устройства памяти MEMR/MEMW, сигнала защелки адреса BALE; модуль интерфейса синхронизации шины CPCI, соответствующей шине ISA, обменивается данными с модулем синхронизации расширения интерфейса локальной шины CPCI посредством сигнала прерывания и повторного соединения USER_STOP; и модуль управления тактовой синхронизацией обеспечивает рабочую синхронизацию для модуля синхронизации расширения интерфейса локальной шины CPCI, модуля синхронизации интерфейса шины ISA и модуля интерфейса синхронизации шины CPCI, соответствующей шине ISA.

По сравнению со стандартной рамкой регулирования тягового усилия, основной корпус системы регулирования тягового усилия для нескольких электросекций представляет собой усиленный высокопрочный корпус, и панели корпуса на двух сторонах усиленного корпуса представляют собой усиленные панели.

Блоки двойных штекеров предусмотрены на узлах между платами системы регулирования тягового усилия для нескольких электросекций и гнездом для платы основного корпуса; каждый из блоков двойных штекеров в основном состоит из основной пластины, стержней и платы переключения; верхняя часть основной пластины присоединена к плате переключения; плата переключения представляет собой L-образную плату, и нижняя левая часть L-образной платы шарнирно присоединена к основной пластине на шарнирной части и может поворачиваться на определенный угол вдоль шарнирной части; на основной пластине предусмотрена направляющая канавка для платы переключения, и направляющая канавка совпадает с нижней частью L-образной платы; два ряда стержней закреплены на нижней части основной пластины, и стержни использованы для присоединения к гнезду для платы; и на одной стороне основной пластины предусмотрено отверстие для болта, прикрепленное к плате.

По сравнению с известным уровнем техники настоящая заявка имеет следующие преимущественные эффекты.

(1) Хост-процессор системы регулирования тягового усилия для нескольких электросекций присоединен к нижней вычислительной плате посредством шины CPCI, и система регулирования тягового усилия содержит высокоскоростную вычислительную плату, сетевой модуль и модуль устранения ошибок; команда проходит на нижнюю вычислительную плату посредством шины CPCI, и в то же время, нижняя вычислительная плата передает информацию о состоянии на хост-процессор посредством шины CPCI для получения общего контроля во внутренней части системы регулирования тягового усилия для нескольких электросекций.

(2) Двусторонний обмен данными между платой дискретизации сигналов и высокоскоростной вычислительной платой реализован посредством высокоскоростной дифференциальной шины LinkPort для получения быстрого контроля на инверторном модуле питания и четырехквадрантном модуле питания.

(3) Двусторонняя связь между сетевой картой и каждой платой модуля ввода/вывода реализована посредством шины CAN, и цифровые и аналоговые сигналы, отправленные каждой из плат модуля ввода/вывода, передаются на хост-процессор посредством шины CPCI для обеспечения стабильности и надежности в передаче информации системы регулирования тягового усилия для нескольких электросекций.

(4) Протокол обмена общими данными представляет собой CAN и тому подобное. По сравнению с LinkPort, данные протоколы имеют низкую скорость извлечения и передачи данных. Согласно настоящей заявке достигают передачи LinkPort между платой дискретизации сигналов и высокоскоростной вычислительной платой. LinkPort, представляющий собой вид низковольтного дифференциального сигнала (LVDS), обладает отличными свойствами, такими как высокая скорость, достаточно низкие потребление энергии, производимый шум и затраты. Передача данных посредством LinkPort в огромной степени улучшает скорость передачи данных, которая может достигать 400 Mбит/с. Таким путем можно реализовать быстрый контроль на блоке управления тяговым усилием.

(5) В системе регулирования тягового усилия для нескольких электросекций используют ведущие чипы управления и концепции новейших разработок, а также используют внедренную и операционную систему реального времени QNX. Операционная система имеет низкий коэффициент наполняемости системных ресурсов и является высокопрофессиональной, тем самым применяемой в конкретных областях техники. Система, будучи емкой, с высоким уровнем безопасности, мгновенной и эффективной при выполнении кода, может решать многие задачи.

(6) Улучшена конструкция корпуса системы регулирования тягового усилия для нескольких электросекций. Основной корпус системы регулирования тягового усилия для нескольких электросекций представляет собой усиленный высокопрочный корпус. На узлах между всеми видами плат и гнездом для платы основного корпуса предусмотрены блоки двойных штекеров.

Краткое описание графических материалов

На фиг. 1 представлена структурная схема основной цепи системы регулирования тягового усилия из предыдущего уровня техники для нескольких электросекций.

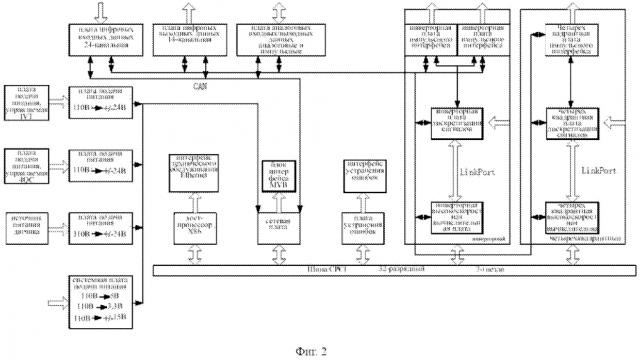

На фиг. 2 представлена структурная схема системы регулирования тягового усилия для нескольких электросекций настоящей заявки.

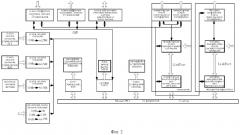

На фиг. 3 представлено схематическое структурное представление платы дискретизации сигналов и высокоскоростной вычислительной платы.

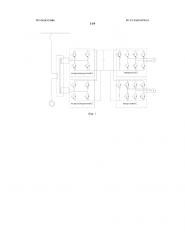

На фиг. 4 представлено схематическое структурное представление схемы преобразования сигналов платы дискретизации сигналов.

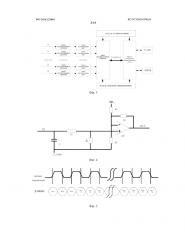

На фиг. 5 представлен схематический вид обмена данными LinkPort.

На фиг. 6 представлена блок-схема приема данных посредством LinkPort платы дискретизации сигналов.

На фиг. 7 представлена блок-схема отправки данных посредством LinkPort платы дискретизации сигналов.

На фиг. 8 представлено схематическое структурное представление платы импульсного интерфейса.

На фиг. 9 представлено схематическое структурное представление схемы блока дистанционного управления платы импульсного интерфейса.

На фиг. 10 представлено схематическое структурное представление схемы автоматической диагностики входных данных платы импульсного интерфейса.

На фиг. 11 представлено схематическое структурное представление схемы автоматической диагностики выходных данных платы импульсного интерфейса.

На фиг. 12 представлено схематическое структурное представление блока двойного штекера.

На фиг. 13 представлено схематическое структурное представление преобразователя протоколов.

На фиг. 14 представлена конкретная диаграмма синхронизации сигналов TRDY, STOP, FRAME и IRDY.

На фиг. 15 представлена частичная диаграмма синхронизации доступа считывания в виде ввода/вывода преобразователем протоколов.

На фиг. 16 представлена блок-схема доступа преобразователем протоколов.

На фиг. 17 представлена архитектура программного обеспечения системы регулирования тягового усилия для нескольких электросекций.

На фиг. 18 представлена блок-схема системы регулирования тягового усилия для нескольких электросекций.

Подробное описание настоящего изобретения

Для четкого объяснения целей, технических решений и преимуществ вариантов осуществления настоящей заявки технические решения в вариантах осуществления настоящей заявки будут описаны четко и полностью со ссылкой на прилагаемые графические материалы в вариантах осуществления настоящей заявки. Очевидно, описанные варианты осуществления представляют собой всего лишь некоторые, но не все варианты осуществления настоящей заявки. На основе вариантов осуществления настоящей заявки все другие варианты осуществления, полученные специалистами в данной области техники без приложения каких-либо творческих усилий, должны попадать в объем охраны настоящей заявки.

Вариант осуществления 1

Предусмотрена система регулирования тягового усилия для нескольких электросекций, которая может управлять двумя группами четырехквадрантных модулей питания и двумя группами инверторных модулей питания одновременно. Согласно фиг. 2 система регулирования тягового усилия для нескольких электросекций в основном содержит модуль подачи питания, инверторный/четырехквадрантный модуль, модуль ввода/вывода, сетевой модуль и модуль устранения ошибок.

Модуль подачи питания состоит из ряда плат подачи питания, включающих 110 В→24 В плату подачи питания, 110 В→5 В плату подачи питания, 110 В→3,3 В плату подачи питания и 110 В→15 В плату подачи питания. Основной функцией модуля подачи питания является подача питания на инверторный/четырехквадрантный модуль, модуль ввода/вывода, сетевой модуль и модуль устранения ошибок, подача питания на инверторные/четырехквадрантные модули питания и подача питания на встроенный датчик тягового преобразователя.

Модуль ввода/вывода обеспечивает внешнее управление вводом-выводом, в основном применяемое для сбора состояний и управления выводом. Модуль ввода/вывода в основном содержит плату цифровых входных данных, плату цифровых выходных данных и плату аналоговых входных/выходных данных. Двусторонний обмен данными между модулем ввода/вывода и инверторным/четырехквадрантным модулем реализован посредством высокоскоростной шины; и двусторонний обмен данными между модулем ввода/вывода и сетевым модулем и модулем устранения ошибок реализован посредством шины CAN.

Функцией инверторного/четырехквадрантного модуля является достижение контроля на тяговом преобразователе и на четырех квадрантах, в основном состоящего из высокоскоростной вычислительной платы, платы дискретизации сигналов и платы импульсного интерфейса. Высокоскоростная вычислительная плата содержит инверторную высокоскоростную вычислительную плату и четырехквадрантную высокоскоростную вычислительную плату. Плата дискретизации сигналов содержит инверторную плату дискретизации сигналов и четырехквадрантную плату дискретизации сигналов. Плата импульсного интерфейса содержит инверторную плату импульсного интерфейса и четырехквадрантную плату импульсного интерфейса.

Инверторная плата дискретизации сигналов в основном выполнена с возможностью приема сигналов от датчика наружной установки, импульсных сигналов обратной связи, отправленных инверторной платой импульсного интерфейса, и сигналов управления, отправленных инверторной высокоскоростной вычислительной платой, и отправки импульсных сигналов на инверторную плату импульсного интерфейса, обработанных сигналов извлечения на инверторную высокоскоростную вычислительную плату, и сигналов релейного управления на модуль ввода/вывода.

Инверторная высокоскоростная вычислительная плата в основном выполнена с возможностью приема аналоговых сигналов и цифровых сигналов, извлеченных и обработанных инверторной платой дискретизации сигналов, и сигналов управления, отправленных хост-процессором, и отправки сигналов управления на инверторную плату дискретизации сигналов и обрабатывающих сигналов на сетевой модуль.

Инверторная плата импульсного интерфейса присоединена максимум к двум группам инверторных модулей питания.

Инверторная плата импульсного интерфейса в основном выполнена с возможностью приема сигналов состояния IGBT, отправленных инверторным модулем питания, и сигналов управления IGBT, отправленных инверторной платой дискретизации сигналов, и отправки сигналов состояния IGBT на инверторную плату дискретизации сигналов и сигналов управления IGBT на инверторный модуль питания.

Двусторонний обмен данными между инверторной платой дискретизации сигналов и инверторной высокоскоростной вычислительной платой реализован посредством высокоскоростной дифференциальной шины LinkPort; двусторонний обмен данными между инверторной платой дискретизации сигналов и модулем ввода/вывода реализован посредством высокоскоростной шины; и двусторонний обмен данными между инверторной высокоскоростной вычислительной платой и сетевым модулем и модулем устранения ошибок реализован посредством шины CPCI.

Четырехквадрантная плата дискретизации сигналов в основном выполнена с возможностью приема сигналов от датчика наружной установки, импульсных сигналов обратной связи, отправленных четырехквадрантной платой импульсного интерфейса, и сигналов управления, отправленных четырехквадрантной высокоскоростной вычислительной платой, и отправки импульсных сигналов на четырехквадрантную плату импульсного интерфейса, обработанных сигналов извлечения на четырехквадрантную высокоскоростную вычислительную плату и сигналов релейного управления на модуль ввода/вывода.

Четырехквадрантная высокоскоростная вычислительная плата в основном выполнена с возможностью приема аналоговых сигналов и цифровых сигналов, извлеченных и обработанных четырехквадрантной платой дискретизации сигналов, и сигналов управления, отправленных хост-процессором, и отправки сигналов управления на четырехквадрантную плату дискретизации сигналов и обрабатывающих сигналов на сетевой модуль.

Четырехквадрантная плата импульсного интерфейса присоединена максимум к двум группам четырехквадрантных модулей питания.

Четырехквадрантная плата импульсного интерфейса в основном выполнена с возможностью приема сигналов состояния IGBT, отправленных четырехквадрантным модулем питания, и сигналов управления IGBT, отправленных четырехквадрантной платой дискретизации сигналов, и отправки сигналов состояния IGBT на четырехквадрантную плату дискретизации сигналов и сигналов управления IGBT на четырехквадрантный модуль питания.

Двусторонний обмен данными между четырехквадрантной платой дискретизации сигналов и четырехквадрантной высокоскоростной вычислительной платой реализован посредством высокоскоростной дифференциальной шины LinkPort; двусторонний обмен данными между четырехквадрантной платой дискретизации сигналов и модулем ввода/вывода реализован посредством высокоскоростной шины; и двусторонний обмен данными между четырехквадрантной высокоскоростной вычислительной платой и сетевым модулем и модулем устранения ошибок реализован посредством шины CPCI.

Сетевой модуль содержит сетевую плату. Сетевой модуль принимает цифровые сигналы и аналоговые сигналы, отправленные модулем ввода/вывода, и передает цифровые сигналы и аналоговые сигналы на хост-процессор посредством шины CPCI; принимает сигналы на выполнение команды от хост-процессора посредством шины CPCI и отправляет команду на модуль ввода/вывода для управления модулем ввода/вывода для вывода цифровых сигналов и аналоговых сигналов; управляет взаимодействием данных между блоком интерфейса MVB и внешней шиной MVB; и отправляет данные MVB на хост-процессор посредством шины CPCI, и отправляет данные, подлежащие отправке, посредством хост-процессора на блок интерфейса MVB посредством шины CPCI.

Модуль устранения ошибок в основном выполнен с возможностью осуществления способа устранения ошибок в режиме реального времени при взаимодействии с другими платами в сети. Модуль устранения ошибок содержит плату устранения ошибок; модуль устранения ошибок принимает команды на устранение ошибок и сигналы на устранение ошибок, отправленные хост-процессором посредством шины CPCI; модуль устранения ошибок принимает сигналы на устранение ошибок, отправленные платой дискретизации сигналов посредством высокоскоростной шины; и модуль устранения ошибок выдает аналоговые сигналы на устранение ошибок посредством 32-канальной схемы аналоговых выходных данных.

Как показано на фиг. 3, целью системы регулирования тягового усилия является управление переключением IGBT внутри преобразователя для реализации преобразования переменного тока на постоянный и снова преобразования постоянного тока на переменный. В ходе операции датчик на схемах извлекает сигналы о параметрах тока и сигналы о параметрах напряжения схем тягового преобразователя, выдает обратно сигналы на высокоскоростную вычислительную плату посредством платы дискретизации сигналов, анализирует и высчитывает сигналы и обеспечивает сигнал управления с учетом результатов вычислений. Поскольку дискретизированные сигналы содержат сигналы о параметрах тока и сигналы о параметрах напряжения, блок извлечения параметров повторного применения тока и напряжения выполнен в настоящей заявке. Причем плата дискретизации сигналов содержит блок извлечения параметров тока/напряжения и блок управления тактовой синхронизацией. Блок извлечения параметров тока/напряжения состоит из схемы преобразования сигналов и схемы дискретизации ADC, которые соединены друг с другом.

Блок извлечения параметров тока/напряжения имеет несколько каналов, все из которых присоединены к плате дискретизации сигналов; и блок управления тактовой синхронизацией присоединен к плате дискретизации сигналов и высокоскоростной вычислительной плате, соответственно. На фиг. 4 представлено схематическое структурное представление схемы преобразования сигналов. Схема преобразования сигналов содержит первый резистор R1, второй резистор R2, фильтрующий конденсатор C и операционный усилитель OP; терминал IN ввода схемы преобразования сигналов присоединен к терминалу извлечения сигналов; терминал IN ввода схемы преобразования сигналов присоединен к первому терминалу первого резистора R1; второй терминал первого резистора R1 присоединен к первому терминалу второго резистора R2 и положительному терминалу ввода операционного усилителя OP, соответственно; второй терминал второго резистора R2 заземлен; обратный терминал ввода операционного усилителя OP присоединен к терминалу опорного напряжения; терминал OUT вывода операционного усилителя присоединен к схеме дискретизации ADC; и терминал IN ввода схемы преобразования сигналов заземлен посредством фильтрующего конденсатора C.

Терминал извлечения сигналов схемы преобразования сигналов представляет собой терминал извлечения сигналов о параметрах напряжения или терминал извлечения сигналов о параметрах тока для извлечения данных, таких как напряжение в сети, ток в сети, ток инвертора и другие данные на поезде. Если терминал ввода схемы преобразования сигналов присоединен к терминалу извлечения сигналов о параметрах напряжения, как первый резистор R1, так и второй резистор R2 представляют собой точные резисторы малой мощности и высокого сопротивления. Если терминал ввода схемы преобразования сигналов присоединен к терминалу извлечения сигналов о параметрах тока, первый резистор R1 представляет собой резистор для ограничения тока высокой мощности и малого сопротивления, и второй резистор R2 представляют собой низкоомный резистор высокой мощности и малого сопротивления. Наконец-то, с использованием операционного усилителя OP путем гибкого выполнения коэффициента усиления пропорциональной схемы операционного усилителя посредством конфигурации резисторов R3, R4 и R5 достигают цели измерения тока или напряжения при вводе любого размера.

Схема преобразования сигналов извлекает сигнал о параметрах тока или сигнал о параметрах напряжения. Дискретизированный сигнал подвергают преобразованию из аналогового сигнала в цифровой посредством схемы дискретизации ADC. После преобразования данные будут переданы на плату дискретизации сигналов.

Плата дискретизации сигналов отправляет данные на высокоскоростную вычислительную плату посредством LinkPort для обработки данных; и высокоскоростная вычислительная плата передает обработанные данные на сторону платы дискретизации сигналов посредством LinkPort.

На фиг. 5 представлен схематический вид обмена данными LinkPort. На фиг. 5 можно увидеть, что для обмена данными LinkPort необходимы извлечение и отправка данных, выполняемые блоком чипа как на переднем фронте, так и на заднем фронте тактовых сигналов, и извлеченные и отправленные данные на каждом промежутке времени представляют собой 4-разрядный дифференциальный сигнал. Принцип отправки и приема LinkPort платы дискретизации сигналов настоящей заявки заключается в том, что данные приняты и отправлены платой дискретизации сигналов как на переднем фронте, так и на заднем фронте тактовых сигналов.

На фиг. 6 и фиг. 7, соответственно, предусмотрены блок-схема приема данных посредством LinkPort платы дискретизации сигналов и блок-схема отправки данных посредством LinkPort платы дискретизации сигналов. Данные приняты и отправлены посредством FPGA внутри платы дискретизации сигналов. DSP на высокоскоростной вычислительной плате представляет собой блок, осуществляющий взаимодействие данных и вычисление данных посредством FPGA. FPGA имеет двухпортовую память RAM. В процессе отправки данных на DSP с помощью FPGA посредством LinkPort шина накопления данных двухпортовой памяти RAM служит в качестве модуля обработки данных FPGA; и шина данных, к которым будет разрешен доступ, служит в качестве модуля обмена данными LinkPort. На фиг.7 видно, что FPGA отправляет данные на DSP посредством LinkPort следующим образом:

(a) отправка посредством FPGA дискретизированного сигнала, принятого от схемы дискретизации ADC на шину накопления данных двухпортовой памяти RAM, т.е. модуля обработки данных FPGA;

(b) упаковка посредством FPGA данных с помощью 4 битов смежных несимметричных сигналов в группе от шины данных, к которым будет разрешен доступ, двухпортовой памяти RAM, т.е. от модуля обмена данными LinkPort;

(c) преобразование посредством FPGA упакованных данных из несимметричного сигнала в дифференциальный сигнал;

(d) предоставление посредством FPGA сигнала передачи данных на переднем фронте и на заднем фронте тактовых сигналов и отправка преобразованных данных на DSP.

В процессе приема данных посредством FPGA от DSP посредством LinkPort шина накопления данных двухпортовой памяти RAM служит в качестве модуля обмена данными LinkPort и шина данных, к которым будет разрешен доступ, служит в качестве модуля обработки данных FPGA. На фиг.6 видно, что FPGA принимает данные от DSP посредством LinkPort следующим образом:

(e) прием посредством FPGA данных, отправленных посредством DSP на переднем фронте и на заднем фронте тактовых сигналов, соответственно;

(f) преобразование посредством FPGA принятых данных из дифференциального сигнала в несимметричный сигнал;

(g) осуществление посредством FPGA разбора данных на преобразованных данных для разбора данных, упакованных с помощью 4 битов в группе в данные блока;

(h) отправка посредством FPGA разобранных данных на шину накопления данных двухпортовой памяти RAM, т.е. модуля обмена данными LinkPort; и

(i) доступ посредством FPGA данных от шины данных, к которым будет разрешен доступ, двухпортовой памяти RAM, т.е. модуля обработки данных FPGA, и введение данных в практику.

Плата импульсного интерфейса в основном выполняет функцию передачи данных в системе регулирования тягового усилия. Плата импульсного интерфейса выполнена с возможностью приема сигналов состояния IGBT, отправленных инверторными/четырехквадрантными модулями питания тягового преобразователя, и сигналов управления IGBT от платы дискретизации сигналов на инверторные/четырехквадрантные модули питания тягового преобразователя, и отправки сигналов управления IGBT инверторных/четырехквадрантных модулей питания тягового преобразователя на плату дискретизации сигналов и сигналов управления IGBT на инверторные/четырехквадрантные модули питания тягового преобразователя.

При приеме вычислительного сигнала управления от высокоскоростной вычислительной платы плата дискретизации сигналов передает вычислительный сигнал управления на плату импульсного интерфейса. Принятый платой импульсного интерфейса сигнал представляет собой электрический сигнал. Во избежание помех из-за мощного электричества и сложной электромагнитной среды на управляющем сигнале IGBT плата импульсного интерфейса