Биполярно-полевой операционный усилитель

Иллюстрации

Показать всеИзобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления сигналов. Технический результат заключается в расширении диапазона изменения отрицательного выходного напряжения ОУ до уровня, близкого к напряжению на второй (12) шине источника питания, и повышении коэффициента ослабления входных синфазных сигналов (Кос.сф) ОУ. Биполярно-полевой операционный усилитель содержит входной дифференциальный каскад (1), шину источника питания, полевой транзистор, резистивную цепь установления статического режима (17), связанную с шиной источника питания, выходной биполярный транзистор. 6 ил.

Реферат

Изобретение относится к области радиоэлектроники и может быть использовано в качестве прецизионного устройства усиления сигналов.

В современной радиоэлектронной аппаратуре находят применение операционные усилители (ОУ) на полевых и биполярных транзисторах, в которых выходными напряжениями входного каскодного дифференциального каскада являются напряжения не на стоках, а на истоках выходных транзисторов [1-5]. Они имеют ряд преимуществ (в сравнении с классическими ОУ) по диапазону рабочих частот, уровню нелинейных искажений, быстродействию и т.п. Заявляемый ОУ относится к данному подклассу устройств.

Для работы в условиях космического пространства, в экспериментальной физике необходимы прецизионные радиационно стойкие ОУ с расширенным диапазоном изменения выходного напряжения при низковольтном питании и повышенным коэффициентом ослабления входных синфазных сигналов. Мировой опыт проектирования устройств данного класса показывает, что решение этих задач возможно с использованием биполярно-полевого технологического процесса [6], обеспечивающего формирование р-канальных полевых и высококачественных n-p-n биполярных транзисторов с радиационной стойкостью до 1 Мрад и потоком нейтронов до 1013 н/см2. Однако для таких ОУ необходима специальная схемотехника, учитывающая ограничения биполярно-полевой технологии [6-10].

Ближайшим прототипом (фиг. 1) заявляемого устройства является операционный усилитель по патенту US 5.218.319 (кроме этого, данная структура представлена в патентах US 6.756.847 fig. 1, US 5.914.639). Он содержит (фиг. 1) входной дифференциальный каскад 1, общая истоковая цепь которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с истоком первого 7 выходного полевого транзистора и базой первого 8 выходного биполярного транзистора, второй 9 токовый выход входного дифференциального каскада 1, связанный с истоком второго 10 выходного полевого транзистора и базой второго 11 выходного биполярного транзистора, вторую 12 шину источника питания, которая связана с объединенными стоками первого 7 и второго 10 выходных транзисторов, цепь динамической нагрузки 13, вход которой 14 соединен с коллектором второго 11 выходного биполярного транзистора, а выход 15 связан с выходом устройства 16 и подключен к коллектору первого 8 выходного биполярного транзистора, резистивную цепь установления статического режима 17, связанную со второй 12 шиной источника питания, первый вход 18 которой подключен к эмиттеру первого 8 выходного биполярного транзистора, а второй вход 19 подключен к эмиттеру второго 11 выходного биполярного транзистора, причем затворы первого 7 и второго 10 выходных транзисторов соединены друг с другом.

Существенный недостаток известного ОУ состоит в том, что в нем не обеспечивается широкий диапазон изменения отрицательного выходного напряжения , что особенно проявляется при низковольтном питании (2,5÷3 В). Кроме этого, известная схема ОУ не обеспечивает также высокое ослабление входных синфазных сигналов и характеризуется повышенной нестабильностью статического режима транзисторов.

Основная задача предлагаемого изобретения состоит в расширении диапазона изменения отрицательного выходного напряжения ОУ до уровня, близкого к напряжению на второй 12 шине источника питания.

Дополнительная задача - повышение коэффициента ослабления входных синфазных сигналов (Кос.сф) ОУ.

Поставленные задачи достигаются тем, что в операционном усилителе фиг. 1, содержащем входной дифференциальный каскад 1, общая истоковая цепь которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с истоком первого 7 выходного полевого транзистора и базой первого 8 выходного биполярного транзистора, второй 9 токовый выход входного дифференциального каскада 1, связанный с истоком второго 10 выходного полевого транзистора и базой второго 11 выходного биполярного транзистора, вторую 12 шину источника питания, которая связана с объединенными стоками первого 7 и второго 10 выходных транзисторов, цепь динамической нагрузки 13, вход которой 14 соединен с коллектором второго 11 выходного биполярного транзистора, а выход 15 связан с выходом устройства 16 и подключен к коллектору первого 8 выходного биполярного транзистора, резистивную цепь установления статического режима 17, связанную со второй 12 шиной источника питания, первый вход 18 которой подключен к эмиттеру первого 8 выходного биполярного транзистора, а второй вход 19 подключен к эмиттеру второго 11 выходного биполярного транзистора, причем затворы первого 7 и второго 10 выходных транзисторов соединены друг с другом, предусмотрены новые элементы и связи - в схему введены первый 20 и второй 21 дополнительные биполярные транзисторы, база первого 20 дополнительного биполярного транзистора соединена с базой первого 8 выходного биполярного транзистора, эмиттер первого 20 дополнительного биполярного транзистора подключен к эмиттеру первого 8 выходного биполярного транзистора, коллектор первого 20 дополнительного биполярного транзистора соединен с затвором первого 7 выходного полевого транзистора, база второго 21 дополнительного биполярного транзистора соединена с базой второго 11 выходного биполярного транзистора, эмиттер второго 21 дополнительного биполярного транзистора соединен с эмиттером второго 11 выходного биполярного транзистора, коллектор второго 21 дополнительного биполярного транзистора соединен с затвором второго 10 выходного полевого транзистора, причем объединенные затворы первого 7 и второго 10 выходных полевых транзисторов связаны с первой 3 шиной источника питания через дополнительный токостабилизирующий двухполюсник 22.

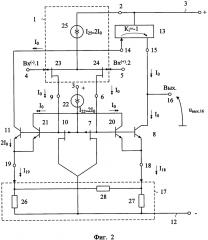

На фиг. 1 показана схема ОУ-прототипа, а на фиг. 2 - схема заявляемого устройства в соответствии с формулой изобретения.

На фиг. 3 показаны частные варианты резистивной цепи установления статического режима 17.

На фиг. 4 приведена схема ОУ, фиг. 2, в среде PSpice на радиационно-зависимых моделях интегральных транзисторов АБМК_1_3 НПО «Интеграл» (г. Минск).

На фиг. 5 представлена амплитудно-частотная характеристика скорректированного ОУ фиг. 4 без обратной связи при сопротивлении резистора 29 (фиг. 3а) R29=250 Ом (или в обозначениях фиг. 4 - R1=250 Ом).

На фиг. 6 представлена амплитудно-частотная характеристика ОУ фиг. 4 без обратной связи при сопротивлении резистора 29 (фиг. 3а) R29=1 Ом (или в обозначениях фиг. 4 - R1=250 Ом).

Компьютерное моделирование показывает, что в заявляемой схеме эмиттеры транзисторов 8, 11, 20, 21 могут, в частном случае, иметь потенциал второй 12 шины источника питания. При этом основные параметры ОУ не деградируют, а максимальная амплитуда отрицательного выходного напряжения ОУ будет близка к напряжению на второй 12 шине источника питания.

Биполярно-полевой операционный усилитель фиг. 2 содержит входной дифференциальный каскад 1, общая истоковая цепь которого 2 связана с первой 3 шиной источника питания, первый 4 и второй 5 входы входного дифференциального каскада 1, первый 6 токовый выход входного дифференциального каскада 1, связанный с истоком первого 7 выходного полевого транзистора и базой первого 8 выходного биполярного транзистора, второй 9 токовый выход входного дифференциального каскада 1, связанный с истоком второго 10 выходного полевого транзистора и базой второго 11 выходного биполярного транзистора, вторую 12 шину источника питания, которая связана с объединенными стоками первого 7 и второго 10 выходных транзисторов, цепь динамической нагрузки 13, вход которой 14 соединен с коллектором второго 11 выходного биполярного транзистора, а выход 15 связан с выходом устройства 16 и подключен к коллектору первого 8 выходного биполярного транзистора, резистивную цепь установления статического режима 17, связанную со второй 12 шиной источника питания, первый вход 18 которой подключен к эмиттеру первого 8 выходного биполярного транзистора, а второй вход 19 подключен к эмиттеру второго 11 выходного биполярного транзистора, причем затворы первого 7 и второго 10 выходных транзисторов соединены друг с другом. В схему введены первый 20 и второй 21 дополнительные биполярные транзисторы, база первого 20 дополнительного биполярного транзистора соединена с базой первого 8 выходного биполярного транзистора, эмиттер первого 20 дополнительного биполярного транзистора подключен к эмиттеру первого 8 выходного биполярного транзистора, коллектор первого 20 дополнительного биполярного транзистора соединен с затвором первого 7 выходного полевого транзистора, база второго 21 дополнительного биполярного транзистора соединена с базой второго 11 выходного биполярного транзистора, эмиттер второго 21 дополнительного биполярного транзистора соединен с эмиттером второго 11 выходного биполярного транзистора, коллектор второго 21 дополнительного биполярного транзистора соединен с затвором второго 10 выходного полевого транзистора, причем объединенные затворы первого 7 и второго 10 выходных полевых транзисторов связаны с первой 3 шиной источника питания через дополнительный токостабилизирующий двухполюсник 22.

На фиг. 2 входной дифференциальный каскад 1 реализован на входных полевых транзисторах 23, 24 и источнике опорного тока 25.

В частном случае резистивная цепь установления статического режима 17 может содержать вспомогательные резисторы 26, 27 и 28 (фиг. 3а) или один вспомогательный резистор 29 (фиг. 3б).

Для уменьшения выходного сопротивления ОУ к выходу 16 схемы, фиг. 2, может подключаться буферный усилитель Gain=1 (фиг. 4).

Рассмотрим работу ОУ, фиг. 2.

Статический режим транзисторов схемы, фиг. 2, устанавливается источниками опорного тока 25 и 22. При этом токи стока (Ici) и токи коллекторов (Iкi) транзисторов схемы определяются с учетом местной отрицательной обратной связи уравнениями Кирхгофа:

где I25, I22 - токи источника опорного тока 25 и дополнительного токостабилизирующего двухполюсника 22.

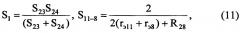

Дифференциальный коэффициент усиления по напряжению схемы ОУ фиг. 2 определяется произведением:

где uвых.16 - приращение выходного напряжения ОУ в узле 16, вызванное изменением напряжения (uвх.=uвх.4.5) между входами 4 и 5 ОУ;

- коэффициент преобразования напряжения между входами 4

и 5 ОУ (uвх) в напряжение между первым 6 и вторым 9 токовыми выходами входного дифференциального каскада 1;

- коэффициент передачи дифференциального напряжения u9-6 между узлами 9 и 6 на выход ОУ 16.

Причем

где Rэкв.9-6 - эквивалентное дифференциальное сопротивление между узлами 9 и 6;

Rэкв.16 - эквивалентное сопротивление в высокоимпедансном выходном узле ОУ 16.

Причем в формулах (9) и (10):

Где S23, S24 - крутизны стокозатворной характеристики соответствующих полевых транзисторов 23, 24;

R28 - сопротивление резистора 28;

rэ11=rэ8=ϕт/I0 - сопротивления эмиттерных переходов транзисторов 11 и 8;

ϕт=25 мВ - температурный потенциал.

Численное значение эквивалентного сопротивления Rэкв.16 близко к сопротивлениям закрытых коллекторов переходов выходных транзисторов цепи динамической нагрузки 13, выполненной в виде токового зеркала, и транзистора 8, а сопротивление Rэкв.9-6 определяется, в основном, входным сопротивлением цепи истока полевых транзисторов 7 и 10:

Как следствие, коэффициент усиления по напряжению разомкнутого ОУ, фиг. 2, получается достаточно большим (≈103, фиг. 6).

В заявляемой схеме ОУ (в сравнении с прототипом) повышается также коэффициент ослабления входных синфазных сигналов (Кос.сф). Данный эффект объясняется повышенной симметрией схемы ОУ фиг. 2 и введением за счет новых элементов отрицательной обратной связи по синфазному сигналу в выходной цепи входного дифференциального каскада 1 (транзисторы 21 и 20) [11].

За счет высокой симметрии схемы ОУ и введения отрицательной обратной связи напряжение смещения нуля заявляемого ОУ (Uсм) измеряется микровольтами (при условии высокой идентичности используемых транзисторов и идеальном токовом зеркале 13).

Компьютерное моделирование показывает, что в заявляемой схеме эмиттеры транзисторов 8, 11, 20, 21 могут, в частном случае, иметь потенциал второй 12 шины источника питания. При этом основные параметры ОУ не деградируют, а максимальная амплитуда отрицательного выходного напряжения ОУ будет близка к напряжению на второй 12 шине источника питания.

Таким образом, заявляемое устройство имеет существенные преимущества в сравнении с ОУ-прототипом.

Источники и информации

1. Патент US 5.218.319, fig. 1, fig. 3а.

2. Патент US 7.639.079, fig. 10.

3. Патент US 6.756.847, fig. 1.

4. Патент US 7.142.056, fig. 1.

5. Патент US 5.914.639.

6. Элементная база радиационно-стойких информационно-измерительных систем: монография / Н.Н. Прокопенко, О.В. Дворников, С.Г. Крутчинский; под общ. ред. д.т.н. проф. Н.Н. Прокопенко; ФГБОУ ВПО «Южно-Рос. гос. ун-т. экономики и сервиса». - Шахты: ФГБОУ ВПО «ЮРГУЭС», 2011. - 208 с.

7. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 1 /О. Дворников // Компоненты и технологии, №6, 2005, http://kit-e.ru/articles/device/2005_6_218.php.

8. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 2 /О. Дворников // Компоненты и технологии, №7, 2005, http://kit-e.ru/articles/device/2005_7_216.php.

9. Проблемы проектирования аналоговых устройств с входными полевыми транзисторами. Часть 3 /О. Дворников // Компоненты и технологии, №8, 2005, http://kit-e.ru/articles/device/2005_8_184.php.

10. Схемотехника биполярно-полевых аналоговых микросхем. Часть 4. Источники тока для особых применений / О. Дворников // Chip News, №3(96), 2005. - С. 66-68.

11. Архитектура и схемотехника дифференциальных усилителей с повышенным ослаблением синфазных сигналов: монография / Н.Н. Прокопенко, С.В. Крюков. - Шахты: ГОУ ВПО «ЮРГУЭС», 2008. - 329 с.

Биполярно-полевой операционный усилитель, содержащий входной дифференциальный каскад (1), общая истоковая цепь которого (2) связана с первой (3) шиной источника питания, первый (4) и второй (5) входы входного дифференциального каскада (1), первый (6) токовый выход входного дифференциального каскада (1), связанный с истоком первого (7) выходного полевого транзистора и базой первого (8) выходного биполярного транзистора, второй (9) токовый выход входного дифференциального каскада (1), связанный с истоком второго (10) выходного полевого транзистора и базой второго (11) выходного биполярного транзистора, вторую (12) шину источника питания, которая связана с объединенными стоками первого (7) и второго (10) выходных транзисторов, цепь динамической нагрузки (13), вход которой (14) соединен с коллектором второго (11) выходного биполярного транзистора, а выход (15) связан с выходом устройства (16) и подключен к коллектору первого (8) выходного биполярного транзистора, резистивную цепь установления статического режима (17), связанную со второй (12) шиной источника питания, первый вход (18) которой подключен к эмиттеру первого (8) выходного биполярного транзистора, а второй вход (19) подключен к эмиттеру второго (11) выходного биполярного транзистора, причем затворы первого (7) и второго (10) выходных транзисторов соединены друг с другом, отличающийся тем, что в схему введены первый (20) и второй (21) дополнительные биполярные транзисторы, база первого (20) дополнительного биполярного транзистора соединена с базой первого (8) выходного биполярного транзистора, эмиттер первого (20) дополнительного биполярного транзистора подключен к эмиттеру первого (8) выходного биполярного транзистора, коллектор первого (20) дополнительного биполярного транзистора соединен с затвором первого (7) выходного полевого транзистора, база второго (21) дополнительного биполярного транзистора соединена с базой второго (11) выходного биполярного транзистора, эмиттер второго (21) дополнительного биполярного транзистора соединен с эмиттером второго (11) выходного биполярного транзистора, коллектор второго (21) дополнительного биполярного транзистора соединен с затвором второго (10) выходного полевого транзистора, причем объединенные затворы первого (7) и второго (10) выходных полевых транзисторов связаны с первой (3) шиной источника питания через дополнительный токостабилизирующий двухполюсник (22).