Цифровое устройство для формирования последовательностей управляющих сигналов с последовательным переносом информации

Иллюстрации

Показать всеИзобретение относится к области цифровой техники. Технический результат заключается в повышении быстродействия цифрового устройства. Технический результат достигается за счет того, что устройство содержит последовательно соединенные блоки, принимающие при воздействии тактовых сигналов одну и ту же последовательность внутренних состояний; при этом переход к очередным состояниям осуществляется под действием активного уровня на соответствующих им входах и очередным состояниям соответствуют определенные выходы; после сигнала на очередных входах последующего блока, являющихся выходами предыдущего блока, соответствующими определенным его состояниям, переключающего блок в очередное внутреннее состояние «J» в данном цикле предыдущего блока, следующим сигналом, переключающим последующий блок в следующее внутреннее состояние (J+1) в следующем цикле предыдущего блока, является сигнал предыдущего блока, соответствующий другому его внутреннему состоянию, предшествующий по циклу предыдущего блока сигналу, переключающему последующий блок в состояние «J»; при этом выходами упомянутого предыдущего блока и входами упомянутого последующего блока являются выходы триггеров предыдущего блока, определяющие его внутреннее состояние. 5 ил., 3 табл.

Реферат

Устройство относится к области цифровой техники и может быть использовано в вычислительной технике, системах передачи и обработки информации, при построении различного рода управляющих автоматов циклического действия, то есть устройств, принимающих при воздействии входных сигналов одну и ту же последовательность внутренних состояний (состояний элементов памяти), предназначенных для формирования последовательностей управляющих сигналов.

Наиболее типичными, простыми и наиболее исследованными устройствами такого вида являются счетчики и распределители импульсов, а также более сложные управляющие автоматы циклического действия с произвольным алгоритмом функционирования (например, устройства управления процессоров, формирующие на своих выходах последовательности сигналов, управляющие операционными устройствами, генераторы кодов, а также кодирующие и декодирующие устройства систем передачи информации).

Устройства циклического действия традиционно выполняются в виде счетчика импульсов совместно с дешифратором. Наиболее распространенным примером такого подхода являются распределители импульсов. При этом важной является возможность использования логических элементов, входящих в счетчик, для реализации дешифратора, что позволяет уменьшать количество оборудования.

Название предлагаемого изобретения выбрано исходя из того, что предлагаемое устройство при частной реализации может выполнять функции всех вышеперечисленных устройств циклического действия, то есть обладать универсальностью, позволяет строить различные его варианты и выбирать наиболее подходящий с учетом используемой элементной базы (например, с учетом ограничений на реализацию логических элементов и элементов памяти при разработке микросхем), а также других требуемых параметров, отличается оригинальностью структуры. То есть название принято обобщающего характера и не отражает частную функцию (счетчик, распределитель, устройство управления и т.п.), а отражает общее понятие (выражающее функцию), охватывающее разные частные формы его реализации (см. «Правила составления, подачи и рассмотрения заявки…». П. 3.3.1 (6)).

Показателями технического уровня цифрового устройства циклического действия, как и других видов цифровых устройств, являются используемое для его реализации количество оборудования, быстродействие, возможность реализовать многоразрядные (многоблочные) устройства без дополнительных усложнений структуры, регулярность (однородность) структуры.

Известны устройства, которые обеспечивают высокие показатели по разным параметрам из перечисленных.

Это, например, устройство в соответствии с патентом на изобретение №2397610 («Цифровое устройство для формирования последовательностей управляющих сигналов», зарегистрированное 20.08.2010 г.). Пример его реализации приведен на Фиг. 1. Выберем его в качестве прототипа.

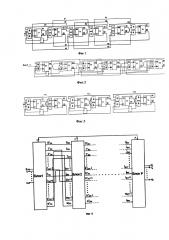

Другое широко распространенное устройство такого типа - счетчик с последовательной передачей информации, состоящий из последовательно соединенных Τ-триггеров (мм., например: Опадчий Ю.Ф., Глудкин О.П., Гуров А.И. Аналоговая и цифровая электроника. Полный курс. М.: Горячая линия - Телеком. 2000. Рис. 17.8, рис. 17.31). На Фиг. 3 приведена более детальная схема, в которой раскрыта структура триггеров ТТ1-ТТ3 в соответствии с рис. 17.4а указанного источника. Используем его в качестве аналога.

В изобретении №2397610 (прототипе) описано цифровое устройство для формирования последовательностей управляющих сигналов, содержащее два или более последовательно соединенных блоков, являющихся последовательностными устройствами, имеющими по несколько входов и выходов, каждый из которых соответствует одному внутреннему состоянию, меняющими в одной очередности свои внутренние состояния только при воздействии активного уровня на один из очередных входов и не меняющими внутреннее состояние при переходе активного уровня в пассивный, что в сочетании с оригинальной организацией связей между выходами и входами блоков, таких, что после сигнала на очередном входе последующего блока, переключающем этот блок в очередное внутреннее состояние «j» в данном цикле предыдущего блока, следующим сигналом, переключающим последующий блок в следующее внутреннее состояние (j+1) в следующем цикле предыдущего блока, является сигнал, предшествующий по циклу предыдущего блока сигналу, переключающему последующий блок во внутреннее состояние «j».

Это устройство имеет тот недостаток, что осуществляет сквозной перенос информации по цепочкам последовательно включенных конъюнкторов (схем «И»), когда выход предыдущего конъюнктора подается на один из входов последующего, что приводит к затуханию (уменьшению) уровня сигнала, так как конъюнкторы не имеют усиления. Это ограничивает построение многоблочных (многоразрядных) структур, например счетчиков с большими коэффициентами счета, распределителей с большим количеством выходов, а в общем случае формирование длинных последовательностей управляющих сигналов.

Такого недостатка не имеет устройство по Фиг. 3 (аналог), так как реализует последовательный перенос информации, когда информация распространяется путем последовательного переключения Τ-триггеров в соответствии с двоичным кодом. Но это устройство использует большее количество оборудования и имеет невысокое быстродействие.

Предлагаемое устройство отличается от прототипа тем, что однопроводные (единичные) шины прототипа, связывающие выходы и входы блоков, каждая из которых соответствует одному из устойчивых состояний блока, заменяются на комбинацию шин, являющихся выходами триггеров блока, однозначно определяющих это же состояние. При этом устройство превращается в устройство с последовательным переносом, в котором в отличие от прототипа исключено затухание сигнала, но уменьшается его быстродействие по сравнению с прототипом. В то же время по сравнению с аналогом значительно уменьшается количество оборудования и увеличивается быстродействие.

Вышеописанное поясним на примерах.

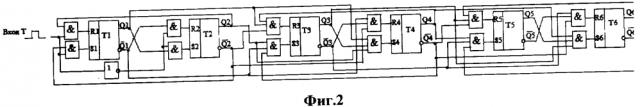

На Фиг. 1 приведена схема счетчика, ярко иллюстрирующая прототип, так как за счет выбора алгоритма функционирования блоков и оригинальной организации соединений между их входами и выходами позволяет экономить количество оборудования и повысить быстродействие. Схема состоит из трех блоков и имеет коэффициент счета КСЧ=18. При этом все блоки, кроме первого, имеют КСЧ=3, вместо двух в схеме на Т-триггерах (см. описание изобретения №2397610).

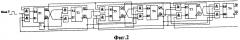

На Фиг. 2 приведена схема счетчика, иллюстрирующая предлагаемое устройство, аналогичная по функции схеме Фиг. 1 с КСЧ=18, но реализующая последовательный перенос информации. Каждый из выходов «I» блоков Б1 (I11, I21, I31, I41), Б2 (I12, I22, I32, I42) заменяется, как уже было сказано, на выходы триггеров, однозначно определяющих устойчивое состояние блока, которому соответствует данный выход. В обозначениях выходов первая цифра - это номер выхода, а вторая - номер блока.

Счетчики синтезированы с помощью таблиц переходов 1, 2, 3 (для блоков из триггеров T1 и Т2, T3 и Т4, Т5 и Т6 соответственно для обеих схем). В клетках таблицы указаны номера символов (нулей и единиц), вызывающих соответствующее состояние (в знаменателе номер последнего символа, при котором существует состояние).

Логические функции, описывающие цепи, воздействующие на входы триггеров и на выходы блоков Б1 и Б2 в схеме Фиг. 1

Логические функции, описывающие цепи в схеме Фиг. 2, воздействующие на входы триггеров T3 и Т4 (соответствуют блоку 2 Фиг. 1), Т5 и Т6 (соответствуют блоку 3 Фиг. 1), получаются путем замены переменных «I», отображающих выходы блоков в схеме Фиг. 1, на конъюнкцию переменных, соответствующих выходам триггеров, однозначно отображающих устойчивое состояние блока, которому соответствует данный выход «I» в схеме Фиг. 1. В этом состоянии блока эти выходы триггеров формируют единицу, и поэтому их конъюнкция равна единице. Логические функции, описывающие входные цепи триггеров первого блока Фиг. 1 F(R2), F(S1), F(S2), F(R1), остаются неизменными и для Фиг. 2 (для триггеров Т1 и Т2, соответствующих блоку 1 Фиг. 1) из-за того, что на его входы воздействуют не выходы предыдущего блока, а тактовые сигналы. При этом выходы предыдущего блока, соединенные со входами последующего блока, вместо однопроводных шин будут представлены двухпроводными, соответственно: I11 - шинами ; I21 - Q1, ; I31 - Q1,Q2; I41 - ; I12 - ; I22 - Q3, ; I32 - Q3,Q4; I42 - , Q4.

Таблицы переходов применительно к схеме Фиг. 2 используются с учетом этого соответствия. Логические функции для остальных блоков Фиг. 2 имеют вид:

Счетчик Фиг. 2 с последовательным переносом информации, иллюстрирующий предлагаемое изобретение, за полный цикл фиксирует KS=36 символов (коэффициент счета ), что следует непосредственно из таблиц переходов.

На Фиг. 3 приведена схема счетчика импульсов также с последовательным переносом, использующая Т-триггеры (аналог), состоящая также из трех блоков с тем же составом вентилей (кроме дополнительного инвертора в блоках ТТ2 и TT3), но она фиксирует только KS=16 символов (К=23=8). Для получения даже К=16, что меньше К=18, требуется добавить один блок, то есть экономия (нижняя оценка). Для получения же К=32, большего 18, необходимо два блока; экономия (верхняя оценка).

Коэффициент счета счетчика по Фиг. 2 при «n» блоках

По Фиг. 3

Предлагаемая схема позволяет в отличие от прототипа использовать большое количество разрядов (блоков) ввиду того, что, как указано выше, отсутствует затухание сигнала при переходе от разряда к разряду (от блока к блоку). Количество используемого оборудования в этой схеме примерно такое же, как в прототипе (это видно непосредственно из схем). Регулярность структуры (однородность) обеих схем высокая (они состоят из одинаковых блоков). Предлагаемая схема проигрывает прототипу по быстродействию, так как это определяется самим принципом последовательного переноса информации от разряда к разряду и свойственно всем схемам с последовательным переносом. Но по отношению к схеме с последовательным переносом (аналогу Фиг. 3) она обладает преимуществом по количеству используемого оборудования (экономия порядка 30-40%, см. выше) и быстродействию (в ее каскадах отсутствует инвертор, создающий дополнительную задержку при переключениях). То есть эта схема улучшает один из параметров прототипа и все основные параметры аналога. При этом она использует характер связей блоков (каскадов) прототипа, но использует другие по составу шины входов и выходов, соединяющиеся с другими точками схем блоков, что приводит к описанным преимуществам. По существу реализуется новый, более совершенный, чем в аналоге, принцип организации последовательного переноса, позволяющий улучшить все его основные параметры, использующий такой же порядок соединений выходов и входов блоков, как в прототипе. Но в отличие от прототипа выходы и входы многоканальные и соединяются с другими точками схем блоков. Представим предлагаемое изобретение в виде обобщенной схемы Фиг. 4, отражающей общее понятие, так же как в прототипе, охватывающем разные частные формы его реализации (см. «Правила составления, подачи и рассмотрения заявки…» П. 3.3.1 (6)). То есть эта схема отражает сущность изобретения в обобщенном виде.

Устройство содержит блоки 1, 2, …Р. Входы и выходы блоков, кроме входов входного блока и выходов выходного блока, представляют собой не однопроводные шины, как в Фиг. 1, а комбинации определенных выходов триггеров, которые однозначно определяют устойчивое состояние блока, соответствующее этой единичной шине в Фиг. 1. Порядок соединения комбинации входов и выходов такой же, как и единичных, соответствующих им в прототипе.

Входной блок 1 имеет номера входов 01, 11, …n1, где нижний индекс является номером блока. Эти входы полностью идентичны входам прототипа. Выходной блок «Р» имеет номера выходов , где нижний индекс - номер блока. Эти выходы также идентичны выходам прототипа. Блок 1 имеет комбинации выходов: (в нижнем индексе 1 - номер блока, «с» - означает комбинацию, «t» - триггеров). Выходы других блоков, кроме последнего, организованы аналогично, связаны с последующим блоком подобным образом, выполняют по отношению к нему такую же функцию, но в обозначении в нижнем индексе должны иметь вместо единицы свой номер блока.

Каждая комбинация выходов является выходами триггеров, состояние которых однозначно определяет очередное устойчивое состояние этого блока, которые переводят последующий блок в очередное состояние в соответствии с его комбинацией входов, с которой они соединены.

Комбинации входов блоков (кроме первого) 0ict, 1ict, …nict, где i - номер блока. Каждая комбинация является той комбинацией выходов предыдущего блока, с которой она соединяется.

Схема Фиг. 4 является обобщенной, то есть в общем виде отображающей суть изобретения (моделью), и при задании конкретных ее параметров приводит к частному решению.

Схема Фиг. 2 является таким частным решением при числе блоков Ρ=3, числе выходов, числе входов и числе состояний блоков, равном 4 (, где i - номер блока, М=4). Для первого блока номера выходов: , для второго - . Для второго блока номера входов: 02ct, 12ct, 22ct, 32ct. Для третьего 03ct, 13ct, 23ct. 33ct. Входы первого блока реализуются входом тактовых импульсов. Выходы третьего блока в данном примере не формируются, так как это тривиальная задача, не требующая иллюстрации.

Точно так же обобщенная схема (модель) может служить основой для любой другой конкретной схемы при задании любых других значений Р, n, М. Это приводит к многообразию конкретных схем, обладающих указанными преимуществами перед известными схемами.

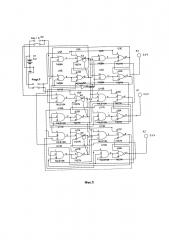

Функционирование схемы, приведенной на Фиг. 2, было проверено путем моделирования на ПЭВМ с использованием программы Electronics Workbench 6.0. На Фиг. 5 приводится распечатка схемы, полностью соответствующей схеме Фиг. 2, подвергавшейся моделированию, с использованием изображений логических элементов в соответствии с американским стандартом ANSI, принятым в этой программе.

В схеме раскрыта структура RS-триггеров на основе двух элементов «ИЛИ-НЕ», используется переключатель S2 для формирования входных сигналов, переключатель S1 для начальной установки RS-триггеров, а также индикаторы состояний триггеров (обозначены буквой X). Схема состоит из трех блоков, полностью идентичных по структуре блокам Б1-Б3 на Фиг. 2. При этом каждый RS-триггер выполнен на двух элементах «ИЛИ-НЕ»: T1(U3A, U3B), T2(U3C, U2A) - блок Б1; T3 (U5A, U5B), Т4 (U5C, U8A) - блок Б2; T5 (U7A, U7B), Т6 (U7C, U9A) - блок Б3. Инвертор - U6A.

Схема функционирует в полном соответствии с таблицами переходов (таблица 1 - блок Б1, таблица 2 - блок Б2, таблица 3 - блок Б3), обеспечивая заданный коэффициент счета КСЧ=18. В таблицах переходов цифрами обозначены номера импульсов и пауз (символов), поступивших на вход для достижения данного состояния (всего 36 символов за цикл - 18 импульсов и 18 пауз).

Цифровое устройство для формирования последовательностей управляющих сигналов с последовательным переносом, содержащее два или более последовательно соединенных блоков, являющихся последовательностными устройствами, принимающими при воздействии тактовых сигналов одну и ту же последовательность внутренних состояний; при этом переход к очередным состояниям осуществляется под действием активного уровня на соответствующих им входах и очередным состояниям соответствуют определенные выходы, а связи между выходами и входами соседних блоков такие, что после сигнала на очередных входах последующего блока, являющихся выходами предыдущего блока, соответствующими определенным его состояниям, переключающего последующий блок в очередное внутреннее состояние J в данном цикле предыдущего блока, следующим сигналом, переключающим последующий блок в следующее внутреннее состояние J+1 в следующем цикле предыдущего блока, является сигнал предыдущего блока, соответствующий другому его внутреннему состоянию, предшествующий по циклу предыдущего блока сигналу, переключающему последующий блок в состояние J, отличающееся тем, что выходами данного предыдущего блока, соответствующими его очередному состоянию, и соответствующими им входами последующего блока являются выходы триггеров предыдущего блока, определяющие его состояние.