Схема, способ и устройство для пробуждения главного блока микроконтроллера

Иллюстрации

Показать всеИзобретение относится к области микроконтроллеров. Техническим результатом является пробуждение главного блока микроконтроллера (MCU). Раскрыта схема для пробуждения главного блока микроконтроллера (MCU), содержащая главный MCU, микросхему периферийного интерфейса и микросхему периферийной обработки, в которой микросхема периферийной обработки соединена с главным MCU посредством микросхемы периферийного интерфейса; линия синхронизации главного MCU соединена с сигналом ведущего генератора синхроимпульсов, а каждая из линии синхронизации микросхемы периферийной обработки и линии синхронизации микросхемы периферийного интерфейса соединена с сигналом ведомого генератора синхроимпульсов, причем сигнал ведущего генератора синхроимпульсов и сигнал ведомого генератора синхроимпульсов являются различными сигналами синхроимпульсов, таким образом, что микросхема периферийного интерфейса и микросхема периферийной обработки остаются в нормальном рабочем состоянии, когда главный MCU переходит в состояние глубокого сна; и микросхема периферийного интерфейса выполнена с возможностью контроля объема данных, передаваемых микросхемой периферийной обработки в микросхему периферийного интерфейса, и передачи сигнала пробуждения в главный MCU, если объем данных превышает порог. 4 н. и 9 з.п. ф-лы, 6 ил.

Реферат

[0001] Данная заявка основана на Заявке на патент Китая № CN201510370154.4, зарегистрированной Государственным Ведомством по интеллектуальной собственности Народной Республики Китай 29 июня 2015 г., и притязает на ее приоритет, причем ее содержание полностью включено в настоящий документ путем ссылки.

ОБЛАСТЬ ТЕХНИКИ

[0002] Изобретение относится к области технологий устройств и, в частности, к схеме, способу и устройству для пробуждения главного блока микроконтроллера (MCU).

УРОВЕНЬ ТЕХНИКИ

[0003] При разработке встроенного системного программного обеспечения разработчики переключают систему в режим низкого энергопотребления в бездействующем состоянии, чтобы сократить энергопотребление и сэкономить электроэнергию, причем микросхема Блока Микроконтроллера (MCU) переходит в состояние сна или состояние глубокого сна. В состоянии глубокого сна общие периферийные устройства MCU (такие как Последовательный Периферийный Интерфейс SPI, Универсальный Асинхронный Приемопередатчик UART и блок Аналого-Цифрового преобразователя АЦП) могут не работать нормально, при этом другие микросхемы могут не связываться с MCU посредством последовательного интерфейса. Только внешнее прерывание и таймерное прерывание могут пробудить MCU.

[0004] Еще в одном сценарии система интеллектуальных устройств может входить в режим низкого энергопотребления в бездействующем состоянии, чтобы сокращать энергопотребление и приводить к рациональному использованию энергии. MCU может переходить в режим сна или режим глубокого сна (готовности/пониженного энергопотребления). Когда MCU переходит в режим глубокого сна, ведущий генератор синхроимпульсов перестает работать, при этом некоторые внутренние периферийные устройства (например, блок UART, блок SPI, блок шины для Соединения Микросхем (шины I2C), блок АЦП и блок Широтно-Импульсной Модуляции (ШИМ) и т.д.) могут оказаться неспособными работать, если они зависят от ведущего генератора синхроимпульсов. Таким образом, главный MCU может не принять своевременно данные, передаваемые от блока UART, блока SPI, блока шины I2C и т.д.

СУЩНОСТЬ ИЗОБРЕТЕНИЯ

[0005] С целью решения проблем на предшествующем уровне техники в изобретении предлагаются схема, способ и устройство для пробуждения главного MCU таким образом, что главный MCU в состоянии глубокого сна может быть своевременно пробужден для передачи и приема данных.

[0006] В соответствии с вариантами осуществления первого аспекта изобретения предлагается схема для пробуждения главного MCU, при этом схема содержит главный MCU, микросхему периферийного интерфейса и микросхему периферийной обработки;

микросхема периферийной обработки соединена с главным MCU посредством микросхемы периферийного интерфейса;

линия синхронизации главного MCU соединена с сигналом ведущего генератора синхроимпульсов, а каждая из линии синхронизации микросхемы периферийной обработки и линии синхронизации микросхемы периферийного интерфейса соединена с сигналом ведомого генератора синхроимпульсов таким образом, что микросхема периферийного интерфейса и микросхема периферийной обработки остаются в нормальном рабочем состоянии, когда главный MCU переходит в состояние глубокого сна;

микросхема периферийного интерфейса выполнена с возможностью контроля объема данных, передаваемых микросхемой периферийной обработки в микросхему периферийного интерфейса, и передачи сигнала пробуждения в главный MCU, если объем данных превышает порог.

[0007] В одном из вариантов осуществления передача микросхемой периферийного интерфейса сигнала пробуждения в главный MCU включает в себя:

передачу микросхемой периферийного интерфейса сигнала пробуждения в виде сигнала прерывания в главный MCU.

[0008] В одном из вариантов осуществления дальнейшее нахождение микросхемы периферийного интерфейса и микросхемы периферийной обработки в нормальном рабочем состоянии включает в себя:

передачу данных между микросхемой периферийной обработки и микросхемой периферийного интерфейса посредством Прямого Доступа к Памяти DMA.

[0009] В одном из вариантов осуществления микросхема периферийного интерфейса представляет собой блок Универсального Асинхронного Приемопередатчика UART, блок Последовательного Периферийного Интерфейса SPI, блок шины для Соединения Микросхем I2C или блок Bluetooth;

микросхема периферийной обработки представляет собой блок Аналого-Цифрового преобразователя АЦП, блок Широтно-Импульсной Модуляции ШИМ, блок обработки видеосигналов или блок обработки звуковых сигналов.

[0010] В изобретении дополнительно предлагается способ пробуждения главного Блока Микроконтроллера MCU, причем данный способ применяется в устройстве, содержащем главный MCU, микросхему периферийного интерфейса и микросхему периферийной обработки, и включает в себя:

настройку главного MCU на нахождение в состоянии глубокого сна и настройку микросхемы периферийного интерфейса и микросхемы периферийной обработки на нахождение в нормальном рабочем состоянии;

контроль объема данных, передаваемых микросхемой периферийной обработки в микросхему периферийного интерфейса; и

если объем данных превышает порог, передачу сигнала пробуждения в главный MCU.

[0011] В одном из вариантов осуществления передача сигнала пробуждения в главный MCU включает в себя:

передачу сигнала пробуждения в виде сигнала прерывания в главный MCU.

[0012] В одном из вариантов осуществления настройка главного MCU на нахождение в состоянии глубокого сна и настройка микросхемы периферийного интерфейса и микросхемы периферийной обработки на нахождение в нормальном рабочем состоянии включает в себя:

соединение линии синхронизации главного MCU с сигналом ведущего генератора синхроимпульсов;

соединение каждой из линии синхронизации микросхемы периферийной обработки и линии синхронизации микросхемы периферийного интерфейса с сигналом ведомого генератора синхроимпульсов; и

управление сигналом ведущего генератора синхроимпульсов и сигналом ведомого генератора синхроимпульсов, чтобы настроить главный MCU на нахождение в состоянии глубокого сна и настроить микросхему периферийной обработки и микросхему периферийного интерфейса на нахождение в нормальном рабочем состоянии.

[0013] В одном из вариантов осуществления настройка микросхемы периферийного интерфейса и микросхемы периферийной обработки на нахождение в нормальном рабочем состоянии включает в себя:

настройку микросхемы периферийной обработки и микросхемы периферийного интерфейса на передачу данных между друг другом посредством Прямого Доступа к Памяти DMA.

[0014] В одном из вариантов осуществления микросхема периферийного интерфейса представляет собой блок Универсального Асинхронного Приемопередатчика UART, блок Последовательного Периферийного Интерфейса SPI, блок шины для Соединения Микросхем I2C или блок Bluetooth;

микросхема периферийной обработки представляет собой блок Аналого-Цифрового Преобразователя АЦП, блок Широтно-Импульсной Модуляции ШИМ, блок обработки видеосигналов или блок обработки звуковых сигналов.

[0015] В изобретении дополнительно предлагается устройство для пробуждения главного Блока Микроконтроллера MCU, причем данное устройство применяется в устройстве, содержащем главный MCU, микросхему периферийного интерфейса и микросхему периферийной обработки, и содержит:

модуль настройки, выполненный с возможностью настройки главного MCU на нахождение в состоянии глубокого сна и настройки микросхемы периферийного интерфейса и микросхемы периферийной обработки на нахождение в нормальном рабочем состоянии;

модуль контроля, выполненный с возможностью контроля объема данных, передаваемых микросхемой периферийной обработки в микросхему периферийного интерфейса; и

модуль передачи, выполненный с возможностью передачи сигнала пробуждения в главный MCU, если объем данных превышает порог.

[0016] В одном из вариантов осуществления модуль передачи выполнен с возможностью передачи сигнала пробуждения в виде сигнала прерывания в главный MCU.

[0017] В одном из вариантов осуществления модуль настройки содержит:

первый субмодуль соединения, выполненный с возможностью соединения линии синхронизации главного MCU с сигналом ведущего генератора синхроимпульсов;

второй субмодуль соединения, выполненный с возможностью соединения каждой из линии синхронизации микросхемы периферийной обработки и линии синхронизации микросхемы периферийного интерфейса с сигналом ведомого генератора синхроимпульсов; и

субмодуль управления, выполненный с возможностью управления сигналом ведущего генератора синхроимпульсов и сигналом ведомого генератора синхроимпульсов, чтобы настроить главный MCU на нахождение в состоянии глубокого сна и настроить микросхему периферийной обработки и микросхему периферийного интерфейса на нахождение в нормальном рабочем состоянии.

[0018] В одном из вариантов осуществления модуль настройки выполнен с возможностью настройки на передачу данных между друг другом посредством Прямого Доступа к Памяти DMA.

[0019] В одном из вариантов осуществления микросхема периферийного интерфейса представляет собой блок Универсального Асинхронного Приемопередатчика UART, блок Последовательного Периферийного Интерфейса SPI, блок шины для Соединения Микросхем I2C или блок Bluetooth;

микросхема периферийной обработки представляет собой блок Аналого-Цифрового Преобразователя АЦП, блок Широтно-Импульсной Модуляции ШИМ, блок обработки видеосигналов или блок обработки звуковых сигналов.

[0020] В изобретении дополнительно предлагается устройство для пробуждения главного Блока Микроконтроллера MCU, причем данное устройство содержит:

процессор; и

память, выполненную с возможностью хранения команд, исполнимых процессором;

причем процессор выполнен с возможностью:

настройки главного MCU на нахождение в состоянии глубокого сна и настройки микросхемы периферийного интерфейса и микросхемы периферийной обработки на нахождение в нормальном рабочем состоянии;

контроля объема данных, передаваемых микросхемой периферийной обработки в микросхему периферийного интерфейса; и

передачи сигнала пробуждения в главный MCU, если объем данных превышает порог.

[0021] Технические решения, предлагаемые в изобретении, могут включать в себя следующие полезные эффекты.

[0022] В вышеописанных вариантах осуществления линия синхронизации главного MCU соединена с сигналом ведущего генератора синхроимпульсов, а каждая из линии синхронизации микросхемы периферийной обработки и линии синхронизации микросхемы периферийного интерфейса соединена с сигналом ведомого генератора синхроимпульсов, т.е. линии синхронизации главного MCU, микросхемы периферийной обработки и микросхемы периферийного интерфейса соединены с различными сигналами синхроимпульсов таким образом, что микросхема периферийного интерфейса и микросхема периферийной обработки могут оставаться в нормальном рабочем состоянии, когда главный MCU переходит в состояние глубокого сна. Таким образом, если объем данных, передаваемых с микросхемы периферийной обработки в микросхему периферийного интерфейса, превышает порог, микросхема периферийного интерфейса может передавать сигнал пробуждения в главный MCU, а главный MCU может передавать, принимать и обрабатывать данные после своего пробуждения. Таким образом, главный MCU в состоянии глубокого сна может быть своевременно пробужден для передачи, приема и обработки данных.

[0023] Следует понимать, что приведенное выше общее описание и нижеследующее подробное описание являются иллюстративными и пояснительными и не должны трактоваться как ограничивающие изобретение.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

[0024] Чертежи, которые включены в данное описание и составляют его часть, иллюстрируют варианты осуществления, соответствующие изобретению, и вместе с описанием служат для объяснения принципов изобретения.

[0025] Фиг. 1 представляет собой схематическую диаграмму схемы для пробуждения главного MCU в соответствии с одним из примеров осуществления.

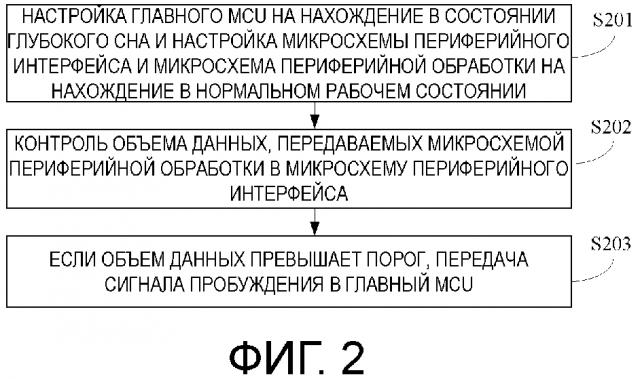

[0026] Фиг. 2 представляет собой структурную схему способа пробуждения главного MCU в соответствии с одним из примеров осуществления.

[0027] Фиг. 3 представляет собой структурную схему этапа S201 в способе пробуждения главного MCU в соответствии с одним из примеров осуществления.

[0028] Фиг. 4 представляет собой блок-схему устройства для пробуждения главного MCU в соответствии с одним из примеров осуществления.

[0029] Фиг. 5 представляет собой блок-схему модуля настройки в устройстве для пробуждения главного MCU в соответствии с одним из примеров осуществления.

[0030] Фиг. 6 представляет собой схематическую диаграмму устройства для пробуждения главного MCU в соответствии с одним из примеров осуществления.

ПОДРОБНОЕ ОПИСАНИЕ

[0031] Из приведенных ниже описаний и чертежей будут понятны указанные и прочие аспекты вариантов осуществления изобретения. В этих описаниях и чертежах представлены некоторые конкретные подходы вариантов осуществления изобретения, чтобы продемонстрировать некоторые пути осуществления принципа вариантов осуществления изобретения, однако следует понимать, что вариант осуществления о изобретения этим не ограничивается. Напротив, варианты осуществления изобретения включают в себя все варианты, модификации и их эквиваленты в пределах сущности и объема изобретения, определенных формулой изобретения.

[0032] Фиг. 1 представляет собой схематическую диаграмму схемы для пробуждения главного MCU в соответствии с одним из примеров осуществления. Схема содержит главный MCU 11, микросхему 12 периферийного интерфейса и микросхему 13 периферийной обработки.

[0033] Микросхема 13 периферийной обработки соединена с главным MCU 11 посредством микросхемы 12 периферийного интерфейса.

[0034] Линия синхронизации главного MCU 11 соединена с сигналом ведущего генератора синхроимпульсов, а каждая из линии синхронизации микросхемы 13 периферийной обработки и линии синхронизации микросхемы 12 периферийного интерфейса соединена с сигналом ведомого генератора синхроимпульсов таким образом, что микросхема 12 периферийного интерфейса и микросхема 13 периферийной обработки остаются в нормальном рабочем состоянии, когда главный MCU переходит в состояние глубокого сна. Микросхема 12 периферийного интерфейса выполнена с возможностью контроля объема данных, передаваемых микросхемой 13 периферийной обработки в микросхему 12 периферийного интерфейса, и передачи сигнала пробуждения в главный MCU 11, если объем данных превышает порог.

[0035] В вышеописанном варианте осуществления линия синхронизации главного MCU 11 соединена с сигналом ведущего генератора синхроимпульсов, а каждая из линии синхронизации микросхемы 13 периферийной обработки и линии синхронизации микросхемы 12 периферийного интерфейса соединена с сигналом ведомого генератора синхроимпульсов, т.е. линии синхронизации главного MCU 11, микросхемы 13 периферийной обработки и микросхемы 12 периферийного интерфейса соединены с различными сигналами синхроимпульсов таким образом, что микросхема 12 периферийного интерфейса и микросхема 13 периферийной обработки могут оставаться в нормальном рабочем состоянии, когда главный MCU 11 переходит в состояние глубокого сна. Таким образом, если объем данных, передаваемых с микросхемы 13 периферийной обработки в микросхему 12 периферийного интерфейса, превышает порог, микросхема 12 периферийного интерфейса может передавать сигнал пробуждения в главный MCU 11, а затем главный MCU может передавать, принимать и обрабатывать данные после своего пробуждения. Таким образом, главный MCU в состоянии глубокого сна может быть своевременно пробужден для передачи, приема и обработки данных.

[0036] В вышеописанном варианте осуществления в микросхеме периферийного интерфейса размещается буфер. Микросхема периферийной обработки готовит данные, передаваемые в главный MCU посредством микросхемы периферийного интерфейса, и передает данные в микросхему периферийного интерфейса, которая сохраняет данные в буфере и передает сигнал пробуждения в главный MCU, если объем данных превышает порог.

[0037] В одном из вариантов осуществления микросхема периферийного интерфейса передает сигнал пробуждения в виде сигнала прерывания в главный MCU таким образом, что главный MCU 11 может быть своевременно пробужден в состоянии глубокого сна для передачи и приема данных. В частности, микросхема периферийного интерфейса контролирует объем данных, передаваемых микросхемой периферийной обработки в микросхему периферийного интерфейса, генерирует сигнал прерывания, если объем данных превышает порог, и передает сигнал прерывания в главный MCU, тем самым пробуждая главный MCU.

[0038] В одном из вариантов осуществления микросхема периферийной обработки и микросхема периферийного интерфейса могут передавать данные между друг другом посредством Прямого Доступа к Памяти DMA, который представляет собой операцию высокоскоростной передачи данных, обеспечивающую прямое считывание и запись данных между внешним устройством и памятью без участия центрального процессора (CPU) и без вмешательства со стороны CPU и полностью управляемую контроллером DMA таким образом, что данные могут передаваться между микросхемой периферийной обработки и микросхемой периферийного интерфейса, даже если главный MCU находится в состоянии глубокого сна.

[0039] В одном из вариантов осуществления микросхема периферийного интерфейса может представлять собой блок Универсального Асинхронного Приемопередатчика UART, блок Последовательного Периферийного Интерфейса SPI, блок шины для Соединения Микросхем I2C или блок Bluetooth; микросхема периферийной обработки может представлять собой блок Аналого-Цифрового Преобразователя АЦП, блок Широтно-Импульсной Модуляции ШИМ, блок обработки видеосигналов или блок обработки звуковых сигналов.

[0040] Далее описывается пример применения изобретения, в котором микросхема периферийного интерфейса выполнена в виде блока UART, а микросхема периферийной обработки выполнена в виде блока АЦП.

[0041] Данный пример применения представляет собой схему с низким энергопотреблением, применяемую в интеллектуальном устройстве, главный MCU которого может быть своевременно разбужен из состояния глубокого сна для приема и передачи данных. Схема с низким энергопотреблением является внутренней периферийной структурой, независимой от ведущего генератора синхроимпульсов, в которой внутренний периферийный блок UART и блок АЦП имеют собственные генераторы синхроимпульсов, независимые от ведущего генератора синхроимпульсов. При этом, если главный MCU входит в режим глубокого сна, рабочее состояние определенного периферийного оборудования может настраиваться отдельно. Например, блок UART остается в нормальном рабочем состоянии, когда главный MCU входит в режим глубокого сна, и передает данные с помощью блока АЦП посредством DMA. Блок UART будет пробуждать главный MCU путем передачи сигнала прерывания, если объем данных, передаваемых блоком АЦП посредством блока UART, превышает порог, таким образом, что главный MCU может принимать, передавать и обрабатывать данные. Таким образом, он может, тем не менее, обеспечивать возможность нормальной передачи данных в режиме сверхмалого энергопотребления.

[0042] Фиг. 2 представляет собой структурную схему способа пробуждения главного MCU в соответствии с одним из примеров осуществления, и, как показано на фиг. 2, данный способ применяется в устройстве, содержащем главный MCU, микросхему периферийного интерфейса и микросхему периферийной обработки, и включает в себя нижеследующие этапы S201-S203.

[0043] На этапе S201 главный MCU настраивается на нахождение в состоянии глубокого сна, а микросхема периферийного интерфейса и микросхема периферийной обработки настроены на нахождение в нормальном рабочем состоянии.

[0044] На этапе S202 контролируется объем данных, передаваемых микросхемой периферийной обработки в микросхему периферийного интерфейса.

[0045] На этапе S203, если объем данных превышает порог, сигнал пробуждения передается в главный MCU. Сигнал пробуждения может передаваться в главный MCU в виде прерывания.

[0046] В вышеописанном варианте осуществления главный MCU настроен на нахождение в состоянии глубокого сна, микросхема периферийного интерфейса и микросхема периферийной обработки настроены на нахождение в нормальном рабочем состоянии, а сигнал пробуждения передается в главный MCU, если объем данных, передаваемых с микросхемы периферийной обработки в микросхему периферийного интерфейса, превышает порог. Таким образом, главный MCU может быть своевременно пробужден из состояния глубокого сна для приема и передачи данных.

[0047] В одном из вариантов осуществления микросхема периферийного интерфейса может представлять собой блок Универсального Асинхронного Приемопередатчика UART, блок Последовательного Периферийного Интерфейса SPI, блок шины для Соединения Микросхем I2C или блок Bluetooth; микросхема периферийной обработки может представлять собой блок Аналого-Цифрового Преобразователя АЦП, блок Широтно-Импульсной Модуляции ШИМ, блок обработки видеосигналов или блок обработки звуковых сигналов.

[0048] Этап S201 включает в себя настройку микросхемы периферийной обработки и микросхемы периферийного интерфейса на передачу данных между друг другом посредством Прямого Доступа к Памяти DMA, который представляет собой операцию высокоскоростной передачи данных, обеспечивающую прямое считывание и запись данных между внешним устройством и памятью без участия CPU и без вмешательства со стороны CPU и полностью управляемую контроллером DMA таким образом, что данные тем не менее могут передаваться между микросхемой периферийной обработки и микросхемой периферийного интерфейса, даже если главный MCU находится в состоянии глубокого сна.

[0049] Как показано на фиг. 3, этап S201 включает в себя следующие этапы.

[0050] На этапе S2011 линия синхронизации главного MCU соединяется с сигналом ведущего генератора синхроимпульсов.

[0051] На этапе S2012 каждая из линии синхронизации микросхемы периферийной обработки и линии синхронизации микросхемы периферийного интерфейса соединяется с сигналом ведомого генератора синхроимпульсов.

[0052] На этапе S2013 управление сигналом ведущего генератора синхроимпульсов и сигналом ведомого генератора синхроимпульсов осуществляется таким образом, чтобы настроить главный MCU на нахождение в состоянии глубокого сна и настроить микросхему периферийной обработки и микросхему периферийного интерфейса на нахождение в нормальном рабочем состоянии.

[0053] В вышеописанном варианте осуществления линия синхронизации главного MCU соединена с сигналом ведущего генератора синхроимпульсов, а каждая из линии синхронизации микросхемы периферийной обработки и линии синхронизации микросхемы периферийного интерфейса соединена с сигналом ведомого генератора синхроимпульсов, т.е. линии синхронизации главного MCU, микросхемы периферийной обработки и микросхемы периферийного интерфейса соединены с различными сигналами синхроимпульсов таким образом, что микросхема периферийного интерфейса и микросхема периферийной обработки могут оставаться в нормальном рабочем состоянии, когда главный MCU переходит в состояние глубокого сна.

[0054] Фиг. 4 представляет собой блок-схему устройства для пробуждения главного MCU в соответствии с одним из примеров осуществления, и, как показано на фиг. 4, данное устройство применяется в устройстве, содержащем главный MCU, микросхему периферийного интерфейса и микросхему периферийной обработки, и включает в себя модуль 41 настройки, модуль 42 контроля и модуль 43 передачи.

[0055] Модуль 41 настройки выполнен с возможностью настройки главного MCU на нахождение в состоянии глубокого сна и настройки микросхемы периферийного интерфейса и микросхемы периферийной обработки на нахождение в нормальном рабочем состоянии.

[0056] Модуль 42 контроля выполнен с возможностью контроля объема данных, передаваемых микросхемой периферийной обработки в микросхему периферийного интерфейса.

[0057] Модуль 43 передачи выполнен с возможностью передачи сигнала пробуждения в главный MCU, если объем данных превышает порог.

[0058] В вышеописанном варианте осуществления главный MCU настроен на нахождение в состоянии глубокого сна, микросхема периферийного интерфейса и микросхема периферийной обработки настроены на нахождение в нормальном рабочем состоянии, а сигнал пробуждения передается в главный MCU, если объем данных, передаваемых с микросхемы периферийной обработки в микросхему периферийного интерфейса, превышает порог. Таким образом, главный MCU может быть своевременно пробужден из состояния глубокого сна для приема и передачи данных.

[0059] В одном из вариантов осуществления модуль 41 настройки выполнен с возможностью настройки микросхемы периферийной обработки и микросхемы периферийного интерфейса на передачу данных между друг другом посредством Прямого Доступа к Памяти DMA, который представляет собой операцию высокоскоростной передачи данных, обеспечивающую прямое считывание и запись данных между внешним устройством и памятью без участия CPU и без вмешательства со стороны CPU и полностью управляемую контроллером DMA таким образом, что данные могут передаваться между микросхемой периферийной обработки и микросхемой периферийного интерфейса, когда главный MCU находится в состоянии глубокого сна.

[0060] Как показано на фиг. 5, модуль 41 настройки содержит первый субмодуль 411 соединения, второй субмодуль 412 соединения и субмодуль 413 управления.

[0061] Первый субмодуль 411 соединения выполнен с возможностью соединения линии синхронизации главного MCU с сигналом ведущего генератора синхроимпульсов.

[0062] Второй субмодуль 412 соединения выполнен с возможностью соединения каждой из линии синхронизации микросхемы периферийной обработки и линии синхронизации микросхемы периферийного интерфейса с сигналом ведомого генератора синхроимпульсов.

[0063] Субмодуль 413 управления выполнен с возможностью управления сигналом ведущего генератора синхроимпульсов и сигналом ведомого генератора синхроимпульсов, чтобы настроить главный MCU на нахождение в состоянии глубокого сна и настроить микросхему периферийной обработки и микросхему периферийного интерфейса на нахождение в нормальном рабочем состоянии.

[0064] В вышеописанном варианте осуществления линия синхронизации главного MCU соединена с сигналом ведущего генератора синхроимпульсов, а каждая из линии синхронизации микросхемы периферийной обработки и линии синхронизации микросхемы периферийного интерфейса соединена с сигналом ведомого генератора синхроимпульсов, т.е. линии синхронизации главного MCU, микросхемы периферийной обработки и микросхемы периферийного интерфейса соединены с различными сигналами синхроимпульсов таким образом, что микросхема периферийного интерфейса и микросхема периферийной обработки могут оставаться в нормальном рабочем состоянии, когда главный MCU переходит в состояние глубокого сна.

[0065] Микросхема периферийного интерфейса может представлять собой блок Универсального Асинхронного Приемопередатчика UART, блок Последовательного Периферийного Интерфейса SPI, блок шины для Соединения Микросхем I2C или блок Bluetooth.

[0066] Микросхема периферийной обработки может представлять собой блок Аналого-Цифрового преобразователя АЦП, блок Широтно-Импульсной Модуляции ШИМ, блок обработки видеосигналов или блок обработки звуковых сигналов.

[0067] Что касается устройств в вышеописанных вариантах осуществления, конкретные режимы работы находящихся в них отдельных модулей подробно описаны в вариантах осуществления, относящихся к способам пробуждения главного MCU, которые не излагаются в настоящем документе.

[0068] Фиг. 6 представляет собой схематическую диаграмму устройства 1200 для пробуждения главного MCU в соответствии с одним из примеров осуществления. Данное устройство применимо к мобильному терминалу. Например, устройство 1200 может представлять собой мобильный телефон, компьютер, цифровой вещательный терминал, устройство для обмена сообщениями, игровую приставку, планшетное устройство, тренажер, Персональный Цифровой Помощник PDA и т.д.

[0069] В соответствии с фиг. 6 устройство 1200 может содержать следующие один или более компоненты: компонент 1202 обработки, память 1204, компонент 1206 электропитания, мультимедийный компонент 1208, звуковой компонент 1210, интерфейс 1212 ввода/вывода (I/O), компонент 1214 датчиков и компонент 1216 связи.

[0070] Компонент 1202 обработки, как правило, управляет всеми операциями устройства 1200, такими как операции, связанные с отображением, телефонными вызовами, передачами данных, операции камеры и операции записи. Компонент 1202 обработки может содержать один или более процессоров 1220 для исполнения команд для выполнения всех или части этапов вышеописанных способов. Кроме того, компонент 1202 обработки может содержать один или более модулей, которые упрощают взаимодействие между компонентом 1202 обработки и другими компонентами. Например, компонент 1202 обработки может содержать мультимедийный модуль для упрощения взаимодействия между мультимедийным компонентом 1208 и компонентом 1202 обработки.

[0071] Память 1204 выполнена с возможностью хранения различных типов данных для обеспечения функционирования устройства 1200. Примеры таких данных включают в себя команды для любых приложений или способов, применяемых в устройстве 1200, контактную информацию, информацию телефонной книги, сообщения, изображения, видеоинформацию и т.д. Память 1204 может быть реализована с помощью любого типа энергозависимых или энергонезависимых запоминающих устройств или их комбинации, таких как статическое оперативное запоминающее устройство (SRAM), электрически стираемое программируемое постоянное запоминающее устройство (EEPROM), стираемое программируемое постоянное запоминающее устройство (EPROM), программируемое постоянное запоминающее устройство (PROM), постоянное запоминающее устройство (ROM), магнитная память, флэш-память, магнитный или оптический диск.

[0072] Компонент 1206 электропитания подает электропитание в различные компоненты устройства 1200. Компонент 1206 электропитания может содержать систему управления электропитанием, один или более источников электропитания и любые иные компоненты, связанные с генерированием, управлением и распределением электропитания в устройстве 1200.

[0073] Мультимедийный компонент 1208 содержит экран, обеспечивающий выходной интерфейс между устройством 1200 и пользователем. В некоторых вариантах осуществления экран может содержать жидкокристаллический дисплей (LCD) и сенсорную панель (ТР). Если экран содержит сенсорную панель, экран может быть реализован в виде сенсорного экрана для приема входных сигналов от пользователя. Сенсорная панель содержит один или более датчиков касания для восприятия касаний, скольжений и иных жестов на сенсорной панели. Датчики касания могут не только воспринимать границу действия касания или скольжения, но и воспринимать период времени и давление, связанные с действием касания или скольжения. В некоторых вариантах осуществления мультимедийный компонент 1208 содержит фронтальную камеру и/или заднюю камеру. Фронтальная камера и задняя камера могут принимать внешние мультимедийные данные, когда устройство 1200 находится в рабочем режиме, таком как режим фотографирования или видеорежим. Каждая из фронтальной камеры и задней камеры может представлять собой фиксированную оптическую линзовую систему или иметь возможности фокусирования и оптического увеличения.

[0074] Звуковой компонент 1210 выполнен с возможностью вывода и/или ввода звуковых сигналов. Например, звуковой компонент 1210 содержит микрофон (MIC), выполненный с возможностью приема внешнего звукового сигнала, когда интеллектуальное устройство 1200 находится в рабочем режиме, таком как режим вызова, режим записи и режим распознавания речи. Принимаемый звуковой сигнал может дополнительно сохраняться в памяти 1204 или передаваться посредством компонента 1216 связи. В некоторых вариантах осуществления звуковой компонент 1210 дополнительно содержит громкоговоритель для вывода звуковых сигналов.

[0075] Интерфейс 1212 I/O обеспечивает интерфейс для компонента 1202 обработки и модулей периферийного интерфейса, таких как клавиатура, колесо прокрутки, кнопки и так далее. Кнопки могут включать в себя в качестве неограничивающих примеров кнопку возврата в исходное положение, кнопку громкости, кнопку пуска и кнопку блокировки.

[0076] Компонент 1214 датчиков содержит один или более датчиков для обеспечения оценок состояния различных аспектов устройства 1200. Например, компонент 1214 датчиков может обнаруживать открытое/закрытое состояние устройства 1200 и относительное позиционирование компонентов (например, дисплея и кнопочной панели устройства 1200). Компонент 1214 датчиков может также обнаруживать изменение в положении устройства 1200 или компонента в устройстве 1200, наличие или отсутствие контакта пользователя с устройством 1200, ориентацию или ускорение/замедление устройства 1200 и изменение температуры устройства 1200. Компонент 1214 датчиков может содержать датчик приближения, выполненный с возможностью обнаружения присутствия близлежащих объектов без какого-либо физического соприкосновения. Компонент 1214 датчиков может также содержать датчик освещенности, такой как датчик изображений на основе прибора с зарядовой связью (CCD) или комплементарной структуры «металл-оксид-полупроводник» (CMOS) для использования в сферах применения формирования изображений. В некоторых вариантах осуществления компонент 1214 датчиков может также содержать датчик ускорений, гиродатчик, магнитный датчик, датчик давления или датчик температуры.

[0077] Компонент 1216 связи выполнен с возможностью упрощения проводной или беспроводной связи между устройством 1200 и другими устройствами. Устройство 1200 может осуществлять доступ к беспроводной сети на основе стандарта в области связи, такого как WIFI, 2G или 3G, либо их комбинации. В одном примере осуществления компонент 1216 связи принимает сигнал вещания или связанную с вещанием информацию от внешней системы управления вещанием посредством канала вещания. В одном примере осуществления компонент 1216 связи дополнительно содержит модуль связи ближнего поля (NFC) для упрощения связи малого радиуса действия. Например, модуль NFC может быть реализован на основе технологии радиочастотной идентификации (RFID), технологии Ассоциации передачи данных в инфракрасном диапазоне (IrDA), сверхширокополосной (UWB) технологии, технологии Bluetooth (BT) и прочих технологий.

[0078] В примерах осуществления устройство 1200 может быть реализовано с использованием одной или более специализированных интегральных микросхем (ASIC), цифровых сигнальных процессоров (DSP), устройств цифровой обработки сигналов (DSPD), программируемых логических устройств (PLD), программируемых пользователем вентильных матриц (FPGA), контроллеров, микроконтроллеров, микропроцессоров или иных электронных компонентов для осуществления вышеописанных способов.

[0079] В примерах осуществления предлагается также энергонезависимый машиночитаемый носитель информации, содержащий команды, такой как память 1204, содержащая команды. Вышеуказанные команды исполнимы процессором 1220 в устройстве 1200 для осуществления вышеописанных способов. Например, энергонезависимый машиночитаемый носитель информации может представлять собой ROM, оперативное запоминающее устройство (RAM), постоянное запоминающее устройство на компакт-дисках (CD-ROM), магнитную ленту, гибкий диск, оптическое устройство накопления данных и так далее.

[0080] Устройство для пробуждения главного Блока Микроконтроллера MCU, содержащее:

процессор; и

память, выполненную с возможностью хранения команд, исполнимых процессором;

причем процессор выполнен с возможностью:

настройки главного MCU на нахождение в состоянии глубокого сна и настройки микросхемы периферийного интерфейса и микросхемы периферийной обработки на нахождение в нормальном рабочем состоянии;

контроля объема данных, передаваемых микросхем