Вычислительный модуль

Иллюстрации

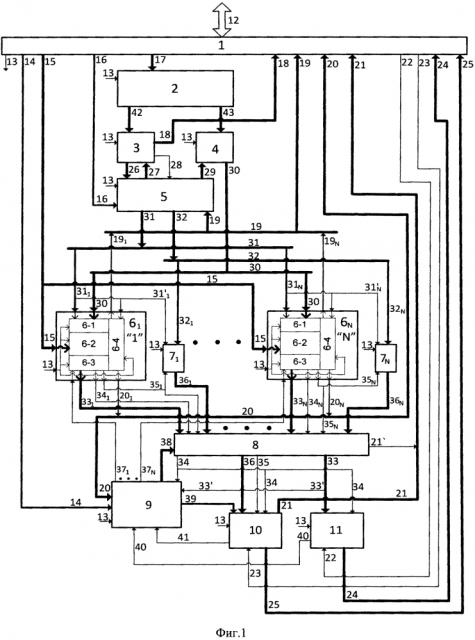

Показать всеИзобретение относится к области вычислительной техники, в частности к высокопроизводительным вычислительным устройствам для решения трудоемких задач с использованием распараллеливания по данным на множество независимых подзадач. Технический результат заключается в повышении производительности вычислительного модуля. Технический результат достигается за счет устройства, которое содержит интерфейсный блок, блок разделения заданий, блок памяти заголовков заданий, блок памяти данных заданий, арбитр заданий, вычислительное поле из группы из N вычислительных ядер 61, …, 6N, группу из N блоков памяти номеров заданий вычислительных ядер 71, …, 7N, блок мультиплексоров результатов, арбитр результатов, блок памяти заголовков результатов, блок памяти данных результатов, внешний интерфейс, при этом каждое вычислительное ядро 61, …, 6N состоит из входной буферной памяти 6-1, операционного блока 6-2, выходной буферной памяти 6-3 и блока управления 6-4. 1 ил.

Реферат

ОБЛАСТЬ ТЕХНИКИ

Изобретение относится к области вычислительной техники, в частности к высокопроизводительным вычислительным устройствам для решения трудоемких задач с использованием распараллеливания по данным на множество независимых подзадач.

ПРЕДШЕСТВУЮЩИЙ УРОВЕНЬ ТЕХНИКИ

Известна адаптивная система обработки данных (RU №105487 U1, МПК G06F 15/16, заявл. 25.02.2011, опубл. 10.06.2011, БИ №16), содержащая N линеек обработки, состоящих из Mn модулей обработки, Mn блоков выбора каналов и выходной магистрали передачи сигналов, блок памяти заявок, регистр задания режимов работы модулей обработки, мультиплексор/демультиплексор выходных магистралей, N дешифраторов адреса, приоритетный шифратор.

Недостатком известной системы является большой объем аппаратных средств и сложная структура распараллеливания потока заявок системы.

Известен базовый модуль многопроцессорной вычислительной системы (RU №86332 U1, МПК G06F 15/16, заявл. 21.05.2009, опубл. 27.08.2009, БИ №24), содержащий вычислительное поле, состоящее из 16 вычислительных элементов, расположенных в узлах двумерной решетки 4×4 и соединенных между собой ортогональной системой связей по близкодействию, контроллер обращений, предназначенный для передачи информации между базовым модулем и управляющей ЭВМ, и блоки распределенной памяти.

Недостатками данного модуля являются сложные матрично-конвейерная структура и многоразрядные информационные связи между вычислительными элементами.

Наиболее близким устройством того же назначения к заявленному изобретению по совокупности признаков является принятый за прототип вычислительный модуль (RU №139326 U1, МПК G06F 15/16, заявл. 10.12.2013, опубл. 10.04.2014, БИ №10), содержащий вычислительное поле из L вычислительных элементов, соответствующих количеству каналов распараллеливания, и каждый вычислительный элемент содержит S ступеней конвейера, блок памяти FIFO, блок генератора переменной X, входной и выходной буферы, группу из L схем сравнения, элемент ИЛИ, четыре внешних входа и четыре внешних выхода.

Недостатками данного вычислительного модуля являются возможность его использования для обработки данных всеми вычислительными элементами только по одному алгоритму, синхронная работа всех вычислительных элементов при обработке единого для всех задания и формирование единого для всех вычислительных элементов множества результатов.

Причиной, препятствующей достижению технического результата, является отсутствие средств для индивидуального обмена с вычислительными элементами при загрузке пакетов входных данных и считывании пакетов результатов.

Задача, на решение которой направлено предлагаемое изобретение, заключается в создании вычислительного модуля, имеющего единую параметризуемую вычислительную среду для подключения вычислительных ядер, за счет чего упрощается сложность разработки вычислительных систем и повышается производительность за счет сокращения времени обмена и сокращения времени ожидания обслуживания.

Техническим результатом предлагаемого изобретения является уменьшение трудоемкости и сроков разработки и повышение производительности.

КРАТКОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Указанный технический результат при осуществлении изобретения достигается тем, что вычислительный модуль содержит группу из N вычислительных ядер 61, …, 6N, интерфейсный блок 1, блок разделения заданий 2, блок памяти заголовков заданий 3, блок памяти данных заданий 4, арбитр заданий 5, группу из N блоков памяти номеров заданий вычислительных ядер 71,…, 7N, блок мультиплексоров результатов 8, арбитр результатов 9, блок памяти заголовков результатов 10, блок памяти данных результатов 11, внешний интерфейс 12, при этом каждое вычислительное ядро 61, …, 6N состоит из входной буферной памяти 6-1, операционного блока 6-2, выходной буферной памяти 6-3 и блока управления 6-4,

причем внешний интерфейс 12 соединен с интерфейсным блоком 1, выход сброса 13 которого соединен с соответствующими входами сброса блока разделения заданий 2, блока памяти заголовков заданий 3, блока памяти данных заданий 4, арбитра заданий 5, блоков вычислительных ядер 61, …, 6N, блоков памяти номеров заданий 71, …, 7N, арбитра результатов 9, блока памяти заголовков результатов 10 и блока памяти данных результатов 11, также интерфейсным блоком 1 шиной кода режима чтения результатов 14 соединен с арбитром результатов 9, шиной общих параметров 15 соединен с операционными блоками 6-2 всех вычислительных ядер 61, …, 6N, шиной кода режима записи заданий 16 соединен с арбитром заданий 5, шиной потоковой записи заданий 17 соединен с блоком разделения заданий 2, шиной кода количества заданий 18 подключен к выходу блока памяти заголовков заданий 3, шиной запросов на запись заданий 19 и шиной запросов на чтение результатов 20 подключен к выходам всех вычислительных ядер 61, …, 6N, шиной кода состояния 21 подключен к выходу блока памяти заголовков результатов 10 и выходу общего признака «Пустой» 21' блока мультиплексоров результатов 8, шиной потокового чтения данных результатов 24 подключен к выходу блока памяти данных результатов 11, шиной потокового чтения заголовков результатов 25 подключен к выходу блока памяти заголовков результатов 10, а выход сигнала чтения данных результатов 22 соединен с соответствующим входом блока памяти данных результатов 11 и выход сигнала чтения заголовков результатов 23 соединен с соответствующим входом блока памяти заголовков результатов 10,

блок разделения заданий 2 шиной записываемых заголовков заданий 42 соединен с соответствующим входом блока памяти заголовков заданий 3 и шиной записываемых данных заданий 43 соединен с соответствующим входом блока памяти данных заданий 4,

блок памяти заголовков заданий 3 шиной считанных заголовков заданий 26 и выходом признака «Пустой» памяти заданий соединен с соответствующими входами арбитра заданий 5, выход которого шиной управления чтением заголовков заданий 27 подключен к соответствующему входу блока памяти заголовков заданий 3,

арбитр заданий 5 шиной управления записью заданий 31 соединен с входными буферными памятями 6-1 соответствующих вычислительных ядер 61, …, 6N по шинам 311, 31N записи заданий и соединен с блоками памяти номеров заданий 71, …, 7N по шинам 31'1, …, 31'N, кроме того, арбитр заданий 5 шиной записываемых номеров заданий 32 соединен по шинам 321, …, 32N с соответствующими входами блоков памяти номеров заданий 71, …, 7N, соответствующий вход арбитра заданий 5 соединен с шиной запросов на запись заданий 19, включающей выходы запросов на запись заданий от вычислительных ядер 191, …, 19N, а также арбитр заданий 5 шиной управления чтением данных заданий 29 соединен с соответствующим входом блоком памяти данных заданий 4, выход которого по шине считанных данных заданий 30 соединен с соответствующими входами входных буферных памятей 6-1 соответствующих вычислительных ядер 61, …, 6N,

соответствующие выходы блоков управления 6-3 вычислительных ядер 61, …, 6N шинами результатов 331, …, 33N подключены к соответствующим входам блока мультиплексоров результатов 8, соответствующий выход которого по шине результатов выбранного вычислительного ядра 33 соединен с соответствующим входом блока памяти данных результатов 11, кроме того, соответствующие выходы окончания считывания пакетов результатов 341, …, 34N блоков управления 6-3 вычислительных ядер 61, …, 6N подключены к соответствующим входам блока мультиплексоров результатов 8, соответствующий выход окончания считывания пакета результатов 34 которого подключен к соответствующим входам арбитра результатов 9, блока памяти заголовков результатов 10 и блока памяти данных результатов 11, соответствующие выходы окончания заданий 351, …, 35N блоков управления 6-3 вычислительных ядер 61, …, 6N подключены к соответствующим входам блоков памяти номеров заданий 71, …, 7N и подключены к соответствующим входам блока мультиплексоров результатов 8, соответствующий выход окончания задания 35 которого подключен к соответствующим входам блока памяти заголовков результатов 10,

соответствующие выходы блоков памяти номеров заданий 71, …, 7N шинами считываемых номеров заданий 361, …, 36N подключены к соответствующим входам блока мультиплексоров результатов 8, соответствующий выход которого по шине считываемого номера задания 36 соединен с соответствующим входом блока памяти заголовков результатов 10,

соответствующие выходы арбитра результатов 9 выходами сигналов чтения результатов 371, …, 37N соединены с соответствующими входами блоков выходной буферной памяти 6-3 соответствующих вычислительных ядер 61, …, 6N, а также соответствующие выходы арбитра результатов 9 по шине 38 кода номера выбранного вычислительного ядра подключены к входам управления блока мультиплексоров результатов 8, а по шине количества слов в пакете результатов 39 подключены к соответствующим входам блока памяти заголовков результатов 10, выход признака переполнения 41 которого соединен с соответствующим входом арбитра результатов 9, соответствующий вход которого соединен с выходом 40 признака переполнения памяти результатов 11.

КРАТКОЕ ОПИСАНИЕ ЧЕРТЕЖЕЙ

На фиг. 1 приведена функциональная схема вычислительного модуля.

На фиг. 1 приняты следующие обозначения:

1 - интерфейсный блок,

2 - блок разделения заданий,

3 - блок памяти заголовков заданий,

4 - блок памяти данных заданий,

5 - арбитр заданий,

61, …, 6N - группа из N вычислительных ядер (ВЯ),

6-1 - входная буферная память ВЯ,

6-2 - операционный блок ВЯ,

6-3 - выходная буферная память ВЯ,

6-4 - блок управления ВЯ,

71, …, 7N - группа из N блоков памяти номеров заданий ВЯ,

8 - блок мультиплексоров результатов,

9 - арбитр результатов,

10 - блок памяти заголовков результатов,

11 - блок памяти данных результатов,

12 - внешний интерфейс,

13 - выход сброса,

14 - шина кода режима чтения результатов,

15 - шина общих параметров, передаваемых параллельным кодом,

16 - шина кода режима записи заданий,

17 - шина потоковой записи заданий,

18 - шина кода количества заданий во входной памяти,

19 - шина запросов на запись заданий,

191, …, 19N - запросы на запись заданий от ВЯ,

20 - шина запросов на чтение результатов,

201, …, 20N - запросы на чтение результатов от ВЯ,

21 - шина кода состояния памятей результатов,

21' - выход общего признака «Пустой» всех блоков памяти номеров заданий 71, …, 7N,

22 - выход сигнала чтения данных результатов,

23 - выход сигнала чтения заголовков результатов,

24 - шина потокового чтения данных результатов,

25 - шина потокового чтения заголовков результатов,

26 - шина считанных заголовков заданий,

27 - шина управления чтением заголовков заданий,

28 - выход признака «Пустой» памяти заданий,

29 - шина управления чтением данных заданий,

30 - шина считанных данных заданий,

31 - шина управления записью заданий,

311, …, 31N - шины управления записью заданий в ВЯ,

31'1, …, 31'N - выходы окончания записи задания в ВЯ,

32 - шина записываемых номеров заданий,

321, …, 32N - шины записываемых номеров заданий ВЯ,

331, …, 33N - шины результатов от ВЯ,

33 - шина результатов выбранного ВЯ,

33' - выход признака достоверности результата,

341, …, 34N - выходы окончания считывания пакетов результатов от ВЯ,

34 - выход окончания считывания пакета результатов выбранного ВЯ,

351, …, 35N - выходы окончания заданий от ВЯ,

35 - выход окончания задания выбранного ВЯ,

361, …, 36N - шины считываемых номеров заданий от ВЯ,

36 - шина считываемого номера задания выбранного ВЯ,

371, …, 37N - выходы сигналов чтения результатов ВЯ,

38 - шина кода номера выбранного схемой арбитража ВЯ,

39 - шина количества слов в пакете результатов,

40 - выход признака переполнения памяти результатов,

41 - выход признака переполнения памяти заголовков результатов,

42 - шина записываемых заголовков заданий,

43 - шина записываемых данных заданий.

ПОДРОБНОЕ ОПИСАНИЕ СУЩНОСТИ ИЗОБРЕТЕНИЯ

Предлагаемый вычислительный модуль (ВМ) предназначен для объединения множества из N вычислительных ядер 61, …, 6N. На данных ВЯ реализуются независимые подзадачи, для решения которых предназначен предлагаемый вычислительный модуль. Загрузка заданий для ВЯ и считывание результатов их работы осуществляются управляющим процессором (УП).

Предлагаемый вычислительный модуль обеспечивает унифицированный параметризуемый интерфейс для встраивания вычислительных ядер, что сводит подготовку модуля только к разработке вычислительных ядер 61, …, 6N.

Предлагаемый вычислительный модуль поддерживает автоматическую загрузку заданий в ВЯ из входной буферной памяти заданий и автоматическое считывание результатов из ВЯ в выходную буферную память результатов. При автоматической загрузке заданий и автоматическом считывании результатов, управляющий процессор не управляет каждым ВЯ, а только загружает пакеты заданий во входную буферную память и считывает пакеты результатов из выходной буферной памяти вычислительного модуля.

Интерфейсный блок 1 преобразует сигналы интерфейса 12 от управляющего процессора в сигналы внутренних интерфейсов модуля. Шины внутреннего интерфейса модуля состоят из 4 групп шин: шин кодов команд и постоянных параметров 13, 14, 15, 16, шины потоковой записи заданий 17, шин сигналов состояний модуля 18, 19, 20, 21 и шин потокового чтения результатов с сигналами управления 22, 23, 24, 25.

Коды команд и постоянных параметров состоят из сигнала сброса (начальной инициализации) модуля 13, кода режима чтения результатов 14, кода общих (одинаковых) параметров 15, передаваемых параллельным кодом для всех ВЯ 61, …, 6N, и кода режима записи заданий 16. Эти коды загружаются от УП в соответствующие регистры интерфейсного блока 1. Для изменения команды требуется повторная запись в тот же регистр или повторные записи в ту же группу регистров.

Интерфейсный блок 1 преобразует поступающие от УП по внешнему интерфейсу 12 команды потоковой записи и пакеты заданий в потоки данных, передаваемые по шине 17. Шина потоковой записи заданий 17 состоит из непосредственно шины записываемых данных и сигнала записи. Каждый из пакетов заданий состоит из заголовка пакета и следующих за ними данных.

Коды состояний модуля включают код количества пакетов заданий во входной памяти 18, код числа пакетов результатов в выходной памяти и признак «Пустой» памяти номеров заданий 21, запросы на запись заданий 19 и чтение результатов 20 от ВЯ 61, …, 6N. Интерфейсный блок 1 обеспечивает считывание данных кодов состояния модуля командами одиночного чтения внешнего интерфейса от УП.

Сигнал чтения данных результатов 22, шина потокового чтения данных результатов 24, сигнал чтения заголовков результатов 23 и шина чтения заголовков результатов 25 обеспечивают чтение результатов на внешний интерфейс 12 к УП. Интерфейсный блок 1 обеспечивает преобразование команд потокового чтения внешнего интерфейса 12 в сигналы чтения 22 и 23 и прием результатов с шин чтения 24 и 25.

Блок разделения заданий 2 предназначен для разделения пакетов на заголовки и данные 2. После сигнала сброса 13 блок разделения заданий 2 принимает первое слово по шине потоковой записи 17 как заголовок пакета задания, выделяет из данного слова код количества следующих за ним данных пакета задания, запоминает этот код, записывает заголовок задания по шине записываемых заголовков заданий 42 в память заголовков заданий 3. При поступлении следующих слов по шине потоковой записи 17 блок разделения заданий 2 форматирует их в зависимости от задаваемой параметром ширины шины данных заданий, записывает переформатированные слова по шине записываемых данных заданий 43 в память данных заданий 4 и проводит счет числа записанных данных в данном пакете заданий. При достижении количеством записанных слов данных значения, заданного в заголовке пакета задания, счетчик записанных слов пакета задания сбрасывается, а следующее слово из потока записи по шине потоковой записи заданий 17 принимается как заголовок нового пакета задания. Если разрядность шины данных ВЯ 30 больше разрядности шины потоковой записи 17, то блок 2 преобразует формат данных, поступающих по шине 17, объединяя по несколько входных слов шины 17 в одно записываемое слово на шине 43.

Блоки входной памяти заголовков заданий 3 и данных заданий 4 являются двухпортовыми ОЗУ, по одному порту которых осуществляется только запись, а по другому порту - только чтение. Запись в данные блоки памяти осуществляется только последовательно, с дисциплиной записи FIFO, а чтение осуществляется последовательно или с произвольным доступом для повторного считывания пакетов задания в режиме последовательной загрузки одного задания в ВЯ 61, …, 6N.

В блок памяти заголовков заданий 3 записываются заголовки заданий по шине 42, которые затем по сигналам по шине управления 27 передаются по шине считанных заголовков 26 на арбитр заданий 5. Блок 3 также формирует и выдает для чтения на интерфейсный блок 1 код количества заданий по шине 18, а также признак «Пустой» памяти заданий по выходу 28 на арбитр заданий 5. Блок памяти заголовков заданий 3 по сигналу сброса 13 обнуляет внутренний счетчик адреса записи в память и счетчик числа пакетов заданий в памяти. В режиме многократного чтения одного и того же задания для работы счетчика числа пакетов во входной памяти 3 по шине 17 передается также сигнал последнего чтения заголовка пакета.

Блок памяти данных заданий 4 записывает данные пакетов заданий по шине 43, по адресу, передаваемому арбитром заданий 5 по шине управления 29, а считываются данные пакетов заданий на ВЯ 61, …, 6N по шине считанных данных заданий 30. Блок памяти данных заданий 4 по сигналу сброса 13 обнуляет счетчик адреса записи в память. Блок памяти 4, при разрядности шины данных ВЯ 30 меньше разрядности шины потоковой записи 17, при чтении преобразует формат считываемых данных к формату шины 30, путем мультиплексирования.

Арбитр заданий 5 считывает пакеты заданий из блоков входной памяти заголовков заданий 3 и данных заданий 4 и записывает данные заданий в вычислительные ядра 61, …, 6N, а соответствующие им номера для идентификации того, к какому заданию относится результат, в N блоков памяти номеров заданий 71, …, 7N. При этом арбитр заданий 5 принимает с интерфейсного блока 1 по шине 16 код режима записи заданий, а по шине 19 запросы на запись заданий от вычислительных ядер. По шине 31 с арбитра заданий 5 на ВЯ 61, …, 6N поступают сигналы управления записью заданий 31'1, …, 31'N, а по шине 32 с арбитра заданий 5 поступают на блоки памяти номеров заданий 71, …, 7N записываемые номера заданий, которые записываются по сигналам 31'1, …, 31'N. По сигналу сброса 13 арбитр заданий 5 обнуляет счетчики адресов блоков памяти 3 и 4 и переходит в режим ожидания снятия признака «Пустой» на выходе 28.

Задание в общем случае может состоять из нескольких пакетов. В заголовке первого пакета задания содержится код режима записи задания и номер задания. В заголовке последнего пакета задания содержится признак последнего пакета, по которому формируется сигнал окончания загрузки задания. Сигналы окончания загрузки заданий по выходам 31'1, …, 31'N сообщают соответствующему ВЯ 61, …, 6N, что во входной памяти 6-1 загружено очередное задание для выполнения, и инициализируют запись номера этого задания в соответствующий блок памяти номера задания 71, …, 7N. Если в задании содержатся только параметры, а не данные для расчета, то в заголовке последнего пакета задания не содержится признака, инициализирующего выдачу сигнала окончания загрузки задания. В заголовках всех пакетов заданий содержится код управления записью задания (в какую часть входной памяти ВЯ должны быть направлены данные) и количество слов данных в пакете.

Режим записи задания определяется кодом режима записи задания в заголовке пакета задания и кодом режима записи заданий, поступающим с интерфейсного блока 1 по шине 16. Предлагаемым модулем поддерживаются следующие режимы записи заданий в ВЯ 61, …, 6N:

- Запись задания в соответствующее ВЯ 61, …, 6N, номер которого передается от интерфейсного блока 1 по шине 16, без ожидания наличия запроса на запись задания от этого ядра. Режим предназначен только для записи параметров в ВЯ.

- Запись задания в соответствующее ВЯ 61, …, 6N, номер которого передается от интерфейсного блока 1 по шине 16, после считывания по шине 19 на УП наличия запроса на запись задания от этого ядра.

- Запись задания в соответствующее ВЯ 61, …, 6N, номер которого указан в заголовке первого пакета задания, без ожидания наличия запроса на запись задания от этого ядра. Режим предназначен только для записи параметров в ВЯ.

- Запись задания в соответствующее ВЯ 61, …, 6N, номер которого указан в заголовке первого пакета задания, с ожиданием наличия запроса на запись задания от этого ядра по шине 19. Анализ запросов на запись заданий выполняется автоматически арбитром заданий 5.

- Запись задания параллельно во все ВЯ 61, …, 6N, без ожидания наличия запросов на запись заданий от всех ядер. Режим предназначен только для записи общих параметров в ВЯ 61, …, 6N.

- Запись задания параллельно во все ВЯ 61, …, 6N, с ожиданием наличия запросов на запись задания от всех ВЯ. При этом анализ запросов на запись заданий выполняется автоматически арбитром заданий 5.

- Запись задания последовательно во все ВЯ 61, …, 6N, с ожиданием наличия запросов на запись задания от каждого ядра перед записью в него задания. Анализ запросов на запись заданий выполняется автоматически арбитром заданий 5. Данный режим может быть предпочтительнее режима параллельной записи задания, если ВЯ 61, …, 6N не могут совмещать запись задания и обработку предыдущего задания, так как не требует готовности к записи задания всех ядер одновременно, и пока в одно ядро будет записываться задание, остальные могут выполнять обработку заданий.

- Запись задания в соответствующее ВЯ 61, …, 6N, выбранное арбитром заданий 5. Арбитр заданий 5 осуществляет автоматический выбор соответствующего ВЯ 61, …, 6N для записи задания в соответствии с приоритетом запросов на запись от ВЯ 61, …, 6N. При этом от каждого ВЯ 61, …, 6N поступает и анализируется 2-разрядный код запроса на запись по шинам 191, …, 19N. Нулевой код соответствует отсутствию запроса. Большее значение кода соответствует более высокому приоритету запроса. При равных значениях кодов запросов больший приоритет имеет ВЯ 61, …, 6N с меньшим порядковым номером.

Вычислительные ядра 61, …, 6N должны иметь одинаковый интерфейс с остальными блоками модуля, т.е. одинаковую разрядность шин 15, 30 и 33, но могут иметь некоторые отличия во внутренней структуре. Это отмечено на фиг. 1 номерами "1"…"N", которые передаются в качестве параметров на ВЯ и могут учитываться при синтезе ВЯ.

На входы ВЯ 61, …, 6N с интерфейсного блока 1 поступают сигнал сброс 13 и одинаковые для всех ВЯ 61, …, 6N параметры по шине 15. От арбитра заданий 5 на ВЯ 61, …, 6N приходят шины управления записью 311, …, 31N, а с блока памяти данных заданий 4 по шине считывания 30 данные заданий для записи. От арбитра результатов 9 на ВЯ 61, …, 6N поступают сигналы чтения результатов 371, …, 37N. С выходов ВЯ 61, …, 6N на блок мультиплексоров результатов 8 поступают шины результатов ВЯ 331, …, 33N, сигналы окончания считывания пакетов результатов 341, …, 34N и сигналы окончания заданий 351, …, 35N. Сигналы по шинам 351, …, 35N также поступают на входы чтения соответствующих блоков памяти номеров заданий 71, …, 7N.

Каждое ВЯ 61, …, 6N состоит из входной буферной памяти 6-1, операционного блока 6-2, выходной буферной памяти 6-3 и блока управления 6-4.

Входная буферная память 6-1 включает память параметров и память данных. Параметры загружаются перед началом обработки массива заданий и не изменяются в течение обработки этого массива заданий, а данные меняются от задания к заданию. Для совмещения загрузки данных задания в память и обработки ранее загруженных данных заданий память данных состоит из нескольких одинаковых блоков. В память 6-1 ВЯ записываются данные с шины 30 под управлением сигналов соответствующей шины 311, …, 31N. Чтение из памяти 6-1 в операционный блок 6-2 осуществляется по интерфейсу, выбираемому разработчиком ВЯ. Управление режимами записи и считывания заданий из блока памяти 6-1 для обработки в операционном блоке 6-2 осуществляется блоком управления 6-4 соответствующего ВЯ.

Операционный блок 6-2 ВЯ 61, …, 6N приводится в начальное состояние сигналом сброса 13, запускается для выполнения очередного задания блоком управления 6-4, записывает результаты выполнения задания и признак окончания обработки задания из-за переполнения выходного буфера в выходную буферную память 6-3, формирует и передает на блок управления 6-4 сигнал окончания выполнения очередного задания и признак переполнения выходного буфера. Если в результате обработки очередного задания операционным блоком 6-2 достигнуто переполнение выходной буферной памяти 6-3 и не доведена до конца обработка задания, то операционный блок запоминает точку останова при переполнении и, при следующем старте от блока управления 6-4, начинает обработку оставшейся части задания именно с этой точки останова, а блок управления 6-4 в этом случае не переключает на вход операционного блока 6-2 следующий блок входной памяти 6-1, а оставляет подключенный ранее блок и запускает операционный блок 6-2 на обработку сразу при наличии свободного блока выходной памяти 6-3.

Выходная буферная память 6-3 также состоит из нескольких одинаковых блоков для уменьшения простоев операционного блока 6-2 во время ожидания записи и записи во входную память 6-1 или ожидания чтения и чтения из выходной памяти 6-3. Номера блоков для записи результатов от операционного блока 6-2 и чтения результатов из ВЯ выбираются блоком управления 6-4. Запись результатов в выходную память 6-3 от операционного блока 6-2 осуществляется по интерфейсу, выбираемому разработчиком ВЯ. При выборе блоком управления 6-4 очередного блока памяти 6-3 на чтение на блок управления от выбранного на чтение блока памяти поступают признак отсутствия результатов и сигнал окончания чтения результатов с данного блока. Чтение результатов с выхода памяти 6-3 происходит по соответствующему сигналу 371, …, 37N. Чтение происходит в общем случае с некоторой конвейерной задержкой.

Считываемые из вычислительных ядер результаты выдаются на соответствующую шину 331, …, 33N. Эти результаты сопровождаются признаком достоверности результата 33' (Valid). Последнее слово считываемого результата сопровождается сигналом по соответствующему выходу 341, …, 34N, а если это одновременно и окончание обработки задания (не было записано признака переполнения при записи результатов от операционного блока), то выдается и сигнал по соответствующему выходу 351, …, 35N.

В случае отсутствия результатов в задании предлагаемым модулем вычислительной среды поддерживаются два различных режима работы ВЯ. В первом режиме блок управления 6-4, при выборе на чтение блока выходной памяти 6-3 с нулевым числом слов результатов, не выдает запроса на чтение по соответствующей шине 201, …, 20N, а соответствующий блок выходной памяти 6-3, после его выбора на чтение, сразу выдает соответствующий сигнал окончания задания 351, …, 35N, после чего блок управления сразу выбирает следующий блок памяти результатов 6-3 на чтение или ждет загрузки результатов в данный блок, если выходная память 6-3 имеет только один блок. Во втором режиме работы ВЯ, после выбора на чтение блока памяти 6-3 с нулевым числом результатов, блок управления 6-4 выдает соответствующий запрос на чтение 201, …, 20N, как и при ненулевом числе результатов, а блок памяти 6-3 ожидает прихода соответствующего сигнала чтения 371, …, 37N и по его приходу выдает на блок управления 6-4 сигнал окончания чтения, а на блок мультиплексоров результатов 8 по выходам соответствующие сигналы окончания считывания пакетов 341, …, 34N и окончания заданий 351, …, 35N. При этом признак достоверности результата по шине 331, …, 33N не выдается. В первом режиме при отсутствии результатов номер задания просто выталкивается из памяти номеров заданий 71, …, 7N, и время на запись заголовков пустых результатов в выходную память и их считывание не тратится, а во втором режиме номера «безрезультативных» заданий явно указываются в заголовках результатов. Режим работы ВЯ 61, …, 6N при отсутствии результатов выбирается разработчиком ВЯ.

Блок управления 6-4 соответствующего ВЯ 61, …, 6N принимает сигналы сброса 13, окончания записи исполняемого задания во входную память 31'1, …, 31'N, окончания обработки от операционного блока 6-2 с признаком переполнения, нулевого количества слов результатов в выбранном для чтения блоке выходной памяти 6-3, окончания считывания результатов с выбранного для чтения блока выходной памяти. Блок управления 6-4 выбирает номера блоков входной 6-1 и выходной памяти 6-3 для записи и чтения, формирует сигнал запуска операционного блока 6-2 и коды запросов от ядра на запись задания и чтение результатов. Логика формирования запросов на запись и чтение определяется разработчиком ВЯ. Коду запроса присваивается наибольшее значение, если именно выполнение запрашиваемой операции записи или чтения задерживает очередной запуск операционного блока, если для запуска операционного блока кроме выполнения запрашиваемой операции, например записи, необходимо еще и выполнение также операции чтения, то приоритет запроса устанавливается меньше, а если выполнение операции возможно, но операционный блок работает, то приоритет - минимальный. В случае невозможности выполнения данной операции должен формироваться нулевой код запроса.

Блоки памяти номеров заданий 71, …, 7N являются блоками памяти типа FIFO. На входы сброса этих блоков памяти поступают сигналы сброса 13, на входы записи поступают сигналы окончания записи исполняемых заданий 31'1, …, 31'N, на входы чтения, используемые как сигналы смены считываемого номера задания, - сигналы окончания заданий 351, …, 35N, на входы данных - шины записываемых номеров заданий 321, …, 32N. С выходов блоков памяти номеров заданий 71, …, 7N номера заданий, к которым относятся считываемые результаты и признаки «Пустой», по соответствующим шинам 361, …, 36N поступают на блок мультиплексоров результатов 8.

На блок мультиплексоров результатов 8 поступает от арбитра результатов 9 по шине 38 код номера выбранного ВЯ 61, …, 6N. В соответствии с данным кодом блок мультиплексоров передает одну из входных шин результатов 331, …, 33N на выходную шину 33, номер задания с одной из входных шин 361, …, 36N на выходную шину 36, один из входных сигналов 341, …, 34N на выход 34, а один из входных сигналов 351, …, 35N на выход 35. Также, в блоке мультиплексоров результатов 8 на основе признаков «Пустой» блоков памяти номеров заданий 71, …, 7N, передаваемых по шинам 361, …, 36N, формируется общий признак «Пустой» всех блоков памяти номеров заданий 21', который по шине 21 передается на интерфейсный блок 1. Общий признак «Пустой» номеров заданий используется УП для определения окончания обработки всего пакета заданий, если вычислительные ядра, при отсутствии результатов выполнения очередного задания, не выдают запрос на чтение, а сразу выдают сигнал окончания задания 35 и номер данного задания отсутствует в заголовках результатов.

На арбитр результатов 9 поступают сигнал сброса 13, код режима чтения результатов по шине 14, запросы вычислительных ядер на чтение по шине 20, сигналы окончания чтения с выбранного арбитром ядра по шине 34, признак достоверности считанного с выбранного ядра кода результата 33' и признаки переполнения блоков выходной памяти результатов 40 и 41. Арбитр результатов 9 формирует сигналы чтения результатов 371, …, 37N в соответствующее вычислительное ядро 61, …, 6N, код номера выбранного вычислительного ядра 38 в блок мультиплексоров результатов 8 и код количества слов в пакете результатов 39 в блок памяти заголовков результатов 10.

Режим работы арбитра результатов 9 определяется кодом управления, поступающим по шине 14. Арбитр результатов 9 может работать в трех различных режимах:

- Чтение результата из соответствующего ВЯ 61, …, 6N, номер которого передается от интерфейсного блока 1 по шине 14, после считывания по шине 20 в интерфейсный блок 1 и анализа запроса на чтение результата от этого ядра.

- Чтение результата последовательно из всех ВЯ 61, …, 6N, с ожиданием наличия запросов на чтение результата по шине 20 от каждого ВЯ перед чтением из него результата. Анализ запросов на чтение результата по шине 20 выполняется автоматически арбитром результатов 9. Данный режим может использоваться при одинаковых временах загрузки, выполнения заданий и считывания результатов для всех ВЯ.

- Чтение результата из соответствующего ВЯ 61, …, 6N, выбранного арбитром результатов 9. При этом арбитр результатов 9 осуществляет автоматический выбор ядра для чтения результата в соответствии с приоритетом запросов на чтение от ВЯ. От каждого ядра поступает двухразрядный код запроса на чтение по соответствующим шинам 201, …, 20N. Нулевой код соответствует отсутствию запроса. Большее значение кода соответствует более высокому приоритету запроса. При равных значениях кодов запросов больший приоритет имеет ВЯ с меньшим порядковым номером.

Блоки памяти заголовков результатов 10 и памяти данных результатов 11 реализуют дисциплину обслуживания FIFO.

Блок памяти заголовков результатов 10 записывает сигналом окончания чтения результатов 34 заголовок результата, состоящий из кодов номера задания 36, количества слов в пакете результатов 39 и признака окончания задания 35. По сигналу чтения 23 от интерфейсного блока 1, из блока памяти 10 считываются заголовки пакетов результатов по шине 25 в интерфейсный блок 1. Также блок памяти 10 выдает для чтения на интерфейс УП код количества пакетов результатов в выходной памяти по шине 21 в интерфейсный блок 1 и признак переполнения памяти заголовков результатов 41 в арбитр результатов 9.

Блок памяти данных результатов 11 записывает сигналом достоверности результата 33' код данных результата, приходящий по шине 33. С данного блока памяти 11 по сигналу чтения 22, приходящему от интерфейсного блока 1, считываются по шине 24 пакеты данных результатов. Также блок памяти 11 выдает признак переполнения памяти результатов 40 в арбитр результатов 9. Блок памяти 11 также преобразует разрядность выходной шины результатов ВЯ 33 в разрядность шины потоковой операции чтения 24. При разрядности выходной шины результатов ВЯ 33 меньшей, чем разрядность шины потоковой операции чтения 24, преобразование разрядности происходит на входе блока памяти 11, а при разрядности шины 33 большей, чем разрядность шины 24, преобразование разрядности происходит на выходе блока памяти 11.

Предлагаемый вычислительный модуль работает следующим образом.

Управляющий процессор (УП) обычно работает с несколькими предлагаемыми ВМ одновременно. На всех модулях и в каждом модуле могут использоваться одинаковые ВЯ 61, …, 6N, предназначенные для выполнения однотипных заданий, или различные ВЯ 61, …, 6N, которые могут отличаться и предназначаться для выполнения принци